# Technical Support Center: Quinacridone-Based Organic Electronic Devices

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Quinacridone

Cat. No.: B094251

[Get Quote](#)

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in reducing defects in **quinacridone**-based organic electronic devices.

## Frequently Asked Questions (FAQs) & Troubleshooting

This section addresses common issues encountered during the fabrication and testing of **quinacridone**-based devices.

### 1. Device Performance Issues

**Q1:** My organic field-effect transistor (OFET) shows low charge carrier mobility. What are the potential causes and how can I improve it?

**A1:** Low charge carrier mobility in **quinacridone**-based OFETs is often linked to the morphology and crystal structure of the active layer. Here are the primary factors and troubleshooting steps:

- Poor Crystalline Quality: The arrangement of **quinacridone** molecules is crucial for efficient charge transport. Defects in the crystal lattice can act as charge traps.

- Solution: Optimize the deposition parameters. If using vacuum deposition, adjust the substrate temperature and deposition rate. For solution-based methods, control the

solvent evaporation rate and consider post-deposition annealing.

- **Unfavorable Polymorph:** **Quinacridone** exists in different crystalline forms (polymorphs), each with distinct electronic properties. The formation of a less favorable polymorph can lead to lower mobility.

- **Solution:** The choice of solvent and substrate can influence polymorph formation. Experiment with different solvents or surface treatments on your substrate to encourage the growth of a high-mobility polymorph. Solvent vapor annealing after film deposition can also induce phase transitions.

- **Interface Traps:** Defects at the interface between the **quinacridone** semiconductor and the dielectric layer can trap charge carriers, reducing mobility.

- **Solution:** Ensure pristine substrate and dielectric surfaces. Employ rigorous substrate cleaning protocols. Consider treating the dielectric surface with a self-assembled monolayer (SAM) like octadecyltrimethoxysilane (ODTMS) to improve the interface quality.

**Q2:** The on/off ratio of my OFET is low. What steps can I take to increase it?

**A2:** A low on/off ratio is typically due to a high off-state current (leakage current). Here's how to address this:

- **Gate Leakage:** A significant current may be flowing through the gate dielectric.

- **Solution:** Ensure the integrity of your dielectric layer. If you are depositing your own dielectric, optimize the deposition process to minimize pinholes and defects. Using a high-quality dielectric material is crucial.

- **Semiconductor Bulk Conductivity:** If the **quinacridone** layer is too thick or has a high density of impurities, it can lead to a higher off-state current.

- **Solution:** Optimize the thickness of the semiconductor layer. For vacuum deposition, reduce the deposition time or rate. For solution processing, adjust the concentration of the **quinacridone** solution.

- Unpatterned Active Layer: In bottom-gate device architectures, an unpatterned semiconductor layer can create a leakage path between the source and drain electrodes that is not controlled by the gate.

- Solution: Pattern the **quinacridone** layer to confine the current flow to the channel region. This can be done through shadow masking during deposition or by post-deposition etching.

Q3: I'm observing a high leakage current in my device. How can I diagnose and fix this?

A3: High leakage current can originate from several sources. Here's a systematic approach to troubleshooting:

- Isolate the Leakage Path:

- Gate Leakage: Measure the current flowing into the gate electrode. If this is high, the issue is likely with the gate dielectric.

- Source-Drain Leakage: If the gate current is low but the off-state source-drain current is high, the leakage is through the semiconductor layer or along interfaces.

- Common Causes and Solutions:

- Poor Dielectric Quality: As mentioned, a faulty dielectric is a common cause of high gate leakage.

- Substrate Contamination: Residues on the substrate can create conductive pathways. Implement a thorough substrate cleaning procedure.

- Device Architecture: For devices on common gate substrates like Si/SiO<sub>2</sub>, the entire substrate can contribute to leakage if the semiconductor is not patterned.<sup>[1]</sup> Confining the active layer to the channel area is an effective solution.<sup>[1]</sup>

## 2. Fabrication and Material-Related Issues

Q4: I'm having trouble forming a uniform **quinacridone** thin film using solution-based methods. What should I do?

A4: Achieving uniform films from solution can be challenging due to the low solubility of **quinacridone** in many common organic solvents.

- Solvent Choice: Dimethyl sulfoxide (DMSO) is a solvent that can be used for **quinacridone**, but its high boiling point requires careful control of the drying process.

- Solution: To avoid the formation of spots or a "shrunken" film when using DMSO, consider a slower evaporation process. This can be achieved by heating the substrate at a moderate temperature (e.g., 50°C) in a convection oven or by creating a solvent atmosphere over the film during drying.[2]

- Solvent Additives: Small amounts of a secondary solvent can influence the solubility and film formation dynamics.

- Solution: Experiment with solvent additives to improve film morphology. However, be aware that this can also affect the resulting crystal structure.

- Deposition Technique: The choice of deposition method plays a significant role.

- Solution: Techniques like solution shearing can produce highly crystalline and aligned films.[3] Optimizing the shearing speed and substrate temperature is key to achieving the desired morphology.[3]

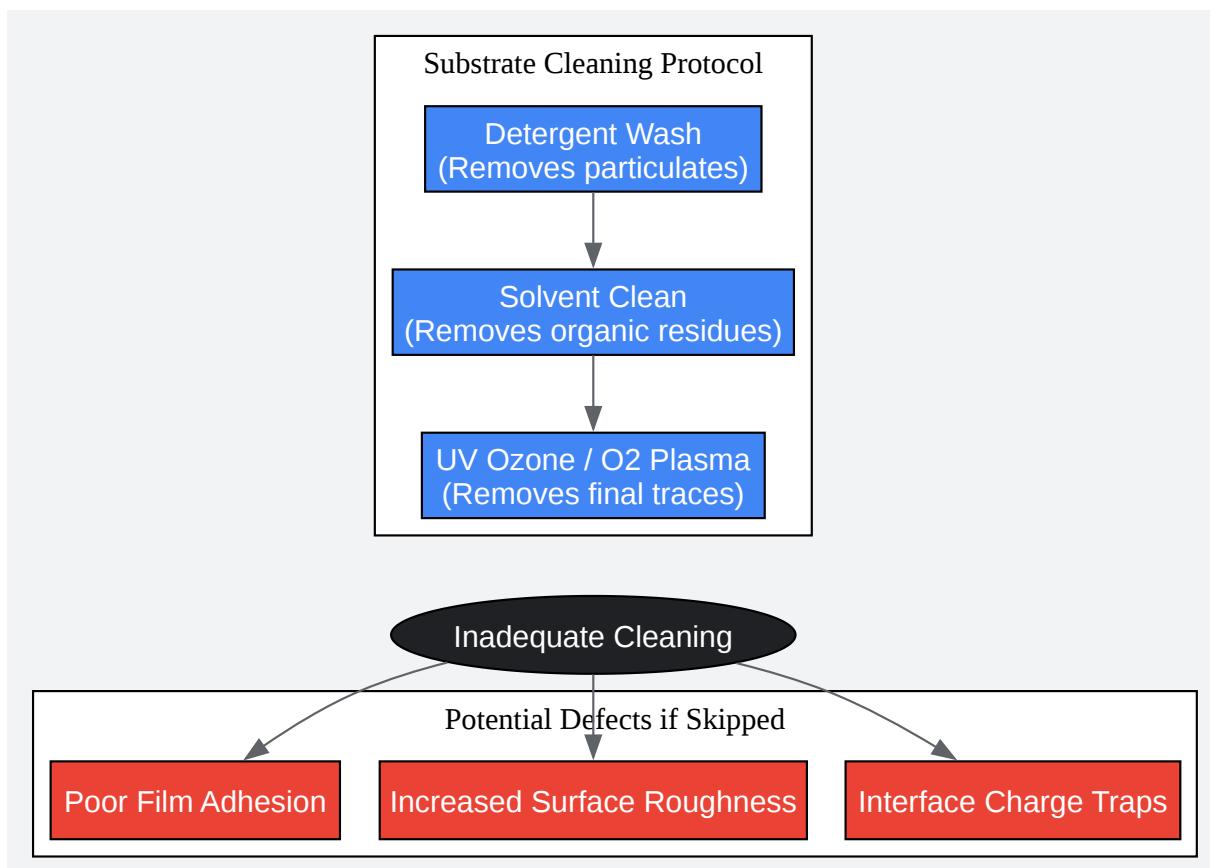

Q5: What is the importance of substrate cleaning, and what is a reliable protocol?

A5: Substrate cleaning is a critical step, as contaminants can act as nucleation sites for defects, increase surface roughness, and introduce charge traps at the semiconductor-dielectric interface.[4]

- Standard Cleaning Protocol: A widely used and effective protocol involves a sequence of sonication in different solvents to remove organic and particulate contaminants.

- Detergent Wash: Sonicate substrates in a heated solution of deionized water and a detergent like Hellmanex III for 5-15 minutes.

- DI Water Rinse: Thoroughly rinse the substrates with hot deionized water.

- Solvent Clean: Sonicate in isopropyl alcohol (IPA) or acetone for 5-10 minutes.

- Final Rinse: Rinse again with hot deionized water.

- Drying: Dry the substrates using a nitrogen gun.

- Surface Treatment: Immediately before depositing the organic layer, treat the substrate surface with UV ozone or an oxygen plasma to remove any remaining organic residues and improve surface wettability.[5][6]

## Quantitative Data Summary

The performance of **quinacridone**-based OFETs is highly dependent on the fabrication conditions and the specific derivatives used. The following tables summarize some reported performance metrics.

Table 1: Performance of Vacuum-Deposited **Quinacridone** OFETs

| Substrate Treatment      | Substrate Temp. (°C) | Polarity | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio          | Threshold Voltage (V) |

|--------------------------|----------------------|----------|--------------------------------|-----------------------|-----------------------|

| Bare Si/SiO <sub>2</sub> | 25                   | p-type   | 2.1 × 10 <sup>-4</sup>         | 1.8 × 10 <sup>5</sup> | -30.9                 |

| ODTMS-treated            | 25                   | p-type   | 1.3 × 10 <sup>-3</sup>         | 1.1 × 10 <sup>6</sup> | -23.1                 |

| ODTMS-treated            | 60                   | p-type   | 1.5 × 10 <sup>-3</sup>         | 5.3 × 10 <sup>5</sup> | -25.2                 |

| ODTMS-treated            | 100                  | p-type   | 1.4 × 10 <sup>-3</sup>         | 1.2 × 10 <sup>6</sup> | -20.5                 |

Data sourced from Tokyo Chemical Industry Co., Ltd. for sublimed **quinacridone** [Q0083] on Si/SiO<sub>2</sub> (200 nm) substrates.

Table 2: Performance of OFETs based on N,N'-Substituted **Quinacridones**

| Quinacridone Derivative   | Dielectric                  | Hole Mobility ( $\mu$ h) ( $\text{cm}^2/\text{Vs}$ ) | Electron Mobility ( $\mu$ e) ( $\text{cm}^2/\text{Vs}$ ) |

|---------------------------|-----------------------------|------------------------------------------------------|----------------------------------------------------------|

| N,N'-dimethylquinacridone | $\text{AlO}_x + \text{TTC}$ | $8 \times 10^{-3}$                                   | $3 \times 10^{-4}$                                       |

| N,N'-dibutylquinacridone  | $\text{AlO}_x + \text{TTC}$ | $2 \times 10^{-4}$                                   | -                                                        |

Data extracted from a study on N,N'-substituted **quinacridones**. The substitution disrupts intermolecular hydrogen bonding, which can affect charge transport properties compared to pristine **quinacridone**.<sup>[7]</sup>

## Experimental Protocols

This section provides detailed methodologies for key experimental processes.

### Protocol 1: Substrate Cleaning for **Quinacridone** Device Fabrication

- Initial Cleaning: Gently scrub the substrate surfaces (e.g., Si/SiO<sub>2</sub> or glass) with a lint-free wipe soaked in a detergent solution (e.g., Hellmanex III).

- Sonication: Place the substrates in a substrate holder and sonicate sequentially in the following solutions for 15 minutes each:

- Detergent solution in deionized (DI) water

- DI water

- Acetone

- Isopropyl alcohol (IPA)

- Rinsing: After each sonication step, thoroughly rinse the substrates with DI water.

- Drying: Dry the substrates with a stream of high-purity nitrogen gas.

- Surface Activation (Optional but Recommended): Immediately prior to use, treat the substrates with UV ozone for 10-15 minutes or in an oxygen plasma ash to remove residual organic contaminants and render the surface hydrophilic.[5][6]

#### Protocol 2: Fabrication of a Bottom-Gate, Top-Contact **Quinacridone** OFET by Vacuum Deposition

- Substrate Preparation: Use a heavily doped silicon wafer with a thermally grown silicon dioxide layer (e.g., 200-300 nm) as the gate electrode and gate dielectric, respectively. Clean the substrate using Protocol 1.

- Dielectric Surface Treatment (Optional): To improve the dielectric-semiconductor interface, a self-assembled monolayer (SAM) can be applied. For an ODTMS layer, expose the cleaned substrate to ODTMS vapor in a vacuum desiccator for several hours.

- **Quinacridone** Deposition:

- Place the prepared substrates in a high-vacuum thermal evaporator.

- Load high-purity (sublimed) **quinacridone** powder into a crucible.

- Evacuate the chamber to a pressure below  $10^{-6}$  Torr.

- Heat the substrate to the desired temperature (e.g., 25-100°C).

- Slowly heat the crucible to sublimate the **quinacridone**, depositing a thin film (e.g., 30-50 nm) on the substrates. The deposition rate should be kept low and constant (e.g., 0.1-0.5 Å/s) to promote ordered film growth.

- Source-Drain Electrode Deposition:

- Without breaking vacuum, or using a shadow mask in a separate deposition step, deposit the source and drain electrodes (e.g., 50 nm of gold with a thin adhesion layer of chromium or titanium) on top of the **quinacridone** film. This defines the channel length and width.

- Device Characterization: Transfer the completed devices to a probe station for electrical characterization in an inert atmosphere (e.g., nitrogen or argon) to prevent degradation from ambient air.

## Visualizations: Workflows and Logical Relationships

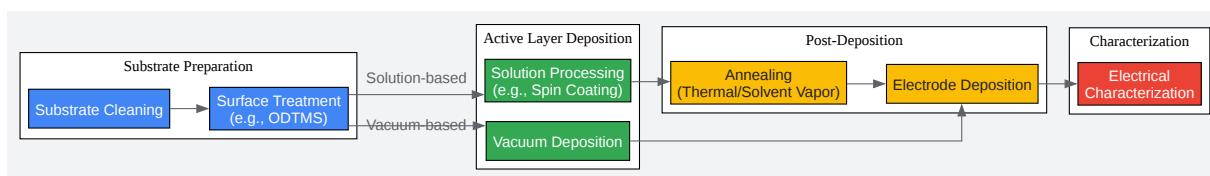

Diagram 1: General Workflow for Fabrication of a **Quinacridone**-Based OFET

[Click to download full resolution via product page](#)

Caption: A generalized workflow for the fabrication of **quinacridone**-based organic field-effect transistors.

Diagram 2: Troubleshooting Logic for Low Device Mobility

[Click to download full resolution via product page](#)

Caption: A decision-making flowchart for troubleshooting low mobility in **quinacridone** devices.

Diagram 3: Relationship between Substrate Cleaning and Device Defects

[Click to download full resolution via product page](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Interfacial effects on solution-sheared thin-film transistors - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 2. Charge carrier traps in organic semiconductors: a review on the underlying physics and impact on electronic devices - Journal of Materials Chemistry C (RSC Publishing)

[pubs.rsc.org]

- 3. researchgate.net [researchgate.net]

- 4. oam-rc.inoe.ro [oam-rc.inoe.ro]

- 5. ossila.com [ossila.com]

- 6. cleanroom.byu.edu [cleanroom.byu.edu]

- 7. N , N '-Substituted quinacridones for organic electronic device applications - Materials Advances (RSC Publishing) DOI:10.1039/D2MA01010K [pubs.rsc.org]

- To cite this document: BenchChem. [Technical Support Center: Quinacridone-Based Organic Electronic Devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b094251#reducing-defects-in-quinacridone-based-organic-electronic-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)