# As<sub>4</sub>S<sub>4</sub> in Electronics: A Technical Support Center for Researchers

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Tetraarsenic tetrasulfide*

Cat. No.: B089339

[Get Quote](#)

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with As<sub>4</sub>S<sub>4</sub> (realgar, arsenic sulfide) in electronic device applications. The information is presented in a question-and-answer format to directly address common issues encountered during experimentation.

## Frequently Asked Questions (FAQs) & Troubleshooting

**Q1:** My solution-processed As<sub>4</sub>S<sub>4</sub> film has poor surface morphology (e.g., pinholes, cracks, or is not uniform). What are the likely causes and solutions?

**A1:** Poor film quality in solution-processed As<sub>4</sub>S<sub>4</sub> is a common issue stemming from several factors. Inconsistent deposition temperatures can lead to voids and pinholes by hindering the mobility of atoms as the film forms.<sup>[1]</sup> Contamination from impurities in the precursor materials or residual gases in the processing environment can also introduce particles that disrupt film integrity.<sup>[1]</sup>

### Troubleshooting Steps:

- **Substrate Cleaning:** Ensure the substrate is meticulously cleaned to remove any organic residues, dust, or other contaminants. Standard procedures often involve sequential ultrasonication in acetone, isopropanol, and deionized water.

- **Solution Preparation:** Ensure the As<sub>4</sub>S<sub>4</sub> precursor is fully dissolved in the chosen solvent (e.g., n-propylamine or ethylenediamine).<sup>[2]</sup> Filtering the solution through a sub-micron filter before deposition can remove undissolved particles.

- **Spin Coating Parameters:** Optimize the spin speed and duration. A higher spin speed generally results in a thinner, more uniform film, but too high a speed can cause the film to de-wet or become too thin.

- **Annealing/Drying:** Control the drying and annealing process carefully. A slow, controlled ramp-up in temperature can prevent solvent "boil-off" which can create pinholes. An optimal annealing temperature helps in structural polymerization and removal of organic residues.<sup>[2]</sup>

- **Environmental Control:** Perform the deposition and annealing in a controlled atmosphere (e.g., a nitrogen-filled glovebox) to minimize exposure to oxygen and moisture, which can lead to the formation of arsenic oxides.

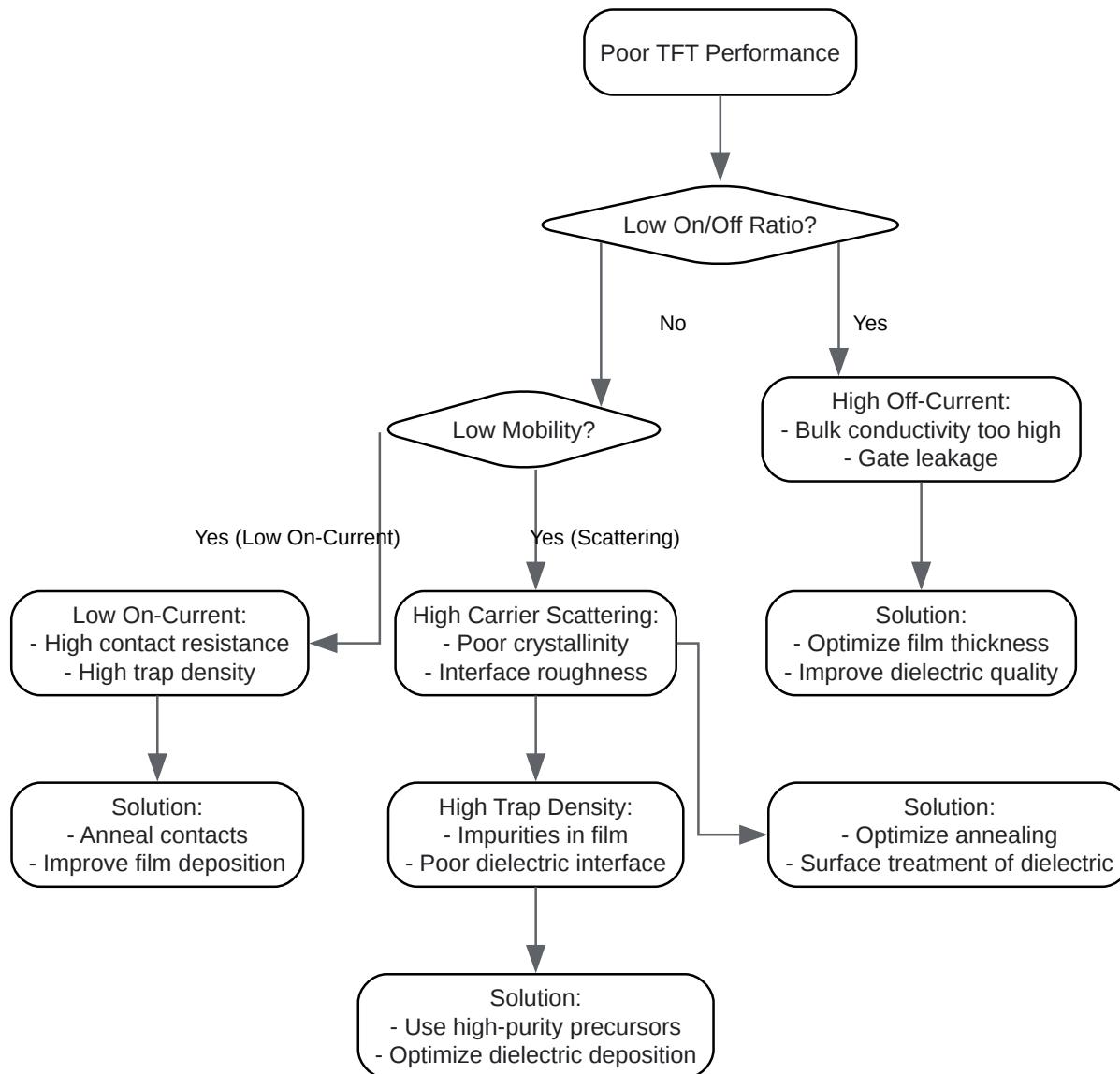

**Q2:** The performance of my As<sub>4</sub>S<sub>4</sub>-based thin-film transistor (TFT) is poor. What are the key performance metrics and what could be causing issues like low mobility or a low on/off ratio?

**A2:** Key performance metrics for a TFT are its field-effect mobility ( $\mu$ ), which indicates how quickly charge carriers move, and the on/off current ratio, which signifies the device's ability to switch between conducting and non-conducting states.<sup>[3]</sup> For arsenic sulfide-based TFTs, reported p-type characteristics include a field-effect mobility of around 0.08 cm<sup>2</sup>/V·s and an on/off ratio of approximately 10<sup>4</sup>.

#### Common Causes for Poor Performance:

- **High Defect Density:** Defects within the As<sub>4</sub>S<sub>4</sub> film or at the interface between the semiconductor and the dielectric layer can act as traps for charge carriers, reducing mobility. These defects can arise from impurities, structural disorder, or dangling bonds.

- **Poor Interface Quality:** A rough or contaminated interface between the As<sub>4</sub>S<sub>4</sub> and the gate dielectric can scatter charge carriers and introduce trap states, severely degrading performance.

- **Contact Resistance:** High resistance at the source and drain contacts can limit the current flow and lead to an underestimation of the device's true performance.

- Film Thickness: The thickness of the As4S4 layer can influence its electrical properties. An optimal thickness is required for effective channel modulation by the gate voltage.

Troubleshooting Flowchart:

[Click to download full resolution via product page](#)

Caption: Troubleshooting logic for poor As4S4 TFT performance.

Q3: My As4S4 device performance degrades over time, especially when exposed to light. What is happening and how can I mitigate this?

A3: Arsenic sulfide materials, including As<sub>4</sub>S<sub>4</sub> (realgar), are known to undergo photo-induced transformations. Exposure to light can cause a phase change from the crystalline realgar ( $\alpha$ -As<sub>4</sub>S<sub>4</sub>) to the amorphous pararealgar, which has different structural and electronic properties. This transformation can alter the conductivity and trap density, leading to device instability. Furthermore, light exposure in the presence of oxygen and moisture can lead to the formation of arsenic oxides and elemental selenium or sulfur on the film surface, which degrades the electronic properties.

#### Mitigation Strategies:

- **Encapsulation:** Depositing a passivation layer (e.g., a thin layer of Al<sub>2</sub>O<sub>3</sub> or SiN<sub>x</sub>) on top of the As<sub>4</sub>S<sub>4</sub> film can protect it from moisture and oxygen in the ambient environment.

- **UV Filtering:** If the application allows, using a UV filter can reduce the energy of incident photons, potentially slowing down the degradation process.

- **Controlled Environment:** Operating and storing the devices in an inert atmosphere (e.g., nitrogen or argon) can prevent oxidation.

## Data Presentation

The following tables summarize typical quantitative data for arsenic sulfide-based materials and provide a comparison with other common thin-film semiconductors.

Table 1: Reported Electronic Properties of Solution-Processed Arsenic Sulfide TFTs

| Parameter                            | Value                     | Source      |

|--------------------------------------|---------------------------|-------------|

| Field-Effect Mobility ( $\mu$ )      | 0.08 cm <sup>2</sup> /V·s | IEEE Xplore |

| On/Off Current Ratio                 | $10^4$                    | IEEE Xplore |

| Threshold Voltage (V <sub>th</sub> ) | -1.2 V                    | IEEE Xplore |

| Conduction Type                      | p-type                    | IEEE Xplore |

Table 2: Comparison of Thin-Film Transistor Performance Metrics

| Material System                                      | Typical Mobility<br>(cm <sup>2</sup> /V·s) | Typical On/Off<br>Ratio           | Deposition Method      |

|------------------------------------------------------|--------------------------------------------|-----------------------------------|------------------------|

| Arsenic Sulfide<br>(As <sub>x</sub> S <sub>y</sub> ) | 0.08                                       | 10 <sup>4</sup>                   | Solution-Processed     |

| Amorphous Silicon (a-Si:H)                           | ~1                                         | >10 <sup>6</sup>                  | PECVD                  |

| Copper Tin Sulfide<br>(CTS)                          | ~2.43                                      | >10 <sup>5</sup>                  | Solution-Processed     |

| Molybdenum Disulfide<br>(MoS <sub>2</sub> )          | 1-200                                      | 10 <sup>6</sup> - 10 <sup>8</sup> | CVD / Exfoliation      |

| Organic Semiconductors (e.g., Pentacene)             | 0.1 - 1                                    | 10 <sup>5</sup> - 10 <sup>7</sup> | Evaporation / Solution |

## Experimental Protocols

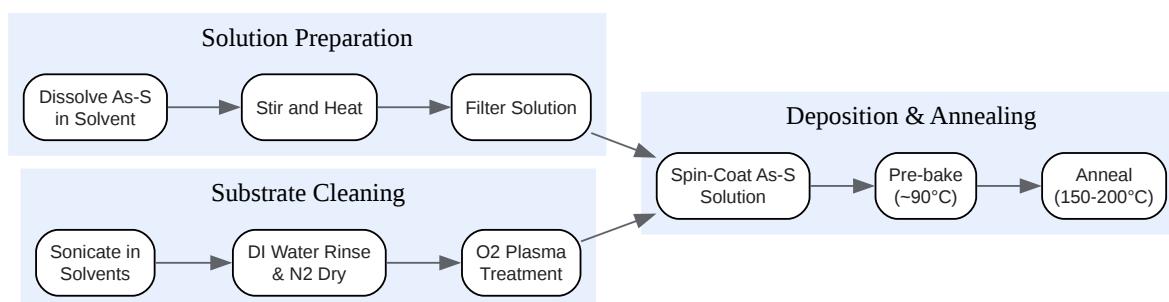

### Protocol 1: Solution-Based Synthesis and Deposition of Arsenic Sulfide Thin Films

This protocol describes a general method for preparing arsenic sulfide thin films via spin-coating.

1. Solution Preparation: a. Dissolve arsenic sulfide powder (e.g., As<sub>2</sub>S<sub>3</sub> as a common precursor) in a suitable solvent such as n-propylamine or ethylenediamine to a desired concentration (e.g., 50-100 mg/mL).<sup>[2]</sup> b. Stir the mixture in a sealed vial on a hotplate at a slightly elevated temperature (e.g., 40-60 °C) for several hours until the powder is fully dissolved. c. Before use, cool the solution to room temperature and filter it through a 0.2 µm PTFE syringe filter.

2. Substrate Preparation: a. Prepare substrates (e.g., heavily doped silicon wafers with a thermal oxide layer). b. Clean the substrates by sonicating for 15 minutes each in acetone, then isopropanol. c. Rinse thoroughly with deionized water and dry with a nitrogen gun. d. Treat the substrates with oxygen plasma for 5 minutes to create a hydrophilic surface for better film adhesion.

3. Film Deposition (Spin-Coating): a. Transfer the prepared substrates and the arsenic sulfide solution into a nitrogen-filled glovebox. b. Dispense a few drops of the solution onto the center of the substrate. c. Spin-coat at a speed of 1000-4000 rpm for 30-60 seconds to achieve the desired thickness. d. Transfer the coated substrate to a hotplate within the glovebox.

4. Annealing: a. Pre-bake the film at a low temperature (e.g., 90 °C) for 10-20 minutes to slowly evaporate the solvent. b. Anneal the film at a higher temperature (e.g., 150-200 °C) for 30-60 minutes to densify the film and improve its structural properties. c. Allow the film to cool down slowly to room temperature before further processing.

Experimental Workflow Diagram:

[Click to download full resolution via product page](#)

Caption: Workflow for solution-based deposition of arsenic sulfide films.

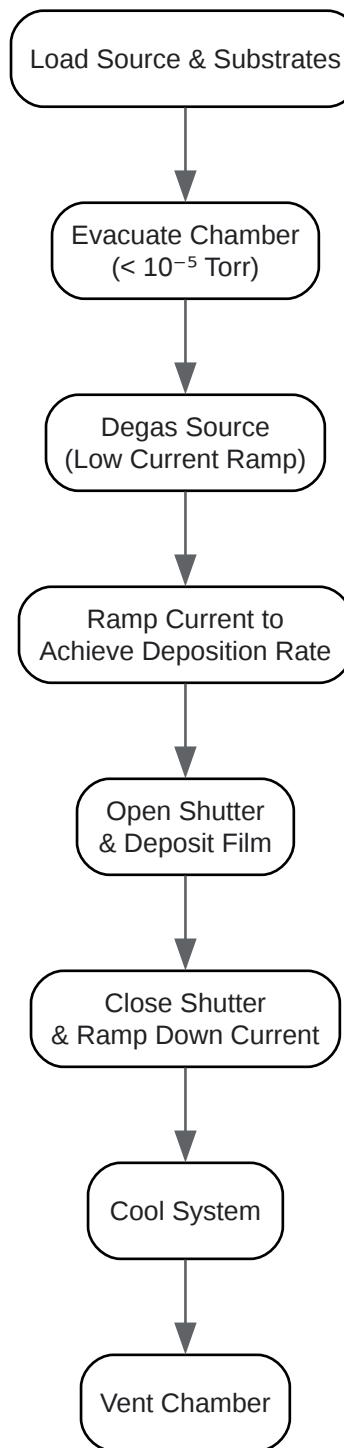

#### Protocol 2: Thermal Evaporation of As<sub>4</sub>S<sub>4</sub> Thin Films

This protocol outlines the steps for depositing As<sub>4</sub>S<sub>4</sub> thin films using a thermal evaporation system.

1. System Preparation: a. Load high-purity As<sub>4</sub>S<sub>4</sub> powder or chunks into a suitable evaporation source, such as a baffled tungsten or molybdenum boat. b. Mount the cleaned substrates onto the substrate holder. c. Evacuate the chamber to a base pressure of at least 10<sup>-6</sup> Torr to minimize contamination.

2. Deposition Parameters: a. Deposition Rate: A typical rate for chalcogenide glasses is between 1-10 Å/s. A slower rate can result in a denser, more uniform film. b. Substrate Temperature: The substrate can be kept at room temperature or heated to a moderate temperature (e.g., 100-150 °C) to control film properties. c. Source Current: Slowly ramp up the current to the evaporation boat to degas the source material. Once degassed, increase the current until the desired deposition rate is achieved, as monitored by a quartz crystal microbalance.

3. Deposition Process: a. Open the shutter between the source and the substrate to begin deposition. b. Maintain a stable deposition rate throughout the process. c. Close the shutter once the desired film thickness is reached. d. Slowly ramp down the current to the source and allow the system to cool before venting.

Thermal Evaporation Process Diagram:

[Click to download full resolution via product page](#)

Caption: Process flow for thermal evaporation of As<sub>4</sub>S<sub>4</sub> thin films.

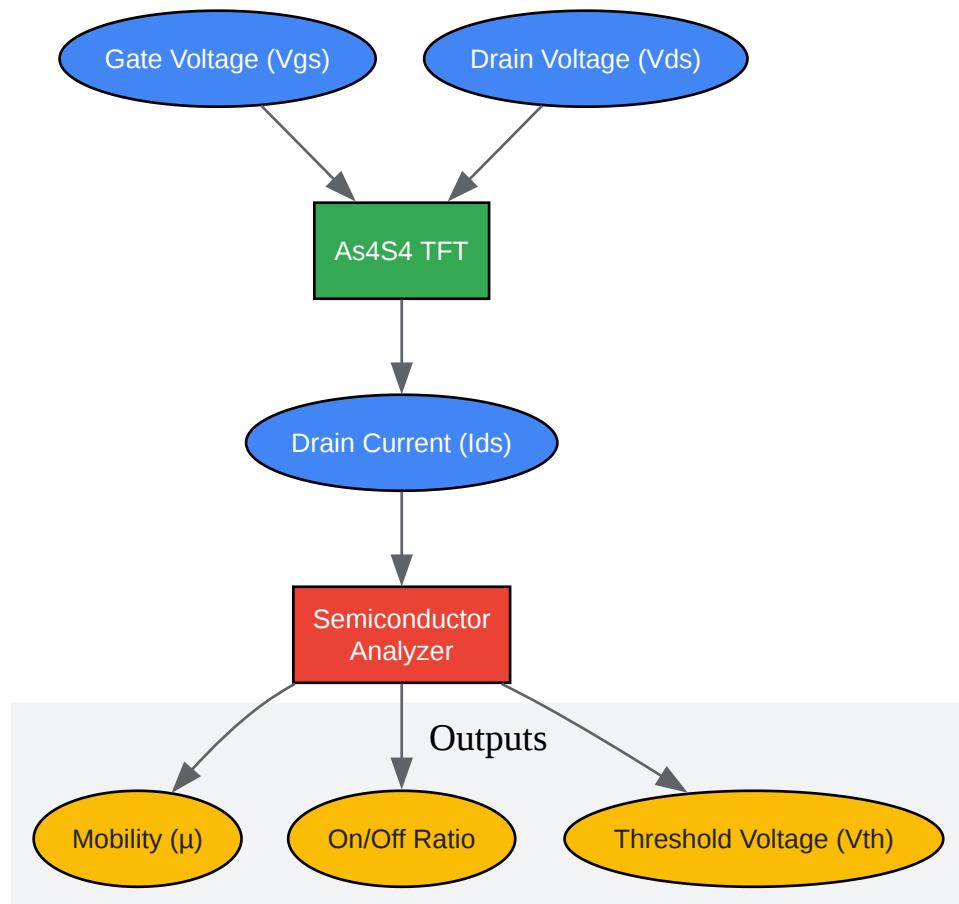

Protocol 3: Thin-Film Transistor (TFT) Characterization

This protocol describes the electrical characterization of a fabricated As4S4 TFT.

1. Equipment: a. Semiconductor parameter analyzer (e.g., Keysight B1500A or similar). b. Probe station with micro-manipulators. c. Controlled measurement environment (dark box, preferably under vacuum or inert gas).

2. Measurement Procedure: a. Output Characteristics ( $I_{ds}$  vs.  $V_{ds}$ ): i. Connect probes to the source, drain, and gate terminals. ii. Set the gate voltage ( $V_{gs}$ ) to a starting value (e.g., 0 V). iii. Sweep the drain-source voltage ( $V_{ds}$ ) over the desired range (e.g., 0 V to -40 V for p-type) and measure the drain-source current ( $I_{ds}$ ). iv. Increment  $V_{gs}$  (e.g., in steps of -5 V) and repeat the  $V_{ds}$  sweep. b. Transfer Characteristics ( $I_{ds}$  vs.  $V_{gs}$ ): i. Set  $V_{ds}$  to a constant value in the saturation region (e.g., -40 V). ii. Sweep  $V_{gs}$  over the desired range (e.g., +20 V to -40 V) and measure  $I_{ds}$ . iii. Plot  $I_{ds}$  (on a logarithmic scale) and  $\sqrt{|I_{ds}|}$  (on a linear scale) against  $V_{gs}$ .

3. Parameter Extraction: a. On/Off Ratio: Determined from the logarithmic  $I_{ds}$  vs.  $V_{gs}$  plot as the ratio of the maximum current in the 'on' state to the minimum current in the 'off' state. b. Field-Effect Mobility ( $\mu$ ): Calculated from the slope of the linear region of the  $\sqrt{|I_{ds}|}$  vs.  $V_{gs}$  plot using the standard MOSFET equation for the saturation regime. c. Threshold Voltage ( $V_{th}$ ): Extracted from the x-intercept of the linear fit to the  $\sqrt{|I_{ds}|}$  vs.  $V_{gs}$  plot.

TFT Characterization Signaling Pathway:

[Click to download full resolution via product page](#)

Caption: Signal and data flow for TFT characterization.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Top 5 Thin Film Deposition Challenges and Expert Solutions for High-Yield Processes [xk-sputteringtarget.com]

- 2. researchgate.net [researchgate.net]

- 3. arxiv.org [arxiv.org]

- To cite this document: BenchChem. [As4S4 in Electronics: A Technical Support Center for Researchers]. BenchChem, [2025]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b089339#improving-the-performance-of-as4s4-in-electronic-devices\]](https://www.benchchem.com/product/b089339#improving-the-performance-of-as4s4-in-electronic-devices)

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)