# impact of grain boundaries on charge transport in Perfluoropentacene

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Perfluoropentacene**

Cat. No.: **B8735957**

[Get Quote](#)

## Technical Support Center: Perfluoropentacene Grain Boundary Effects

This technical support center provides troubleshooting guides, frequently asked questions (FAQs), and experimental protocols for researchers studying the impact of grain boundaries on charge transport in **perfluoropentacene** (PFP), an n-type organic semiconductor.<sup>[1]</sup>

## Frequently Asked Questions (FAQs)

**Q1:** What are grain boundaries in a **perfluoropentacene** thin film?

**A1:** **Perfluoropentacene** thin films are often polycrystalline, meaning they are composed of many small single-crystal domains called "grains." A grain boundary is the interface where two or more of these grains with different crystallographic orientations meet. These interfaces disrupt the long-range molecular order of the film.

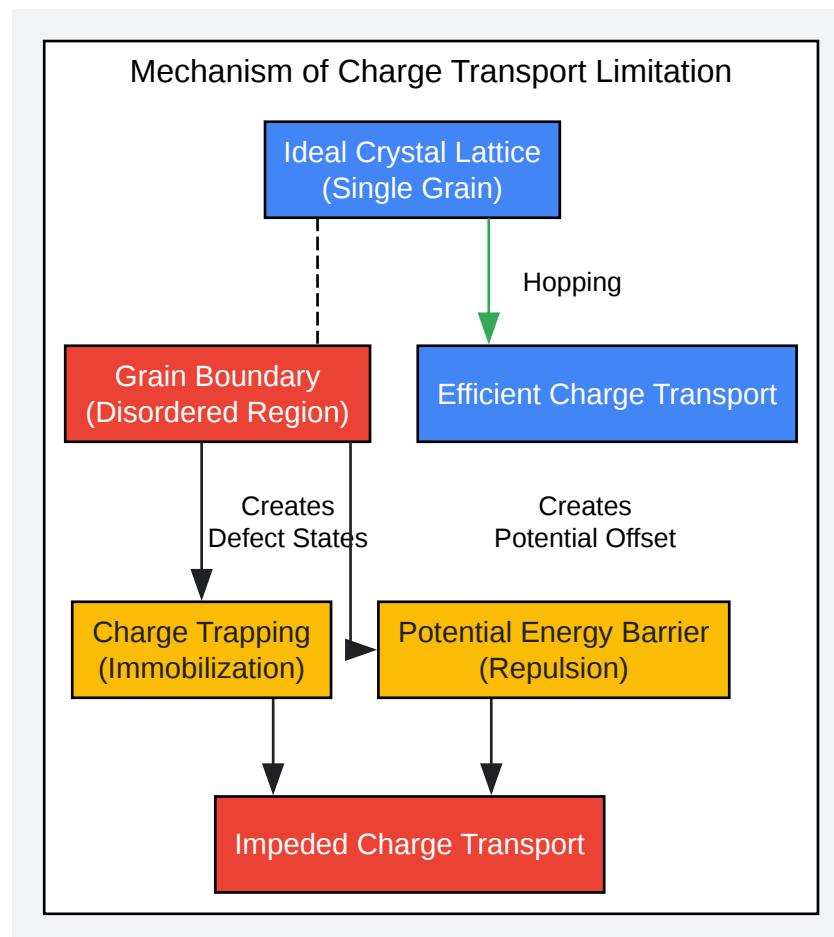

**Q2:** How do grain boundaries fundamentally impact charge transport?

**A2:** Grain boundaries act as significant impediments to charge transport in polycrystalline organic semiconductors.<sup>[2]</sup> They introduce structural disorder and can create localized electronic trap states within the material's bandgap.<sup>[3]</sup> These traps can capture charge carriers (electrons in the case of PFP), immobilizing them and preventing them from contributing to the

current. Furthermore, trapped charges can create an electrostatic potential barrier that repels other carriers, further hindering their movement across the boundary.[2]

Q3: What specific device parameters are affected by grain boundaries?

A3: Grain boundaries can detrimentally affect several key organic field-effect transistor (OFET) performance metrics:

- Carrier Mobility ( $\mu$ ): This is often the most significantly impacted parameter. Grain boundaries act as scattering sites and traps, leading to a substantial reduction in effective mobility compared to single-crystal devices.[4]

- Threshold Voltage ( $V_{th}$ ): Charge trapping at grain boundaries can lead to shifts in the threshold voltage, often requiring a higher gate voltage to turn the transistor "on." [5]

- On/Off Ratio: An increase in trapped charges can elevate the off-state current, thereby decreasing the on/off current ratio, a critical figure of merit for transistor switching applications.[2]

- Device Stability and Hysteresis: Trapping and de-trapping of charges at grain boundaries are often slow processes, which can lead to operational instability and hysteresis in the transistor's transfer characteristics.[2]

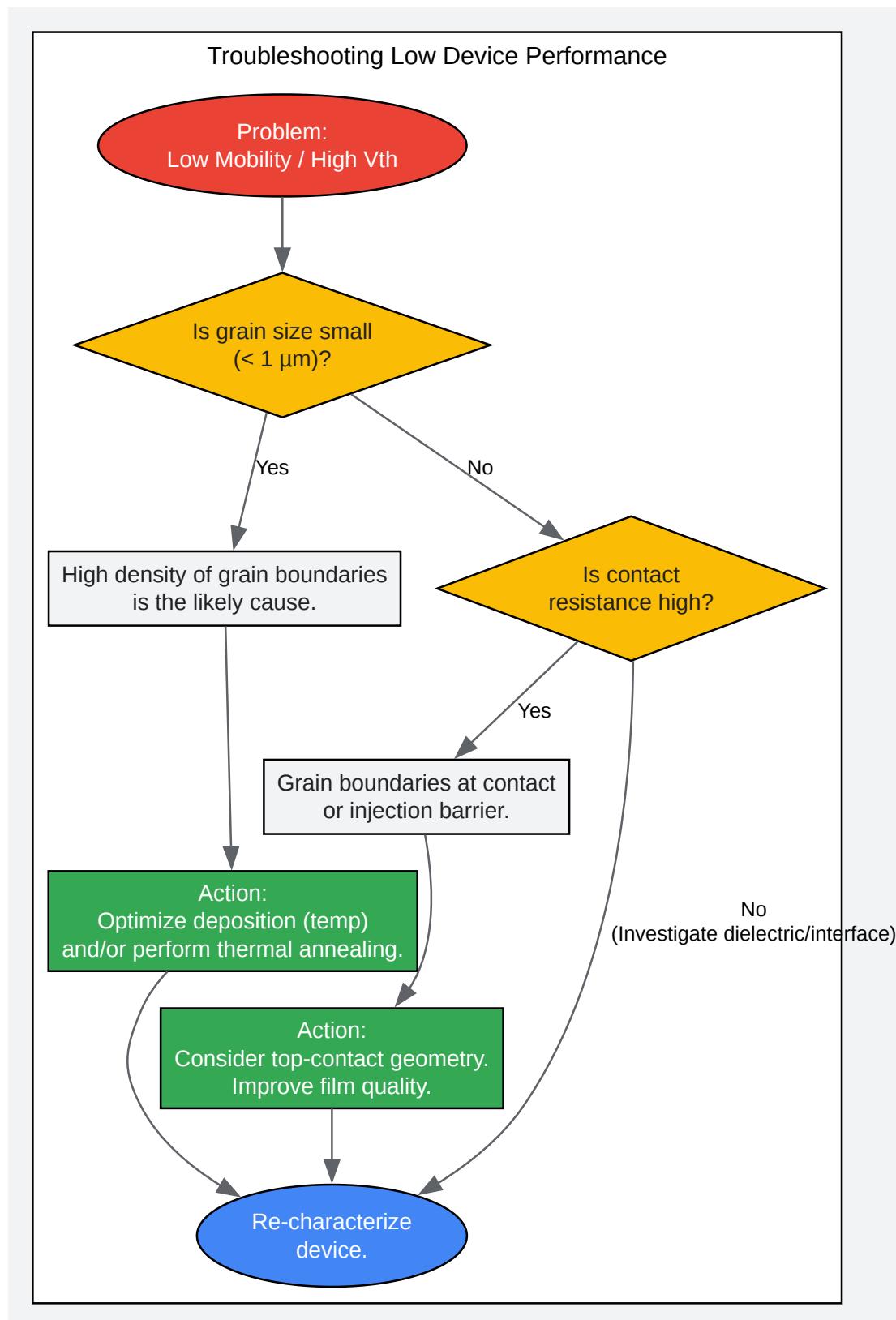

## Troubleshooting Guide

This guide addresses common issues encountered during experiments with **perfluoropentacene** OFETs, with a focus on problems originating from grain boundaries.

Issue 1: My OFET exhibits significantly lower electron mobility than expected.

- Potential Cause: A high density of grain boundaries in the PFP active layer. Small, disordered grains create numerous trapping sites and potential barriers that severely limit charge transport.[2] The relationship between mobility and grain size is not linear; a sharp decrease in mobility is often observed when grain size falls below a critical threshold.[2][6]

- Troubleshooting Steps:

- Morphological Analysis: Use Atomic Force Microscopy (AFM) to visualize the topography of your PFP film. This will allow you to directly observe the grain size and distribution.

- Optimize Deposition Conditions: The substrate temperature during thermal evaporation is a critical parameter. Increasing the substrate temperature often promotes the growth of larger grains.

- Post-Deposition Annealing: Thermal annealing of the completed film can improve molecular ordering and increase the average grain size.<sup>[7]</sup> Experiment with different annealing temperatures (e.g., 50°C to 120°C) and durations in an inert atmosphere to find the optimal conditions for recrystallization.<sup>[7][8]</sup>

- Substrate Surface Treatment: The surface energy of the dielectric layer can influence the growth of the semiconductor film.<sup>[9]</sup> Consider treating the dielectric surface (e.g., with HMDS or other silanizing agents) to promote more ordered, larger-grained film growth.<sup>[10]</sup>

Issue 2: The transfer characteristics of my device show significant hysteresis.

- Potential Cause: Slow charge trapping and de-trapping at deep trap states located at the grain boundaries or at the semiconductor-dielectric interface.<sup>[11]</sup> When you sweep the gate voltage, charges get trapped; on the reverse sweep, they are slowly released, causing a shift in the  $V_{th}$  and a history-dependent output.

- Troubleshooting Steps:

- Measure at Different Sweep Rates: Perform transfer curve measurements at various gate voltage sweep speeds. Hysteresis caused by slow traps will often be more pronounced at faster sweep rates.

- Improve Film Crystallinity: As with low mobility, techniques to increase grain size and reduce the density of grain boundaries (e.g., substrate heating, thermal annealing) can reduce the number of trap states responsible for hysteresis.<sup>[12]</sup>

- Dielectric Surface Passivation: Ensure the dielectric surface is clean and of high quality. Traps at the interface can also contribute significantly to hysteresis. A high-quality dielectric and proper surface treatment can mitigate this.<sup>[11]</sup>

Issue 3: My device has a high off-state current and a low on/off ratio.

- Potential Cause: Charge traps at grain boundaries can contribute to a higher off-state current (leakage).[2] Additionally, high contact resistance, which can be exacerbated by grain boundaries at the metal/semiconductor interface, can limit the on-state current, thereby reducing the overall on/off ratio.[13]

- Troubleshooting Steps:

- Analyze Contact Resistance: Use a method like the Transmission Line Method (TLM) to quantify the contact resistance. This requires fabricating devices with varying channel lengths. A high contact resistance points to injection issues.

- Optimize Device Architecture: In some cases, a top-contact architecture results in lower contact resistance compared to a bottom-contact structure because the metal is deposited onto the already-formed semiconductor film.[3]

- Increase Grain Size: Larger grains not only improve bulk transport but can also lead to lower contact resistance by reducing the number of grain boundaries in the contact region. [13]

## Data Summary

While specific quantitative data for **perfluoropentacene** is sparse, studies on pentacene provide a valuable model for the expected behavior. The following table summarizes the general correlation between grain size and key OFET device parameters based on pentacene research.

| Parameter                             | Small Grains (< 1 $\mu\text{m}$ )          | Large Grains (> 2 $\mu\text{m}$ )           | Probable Reason                                                                                        |

|---------------------------------------|--------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Field-Effect Mobility ( $\mu$ )       | Low (e.g., < 0.1 $\text{cm}^2/\text{Vs}$ ) | High (e.g., > 0.5 $\text{cm}^2/\text{Vs}$ ) | Reduced charge trapping and scattering at grain boundaries. <a href="#">[6]</a>                        |

| Threshold Voltage ( $V_{\text{th}}$ ) | Higher magnitude, positive shift           | Lower magnitude, near-zero                  | Fewer trapped charges that need to be overcome by the gate field. <a href="#">[5]</a>                  |

| Contact Resistance ( $R_c$ )          | High                                       | Low                                         | Fewer grain boundaries disrupting charge injection at the electrode interface.<br><a href="#">[13]</a> |

| Hysteresis                            | Often significant                          | Minimal                                     | Fewer slow trap states associated with disordered grain boundary regions. <a href="#">[11]</a>         |

## Visualizations

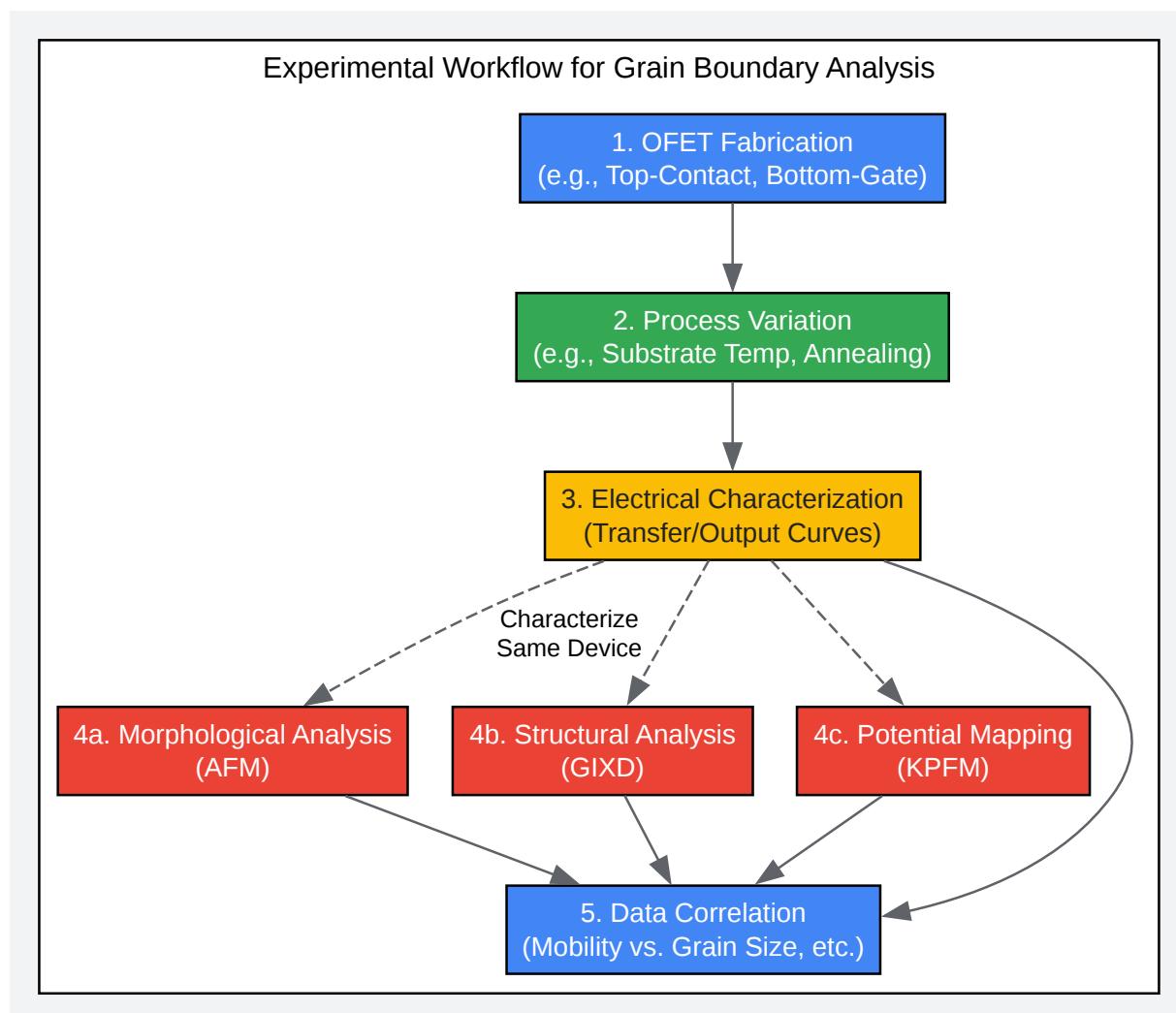

### Logical & Physical Diagrams

The following diagrams illustrate the mechanisms, workflows, and logic associated with studying grain boundary effects in **perfluoropentacene**.

[Click to download full resolution via product page](#)

Caption: Conceptual diagram of how grain boundaries impede charge transport.

[Click to download full resolution via product page](#)

Caption: Workflow for fabrication and characterization of PFP OFETs.

[Click to download full resolution via product page](#)

Caption: Troubleshooting logic for diagnosing performance issues in PFP OFETs.

## Experimental Protocols

### Protocol 1: Fabrication of a Top-Contact, Bottom-Gate PFP OFET

This protocol describes a common architecture for laboratory-scale OFETs.

- Substrate Preparation:

- Start with a heavily n-doped silicon wafer (Si++) which will serve as the common gate electrode.

- A layer of thermally grown silicon dioxide (SiO<sub>2</sub>, typically 200-300 nm) on top of the Si++ acts as the gate dielectric.

- Clean the substrate ultrasonically in a sequence of deionized water, acetone, and isopropanol (15 minutes each).

- Dry the substrate with a nitrogen gun and bake on a hotplate at 120°C for 10 minutes to remove residual moisture.

- Dielectric Surface Treatment (Optional but Recommended):

- To improve the interface quality, apply a self-assembled monolayer (SAM).

- A common method is vapor-phase treatment with hexamethyldisilazane (HMDS) or octadecyltrichlorosilane (OTS). Place the substrates in a vacuum desiccator with a small vial of the silanizing agent and hold under vacuum for several hours.

- **Perfluoropentacene** Deposition:

- Transfer the substrate into a high-vacuum thermal evaporation chamber (base pressure < 10<sup>-6</sup> mbar).

- Deposit a 30-50 nm thick film of **perfluoropentacene**. The deposition rate should be kept low and constant (e.g., 0.1-0.2 Å/s) to promote crystalline growth.

- The substrate temperature can be controlled during deposition (e.g., held at room temperature or elevated, such as 60-100°C) to influence grain size.

- Source-Drain Electrode Deposition:

- Without breaking vacuum, place a shadow mask with the desired channel dimensions (e.g., channel length  $L = 50 \mu\text{m}$ , channel width  $W = 1000 \mu\text{m}$ ) in contact with the PFP film.

- Deposit the source and drain contacts. A common choice is gold (Au) with a thickness of 40-60 nm, often with a thin adhesion layer of chromium (Cr) or titanium (Ti) (2-5 nm).

- Device Annealing (Optional):

- After fabrication, the device can be annealed on a hotplate in an inert environment (e.g., a nitrogen-filled glovebox) to improve film crystallinity. A typical condition is 120°C for 30 minutes.[\[7\]](#)

## Protocol 2: Characterization with Kelvin Probe Force Microscopy (KPFM)

KPFM is used to map the surface potential, revealing potential drops at grain boundaries.[\[14\]](#)

- System Setup:

- Use an Atomic Force Microscope (AFM) equipped with a KPFM module. A conductive AFM probe (e.g., platinum- or diamond-coated silicon) is required.

- Perform the measurement in a controlled environment (e.g., high vacuum or a nitrogen glovebox) to minimize surface contamination and the influence of adsorbates.

- Topography Scan:

- First, acquire a standard topography image of the PFP film using a non-contact or tapping mode. This map will show the physical locations of the grains and their boundaries.

- KPFM Scan (Dual-Pass Mode Example):

- Most KPFM systems use a dual-pass technique (often called LiftMode™ or similar).[\[15\]](#)

- First Pass: The cantilever scans a line to record the topography as in a normal AFM scan.

- Second Pass: The probe is lifted to a constant height (e.g., 20-50 nm) above the recorded topographic profile and re-scans the line.

- During the second pass, an AC voltage ( $V_{ac}$ ) is applied to the tip, causing it to oscillate due to the electrostatic force. A DC bias ( $V_{dc}$ ) is simultaneously applied and adjusted by a feedback loop to nullify this oscillation.

- The required  $V_{dc}$  to null the force is equal to the Contact Potential Difference (CPD) between the tip and the sample surface. The system records this  $V_{dc}$  value for each point, creating a surface potential map.

- Data Analysis:

- Correlate the topography map with the surface potential map. A lower or higher potential localized along the grain boundaries indicates the presence of trapped charges or dipoles, which create the potential barriers to charge transport.[16]

## Protocol 3: Characterization with Grazing-Incidence X-ray Diffraction (GIXD)

GIXD is a powerful technique to determine the crystal structure, molecular orientation, and crystallinity of thin films.[17][18]

- System Setup:

- This technique typically requires a synchrotron light source for a high-brilliance, collimated X-ray beam, although laboratory-based systems can also be used.[18]

- The sample is mounted on a multi-axis goniometer to precisely control the incident angle of the X-rays. A 2D area detector is used to capture the diffraction pattern.

- Measurement Geometry:

- The X-ray beam strikes the sample at a very shallow angle of incidence ( $\alpha_i$ ), typically between 0.1° and 0.5°. This angle is chosen to be near the critical angle for total external

reflection of the film material, which maximizes the signal from the thin film while minimizing the signal from the substrate.[19][20]

- The detector collects the diffracted X-rays over a range of exit angles and in-plane scattering angles.

- Data Acquisition:

- An exposure is taken to produce a 2D diffraction image. The positions and intensities of the diffraction spots or rings are recorded.

- Data Analysis:

- Peak Indexing: The positions of the diffraction peaks are used to determine the lattice parameters of the PFP crystal structure and identify the crystalline phase.[21]

- Orientation Analysis: The location of the peaks (e.g., on the in-plane or out-of-plane axes) reveals the orientation of the PFP molecules relative to the substrate (e.g., "standing up" or "lying down").

- Crystallinity Assessment: The sharpness and intensity of the diffraction peaks provide a qualitative measure of the film's crystallinity. Broader peaks indicate smaller crystallite domains (smaller grains) or higher disorder.[8]

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Perfluoropentacene - Wikipedia [en.wikipedia.org]

- 2. Influence of grain sizes on the mobility of organic thin-film transistors » JOANNEUM RESEARCH [joanneum.at]

- 3. journal.jsss.co.in [journal.jsss.co.in]

- 4. researchgate.net [researchgate.net]

- 5. mdpi.com [mdpi.com]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. arxiv.org [arxiv.org]

- 9. researchgate.net [researchgate.net]

- 10. ossila.com [ossila.com]

- 11. researchgate.net [researchgate.net]

- 12. mdpi.com [mdpi.com]

- 13. Grain size effects on contact resistance of top-contact pentacene TFTs - DRL [snudrl.snu.ac.kr]

- 14. researchgate.net [researchgate.net]

- 15. Kelvin Probe Force Microscopy (KPFM) | Bruker [bruker.com]

- 16. pureadmin.unileoben.ac.at [pureadmin.unileoben.ac.at]

- 17. researchgate.net [researchgate.net]

- 18. X-ray diffraction under grazing incidence conditions | Springer Nature Experiments [experiments.springernature.com]

- 19. youtube.com [youtube.com]

- 20. mdpi.com [mdpi.com]

- 21. Intensity corrections for grazing-incidence X-ray diffraction of thin films using static area detectors - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [impact of grain boundaries on charge transport in Perfluoropentacene]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b8735957#impact-of-grain-boundaries-on-charge-transport-in-perfluoropentacene]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)