# Technical Support Center: Perfluoropentacene (PFP) OFETs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Perfluoropentacene**

Cat. No.: **B8735957**

[Get Quote](#)

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing charge injection in **Perfluoropentacene** (PFP) Organic Field-Effect Transistors (OFETs).

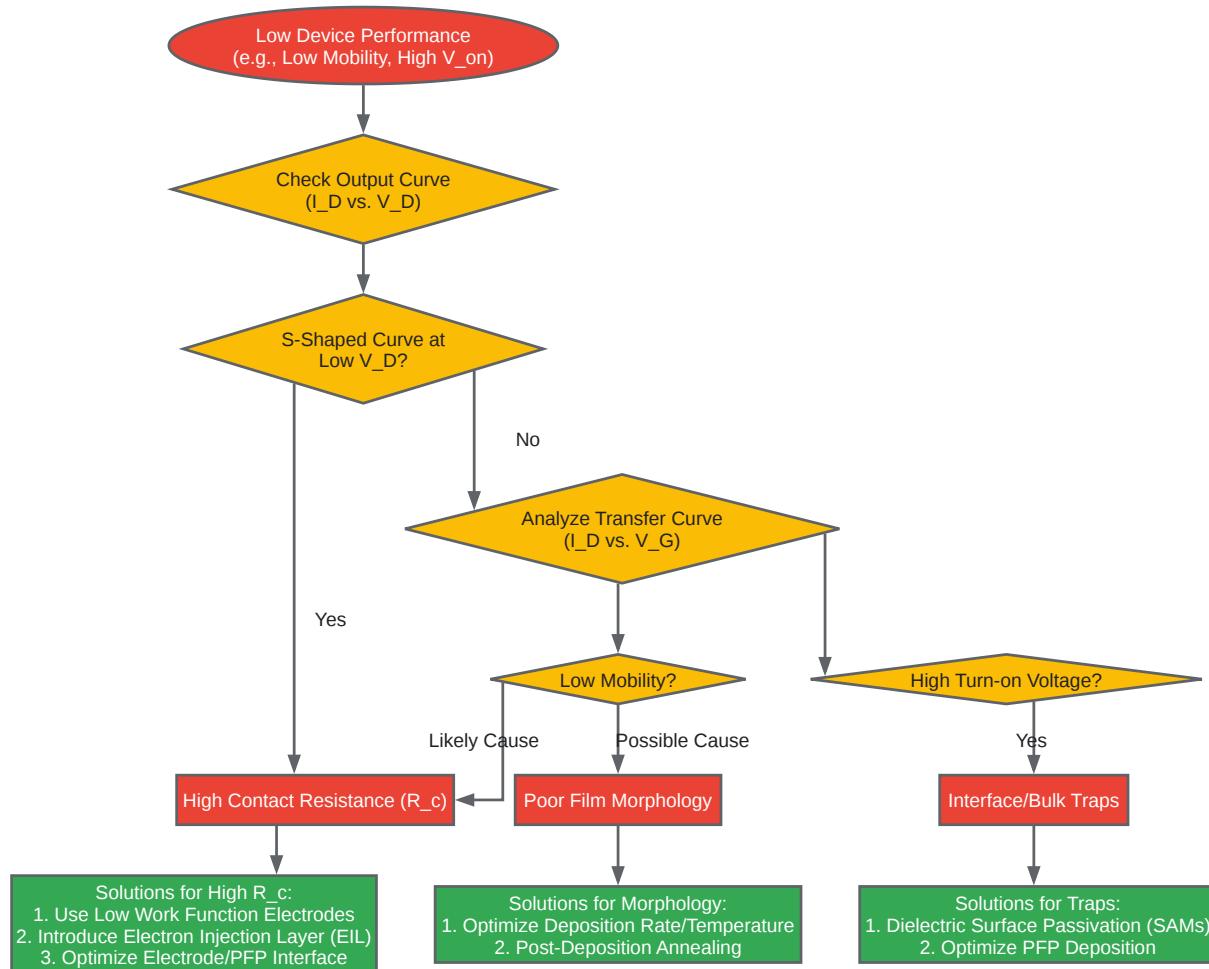

## Troubleshooting Guide

This guide addresses common issues encountered during the fabrication and characterization of PFP OFETs, focusing on poor charge injection and related performance degradation.

**Question:** My PFP OFET exhibits very low electron mobility. What are the potential causes and how can I troubleshoot this?

**Answer:** Low electron mobility in PFP OFETs is a frequent challenge that can stem from several factors. A systematic approach to troubleshooting is crucial for identifying and resolving the root cause.

- **High Contact Resistance:** A significant barrier to electron injection from the source electrode into the PFP semiconductor is a primary cause of low apparent mobility. This is often due to a mismatch between the work function of the electrode material and the Lowest Unoccupied Molecular Orbital (LUMO) of PFP.

- **Solution:** Employ low work function metals as source and drain electrodes to reduce the injection barrier.<sup>[1][2]</sup> Refer to the data table below for a comparison of different electrode

materials. Additionally, ensure pristine interfaces between the electrode and the organic semiconductor.

- Poor Film Morphology: The crystalline structure and morphology of the PFP thin film significantly impact charge transport. Disordered films with small grains and numerous grain boundaries will impede electron mobility.

- Solution: Optimize the deposition parameters during thermal evaporation, such as substrate temperature and deposition rate. A slower deposition rate can sometimes lead to more ordered film growth. Post-deposition annealing can also improve crystallinity, but the temperature must be carefully controlled to avoid damaging the film.

- Dielectric Interface Traps: Traps at the interface between the dielectric layer and the PFP semiconductor can capture electrons, reducing the number of mobile charge carriers and thus lowering mobility.

- Solution: Utilize a dielectric surface passivation layer. Self-assembled monolayers (SAMs) can reduce trap states and improve the morphology of the overlying PFP film.[\[3\]](#)

- Impurities: Contaminants in the PFP source material or within the deposition chamber can introduce traps and disrupt the molecular packing, leading to decreased mobility.

- Solution: Use high-purity PFP and ensure a high-vacuum environment during deposition to minimize contamination.

Question: I am observing a high "turn-on" voltage for my PFP OFET. What does this indicate and how can I reduce it?

Answer: A high turn-on voltage suggests the presence of a significant number of trap states that must be filled before a conductive channel can be formed.

- Interface Traps: As with low mobility, traps at the semiconductor-dielectric interface are a common cause.

- Solution: Surface passivation of the dielectric is an effective strategy to reduce trap density.[\[3\]](#)

- Bulk Traps: Defects within the PFP film itself can also act as traps.

- Solution: Optimizing the deposition conditions to improve the crystallinity and reduce defects in the PFP film can lower the bulk trap density.

Question: The output characteristics of my OFET are non-linear at low drain voltages. What is the cause of this "S-shaped" curve?

Answer: Non-linear, or "S-shaped," output characteristics at low drain voltages are a classic sign of high contact resistance. This indicates a significant injection barrier at the source contact, which impedes charge injection at low biases.

- Energy Level Mismatch: The primary cause is a poor energy level alignment between the source electrode's work function and the PFP's LUMO.

- Solution: The most effective solution is to use an electrode material with a work function that more closely matches the LUMO of PFP. Alternatively, an electron injection layer (EIL) or buffer layer can be introduced between the electrode and the PFP to facilitate a more gradual energy level transition.

## Frequently Asked Questions (FAQs)

Q1: What are the ideal electrode materials for n-type PFP OFETs?

A1: For n-type semiconductors like PFP, electrodes with low work functions are preferred to facilitate electron injection. While gold (Au) is commonly used due to its stability, its work function is not ideal for PFP. Materials like Calcium (Ca), Magnesium (Mg), or Aluminum (Al) have lower work functions and can lead to improved performance. However, these materials are more reactive and may require encapsulation to prevent degradation. The use of a thin buffer layer, such as a metal oxide or an n-doped organic layer, between a more stable electrode (like Au or Ag) and the PFP can also significantly enhance electron injection.[\[1\]](#)

Q2: What is the purpose of a dielectric surface treatment or passivation?

A2: A dielectric surface treatment, often using a self-assembled monolayer (SAM), serves two main purposes. First, it can passivate the dielectric surface, reducing the density of trap states that can immobilize charge carriers.[\[3\]](#) Second, it can modify the surface energy of the

dielectric, which can influence the growth mode and morphology of the subsequently deposited PFP film, leading to improved crystallinity and higher mobility.

**Q3:** How does the device architecture (e.g., top-contact vs. bottom-contact) affect charge injection in PFP OFETs?

**A3:** The device architecture can have a significant impact on contact resistance and charge injection. In a bottom-contact architecture, the PFP is deposited on top of the pre-patterned source and drain electrodes. This can sometimes lead to a less favorable morphology of the PFP at the contact interface. In a top-contact architecture, the electrodes are evaporated onto the PFP film. This often results in a more intimate contact and can lead to lower contact resistance, as the PFP film morphology is established before the electrode deposition.

**Q4:** How can I measure the contact resistance in my PFP OFETs?

**A4:** The Transmission Line Method (TLM) is a widely used technique to determine the contact resistance in OFETs. This method involves fabricating a series of transistors with identical channel widths but varying channel lengths. By plotting the total device resistance as a function of the channel length, the contact resistance can be extracted from the y-intercept.[\[4\]](#)[\[5\]](#)[\[6\]](#)[\[7\]](#)

**Q5:** What is the role of vacuum quality during the thermal evaporation of PFP?

**A5:** The quality of the vacuum during thermal evaporation is critical for achieving high-performance PFP OFETs. A high vacuum (typically in the range of  $10^{-6}$  to  $10^{-7}$  Torr) is necessary to minimize the incorporation of impurities, such as oxygen and water, into the PFP film. These impurities can act as traps for electrons and degrade device performance and stability.[\[8\]](#)

## Quantitative Data Summary

The following table summarizes key performance parameters for PFP OFETs under different experimental conditions.

| Organic Semiconductor                | Electrode Material | Dielectric       | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio     | Reference |

|--------------------------------------|--------------------|------------------|--------------------------------|------------------|-----------|

| Perfluoropentacene                   | Gold (Au)          | SiO <sub>2</sub> | ~0.11                          | >10 <sup>5</sup> | [9]       |

| Perfluoropentacene                   | Not Specified      | Not Specified    | >0.2                           | Not Specified    |           |

| Pentacene<br>(p-type for comparison) | Gold (Au)          | SiO <sub>2</sub> | ~0.2                           | Not Specified    | [10]      |

| Pentacene<br>(p-type for comparison) | Copper (Cu)        | SiO <sub>2</sub> | ~0.2                           | Not Specified    | [10]      |

Note: Direct comparative data for PFP with various low work function electrodes is limited in the provided search results. The table highlights the reported mobility for PFP with gold electrodes and provides a comparison with its p-type counterpart, pentacene.

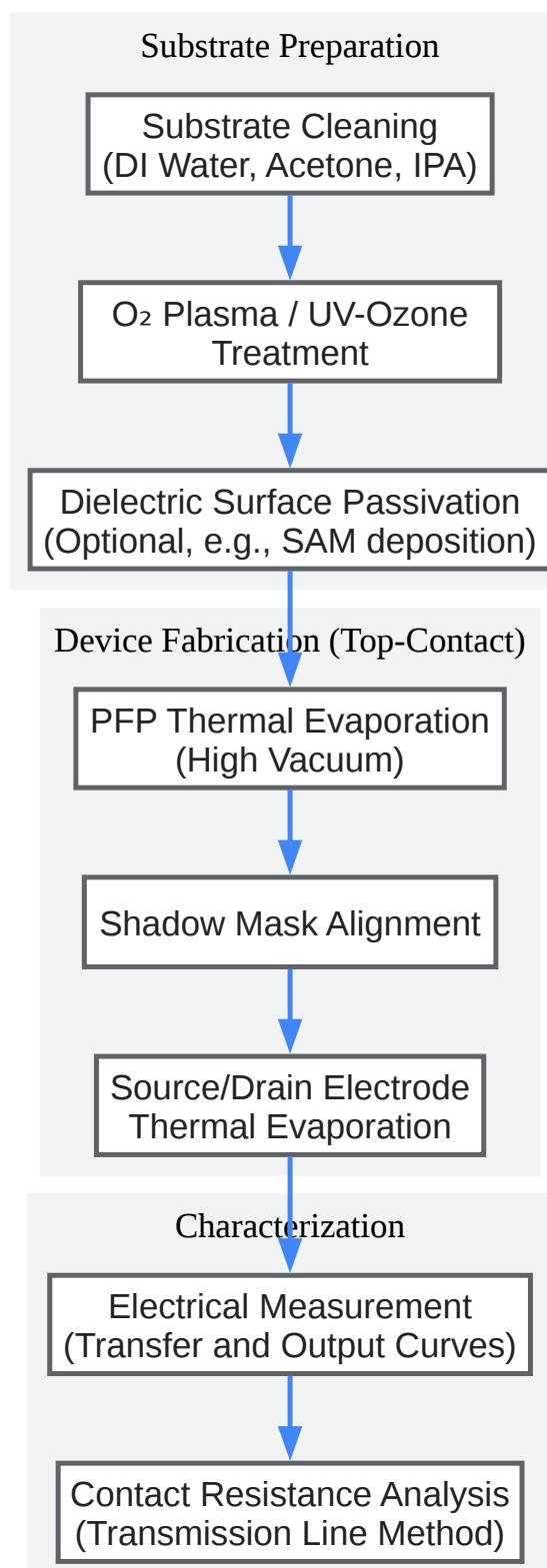

## Experimental Protocols

### Protocol 1: Fabrication of Top-Contact PFP OFETs by Thermal Evaporation

- Substrate Cleaning:

- Begin with a heavily doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer, which will serve as the gate electrode and gate dielectric, respectively.

- Clean the substrate sequentially in an ultrasonic bath with deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of dry nitrogen.

- Treat the substrate with an oxygen plasma or UV-ozone for 10 minutes to remove any remaining organic residues and to hydroxylate the surface for subsequent surface treatments.

- Dielectric Surface Passivation (Optional but Recommended):

- Prepare a dilute solution of a silane-based self-assembled monolayer (SAM) material (e.g., octadecyltrichlorosilane - OTS) in an anhydrous solvent like toluene or hexane.

- Immerse the cleaned substrate in the SAM solution for a specified time (typically 12-24 hours) in a controlled environment (e.g., a glovebox).

- Rinse the substrate thoroughly with the pure solvent to remove any excess, non-bonded SAM molecules.

- Anneal the substrate at a moderate temperature (e.g., 120 °C) to promote the formation of a dense monolayer.

- **Perfluoropentacene (PFP) Deposition:**

- Place the substrate into a high-vacuum thermal evaporation system.

- Load high-purity PFP powder into a quartz crucible.

- Evacuate the chamber to a base pressure of at least  $10^{-6}$  Torr.

- Heat the crucible to sublimate the PFP. The deposition rate should be carefully controlled, typically in the range of 0.1-0.5 Å/s, and monitored using a quartz crystal microbalance.

- Deposit a PFP film of the desired thickness (typically 30-50 nm).

- Allow the substrate to cool to room temperature before breaking the vacuum.

- Source and Drain Electrode Deposition:

- Place a shadow mask with the desired channel length and width dimensions onto the PFP-coated substrate.

- Return the substrate to the thermal evaporation system.

- Deposit the desired electrode material (e.g., a low work function metal like Calcium followed by a protective layer of Aluminum or Silver) through the shadow mask. The

thickness of the electrodes is typically 50-100 nm.

- Remove the substrate from the chamber after the deposition is complete.

#### Protocol 2: Measurement of Contact Resistance using the Transmission Line Method (TLM)

- Device Fabrication:

- Fabricate a series of PFP OFETs on the same substrate with a constant channel width (W) and varying channel lengths (L) using the protocol described above. A shadow mask with multiple channel lengths is required for this step.

- Electrical Characterization:

- Use a semiconductor parameter analyzer to measure the transfer characteristics (Drain Current,  $I_D$  vs. Gate Voltage,  $V_G$ ) for each transistor at a low, constant drain voltage ( $V_D$ ) to ensure operation in the linear regime.

- From the transfer curve of each device, calculate the total resistance ( $R_{\text{total}}$ ) at a specific gate voltage ( $V_G$ ) in the linear region using the formula:  $R_{\text{total}} = V_D / I_D$ .

- Data Analysis:

- Plot the total resistance ( $R_{\text{total}}$ ) as a function of the channel length (L) for the different devices at the same gate voltage.

- Perform a linear fit to the data points.

- The y-intercept of the linear fit corresponds to twice the contact resistance ( $2 * R_c$ ), as the total resistance includes the contributions from both the source and drain contacts.

- The contact resistance ( $R_c$ ) can then be calculated by dividing the y-intercept by two.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for poor performance in PFP OFETs.

[Click to download full resolution via product page](#)

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. cityu.edu.hk [cityu.edu.hk]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- 4. pubs.acs.org [pubs.acs.org]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. pubs.aip.org [pubs.aip.org]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Perfluoropentacene (PFP) OFETs]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b8735957#improving-charge-injection-in-perfluoropentacene-ofets>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)