# Application Notes and Protocols for CMOS-like Inverters using Perfluoropentacene

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Perfluoropentacene**

Cat. No.: **B8735957**

[Get Quote](#)

For Researchers, Scientists, and Drug Development Professionals

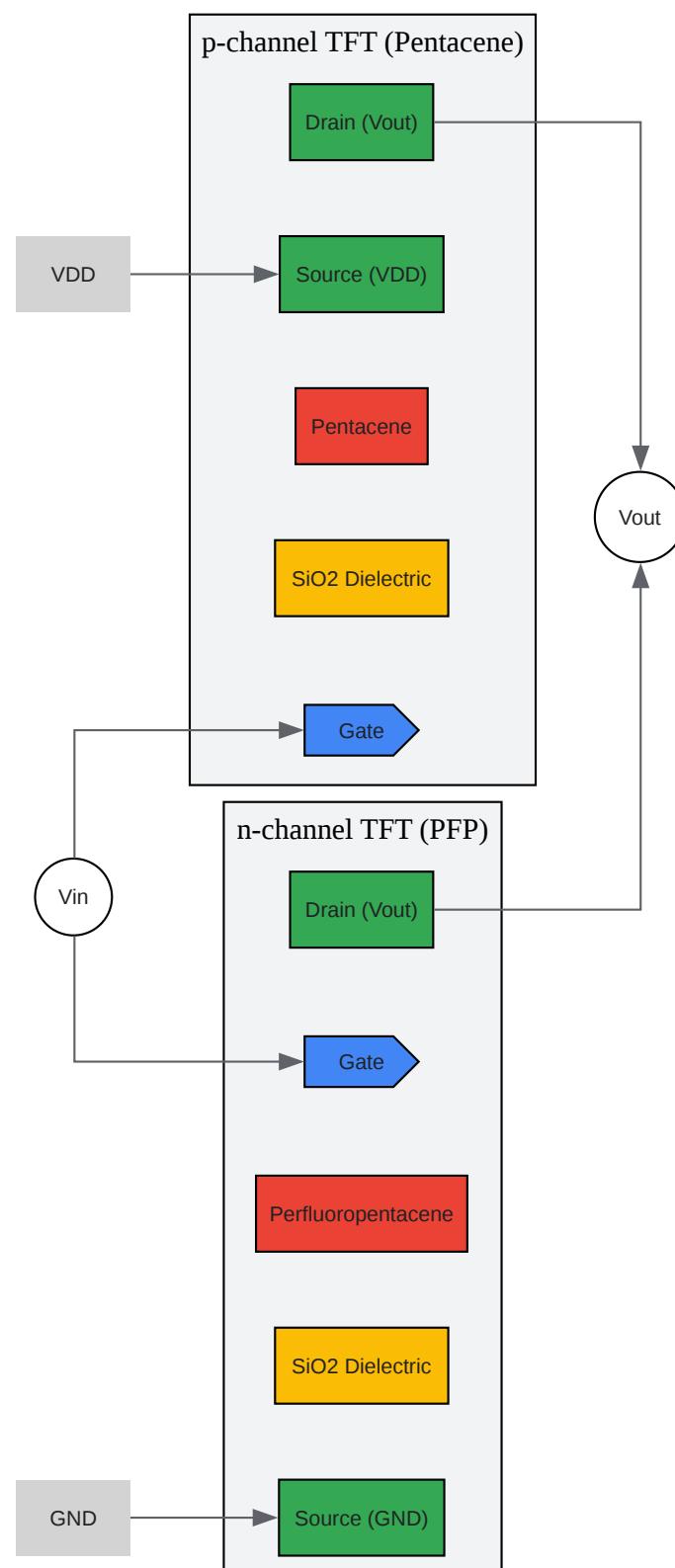

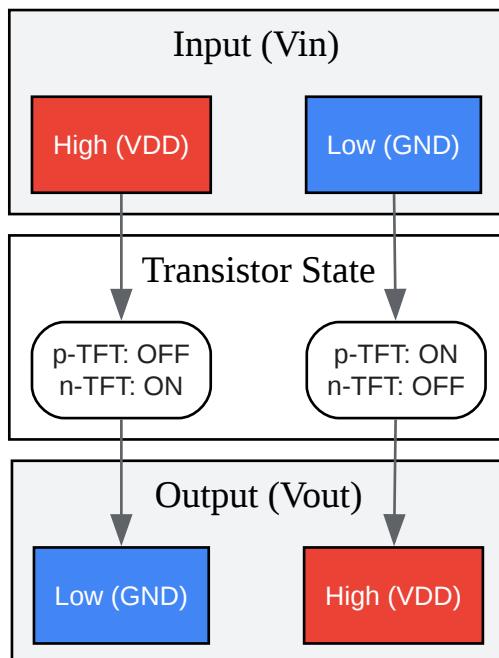

These application notes provide a comprehensive overview and detailed protocols for the fabrication and characterization of CMOS-like inverters utilizing the n-type organic semiconductor, **perfluoropentacene** (PFP), in conjunction with the p-type organic semiconductor, pentacene.

**Perfluoropentacene** ( $C_{22}F_{14}$ ) is a planar, crystalline organic material that serves as a robust n-type semiconductor due to the fluorination of pentacene, which lowers its HOMO energy levels and facilitates electron injection.<sup>[1]</sup> Its structural compatibility with pentacene, a well-known p-type semiconductor with high hole mobility, allows for the creation of efficient organic p-n junctions and complementary logic circuits.<sup>[2][3]</sup>

## Data Presentation: Performance Metrics

The performance of **perfluoropentacene**-based CMOS-like inverters is summarized in the table below. These values are compiled from various reports and represent typical device performance.

| Parameter                            | Symbol                   | Value        | Unit                                  | Notes                                                                                                |

|--------------------------------------|--------------------------|--------------|---------------------------------------|------------------------------------------------------------------------------------------------------|

| PFP (n-channel)<br>Performance       |                          |              |                                       |                                                                                                      |

| Electron Mobility                    | $\mu_e$                  | 0.11 - 0.22  | $\text{cm}^2/(\text{V}\cdot\text{s})$ | Dependent on fabrication conditions and device architecture. <a href="#">[3]</a> <a href="#">[4]</a> |

| On/Off Current Ratio                 | $\text{Ion}/\text{Ioff}$ | $> 10^5$     | -                                     | Indicates good switching behavior. <a href="#">[4]</a>                                               |

| Pentacene (p-channel)<br>Performance |                          |              |                                       |                                                                                                      |

| Hole Mobility                        | $\mu_h$                  | $> 1$        | $\text{cm}^2/(\text{V}\cdot\text{s})$ | High mobility contributes to good inverter performance. <a href="#">[2]</a>                          |

| On/Off Current Ratio                 | $\text{Ion}/\text{Ioff}$ | $> 10^6$     | -                                     |                                                                                                      |

| CMOS-like<br>Inverter<br>Performance |                          |              |                                       |                                                                                                      |

| Voltage Gain                         | $A_V$                    | up to 45     | V/V                                   | Demonstrates effective signal inversion and amplification. <a href="#">[4]</a>                       |

| Supply Voltage                       | VDD                      | 10 - 40      | V                                     | Operating voltage range for typical devices.                                                         |

| Switching Threshold                  | $V_{th}$                 | $\sim VDD/2$ | V                                     | For symmetric inverters.                                                                             |

# Experimental Protocols

Detailed methodologies for the fabrication and characterization of top-contact, bottom-gate **perfluoropentacene**/pentacene CMOS-like inverters are provided below.

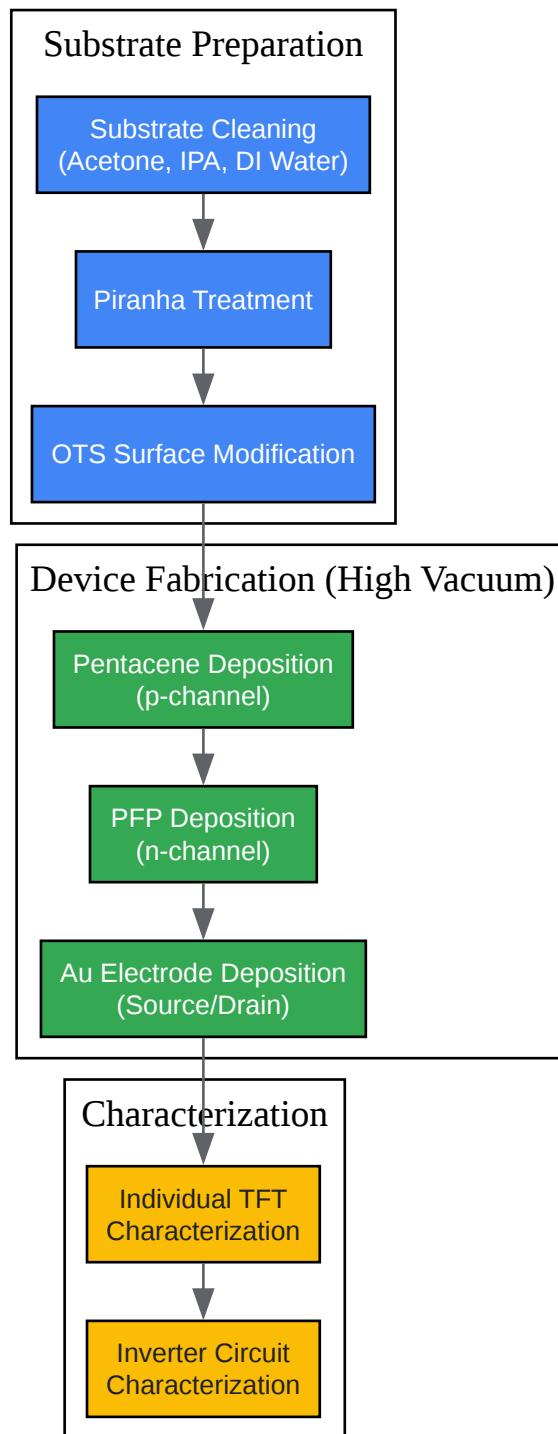

## Substrate Preparation and Cleaning

A thorough cleaning of the substrate is crucial for high-performance organic electronic devices.

- Materials:

- Highly p-doped Silicon wafers with a 300 nm thermally grown  $\text{SiO}_2$  layer (serves as the gate dielectric and substrate).

- Acetone (semiconductor grade).

- Isopropyl alcohol (IPA, semiconductor grade).

- Deionized (DI) water (18  $\text{M}\Omega\cdot\text{cm}$ ).

- Piranha solution (3:1 mixture of concentrated  $\text{H}_2\text{SO}_4$  and 30%  $\text{H}_2\text{O}_2$ ). (Caution: Piranha solution is extremely corrosive and reactive. Handle with extreme care in a fume hood with appropriate personal protective equipment).

- Octadecyltrichlorosilane (OTS) solution (0.5% in a 1:4 v/v mixture of chloroform and hexane).

- Protocol:

- Cut the  $\text{Si}/\text{SiO}_2$  wafer into the desired substrate size.

- Place the substrates in a beaker and sonicate for 15 minutes each in acetone, then IPA, and finally DI water.<sup>[3]</sup>

- Dry the substrates with a stream of dry nitrogen ( $\text{N}_2$ ).

- For surface hydroxylation, immerse the substrates in a freshly prepared piranha solution for 30 minutes.<sup>[3]</sup>

- Rinse the substrates thoroughly with DI water and dry with N<sub>2</sub>.

- For a hydrophobic surface treatment to improve the morphology of the organic semiconductor films, immerse the cleaned and dried substrates in the OTS solution for 30 minutes.[3]

- Rinse the OTS-treated substrates with chloroform and hexane, then dry with N<sub>2</sub>.

- Store the cleaned substrates in a clean, dry environment before use.

## Fabrication of the CMOS-like Inverter

This protocol describes the fabrication of separate p-type (pentacene) and n-type (**perfluoropentacene**) thin-film transistors (TFTs) on the same substrate to form a CMOS-like inverter. This is achieved using shadow masks to define the areas for each semiconductor and the source-drain electrodes.

- Materials and Equipment:

- Cleaned Si/SiO<sub>2</sub> substrates.

- Pentacene powder (99.9% purity).

- **Perfluoropentacene** powder (99.9% purity).

- Gold (Au) pellets or wire (99.99% purity).

- High-vacuum thermal evaporator system (< 10<sup>-6</sup> Torr).

- Shadow masks for defining semiconductor and electrode patterns.

- Quartz crystal microbalance (QCM) for monitoring deposition thickness and rate.

- Protocol:

- Mount the cleaned substrates and the shadow masks in the thermal evaporator.

- Load pentacene, **perfluoropentacene**, and gold into separate evaporation boats.

- Evacuate the chamber to a base pressure of  $< 10^{-6}$  Torr.

- Pentacene Deposition (p-channel TFT):

- Position the shadow mask for the p-channel region over the substrate.

- Heat the pentacene source and deposit a 50 nm thick film at a rate of 0.1-0.2 Å/s. The substrate should be held at room temperature.

- **Perfluoropentacene** Deposition (n-channel TFT):

- Without breaking the vacuum, switch the shadow mask to expose the n-channel region.

- Heat the **perfluoropentacene** source and deposit a 50 nm thick film at a similar deposition rate.

- Source-Drain Electrode Deposition:

- Position the shadow mask for the source and drain electrodes over both the pentacene and **perfluoropentacene** regions.

- Deposit a 50 nm thick layer of gold at a rate of 0.5 Å/s to define the top-contact source and drain electrodes for both the p-channel and n-channel transistors.

- Vent the chamber and carefully remove the substrates.

## Electrical Characterization

The electrical characteristics of the individual TFTs and the complete inverter circuit are measured using a semiconductor parameter analyzer in a probe station.

- Equipment:

- Probe station with micro-manipulators.

- Semiconductor parameter analyzer (e.g., Keysight B1500A or similar).

- Protocol for Individual Transistors (p-channel and n-channel):

- Place the substrate on the probe station chuck.

- Contact the source, drain, and gate electrodes of a single transistor with the probe tips.

- Output Characteristics (Id-Vd):

- For the p-channel (pentacene) TFT, sweep the drain-source voltage (Vd) from 0 V to -40 V in steps, for different gate-source voltages (Vg) from 0 V to -40 V in steps of -10 V.

- For the n-channel (PFP) TFT, sweep Vd from 0 V to 40 V, for Vg from 0 V to 40 V in steps of 10 V.

- Transfer Characteristics (Id-Vg):

- For the p-channel TFT, set a constant Vd of -40 V and sweep Vg from 20 V to -40 V.

- For the n-channel TFT, set a constant Vd of 40 V and sweep Vg from -20 V to 40 V.

- Protocol for the CMOS-like Inverter:

- Connect the source of the p-channel TFT to the supply voltage (VDD).

- Connect the source of the n-channel TFT to ground (GND).

- Connect the gates of both transistors together to form the input (Vin).

- Connect the drains of both transistors together to form the output (Vout).

- Apply a VDD (e.g., 40 V).

- Sweep the input voltage (Vin) from 0 V to VDD and measure the output voltage (Vout).

- The voltage gain (Av) is calculated as the derivative of the transfer curve ( $-dVout/dVin$ ) at the switching threshold.

## Visualizations

### Device Structure and Inverter Circuit

[Click to download full resolution via product page](#)

Caption: CMOS-like inverter circuit diagram.

## Fabrication Workflow

[Click to download full resolution via product page](#)

Caption: Fabrication and characterization workflow.

## Logical Inversion

[Click to download full resolution via product page](#)

Caption: Logical operation of the CMOS-like inverter.

### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Structure and morphology of coevaporated pentacene-perfluoropentacene thin films - PubMed [pubmed.ncbi.nlm.nih.gov]

- 2. ossila.com [ossila.com]

- 3. pure.mpg.de [pure.mpg.de]

- 4. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols for CMOS-like Inverters using Perfluoropentacene]. BenchChem, [2025]. [Online PDF]. Available at:

[<https://www.benchchem.com/product/b8735957#cmos-like-inverters-using-perfluoropentacene>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

**Contact**

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)