# A Comparative Guide: Perfluoropentacene OFETs vs. Amorphous Silicon TFTs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Perfluoropentacene**

Cat. No.: **B8735957**

[Get Quote](#)

For Researchers, Scientists, and Drug Development Professionals

In the landscape of thin-film transistor technologies, both organic and inorganic materials offer distinct advantages and disadvantages. This guide provides a detailed comparison of n-type **perfluoropentacene** (PFP) organic field-effect transistors (OFETs) and amorphous silicon (a-Si) thin-film transistors (TFTs), offering insights into their performance, fabrication, and operational principles to aid in material and device selection for a range of applications, from flexible electronics to sensing platforms.

## Performance Benchmarking

The performance of PFP OFETs and a-Si TFTs is summarized in the table below. While a-Si TFTs generally exhibit higher on/off ratios, PFP OFETs can achieve comparable electron mobility, a key parameter for device speed and performance.

| Performance Metric                   | Perfluoropentacene (PFP)<br>OFETs                                                                         | Amorphous Silicon (a-Si)<br>TFTs                                                                  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Electron Mobility ( $\mu$ )          | 0.043 - 0.22 cm <sup>2</sup> /Vs[1]                                                                       | 0.1 - 1.0 cm <sup>2</sup> /Vs                                                                     |

| On/Off Current Ratio                 | $\sim 10^5$ [1]                                                                                           | $\geq 10^7$                                                                                       |

| Threshold Voltage (V <sub>th</sub> ) | Typically a few volts (positive)                                                                          | Typically 1-3 V                                                                                   |

| Operational Stability                | Moderate; fluorination enhances resistance to oxidation.[2] Susceptible to degradation under bias stress. | Good; established technology with known degradation mechanisms under bias stress and temperature. |

| Processing Temperature               | Low temperature (compatible with flexible substrates)                                                     | Relatively low temperature (~110-350°C)                                                           |

## Experimental Protocols

Detailed methodologies for the fabrication of both transistor types are crucial for reproducibility and optimization. Below are representative protocols for creating top-contact, bottom-gate PFP OFETs and inverted staggered a-Si TFTs.

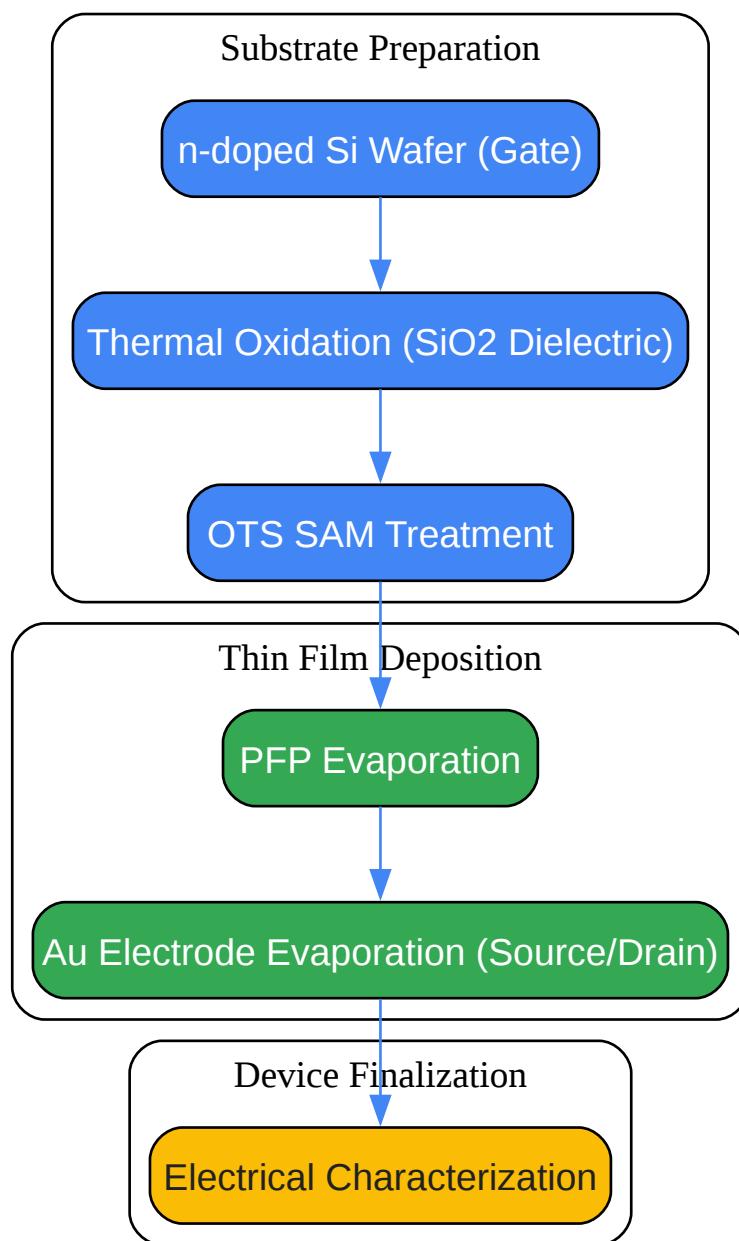

### Perfluoropentacene OFET Fabrication (Top-Contact, Bottom-Gate)

This protocol describes a common method for fabricating PFP OFETs, where the gate is at the bottom of the device and the source/drain electrodes are deposited on top of the organic semiconductor.

- Substrate Preparation:

- Start with a heavily n-doped silicon wafer which will act as the gate electrode.

- A layer of silicon dioxide (SiO<sub>2</sub>), typically 200-300 nm thick, is thermally grown on the silicon wafer to serve as the gate dielectric.

- The SiO<sub>2</sub> surface is then treated to improve the interface quality for the organic semiconductor. This is often done by creating a self-assembled monolayer (SAM) of a

material like octadecyltrichlorosilane (OTS).

- Organic Semiconductor Deposition:

- The **perfluoropentacene** (PFP) active layer is deposited onto the treated  $\text{SiO}_2$  surface.

- This is typically done via thermal evaporation in a high-vacuum chamber (e.g., at a pressure of  $\sim 10^{-6}$  Torr). The substrate temperature is often held at an elevated temperature (e.g., 50°C) during deposition to improve film crystallinity and device performance.<sup>[1]</sup> The deposition rate is carefully controlled (e.g., 0.1-0.5 Å/s).

- Source and Drain Electrode Deposition:

- Gold (Au) is commonly used for the source and drain electrodes due to its high work function, which facilitates electron injection into the PFP layer.

- The electrodes are deposited on top of the PFP layer through a shadow mask using thermal evaporation. The shadow mask defines the channel length and width of the transistor.

- Device Characterization:

- The electrical characteristics of the fabricated OFETs are measured in a vacuum or inert atmosphere using a semiconductor parameter analyzer.

- Key parameters such as electron mobility, on/off ratio, and threshold voltage are extracted from the output and transfer characteristics.

## Amorphous Silicon TFT Fabrication (Inverted Staggered)

The inverted staggered structure is a standard architecture for a-Si TFTs, where the gate electrode is at the bottom, followed by the gate insulator, the a-Si active layer, and finally the source/drain contacts.

- Gate Electrode Formation:

- A metal layer, such as molybdenum (Mo), is deposited on a glass substrate by sputtering and patterned using photolithography and etching to form the gate electrode.

- Deposition of Insulator and Semiconductor Layers:

- A silicon nitride ( $\text{SiN}_x$ ) layer, serving as the gate insulator, is deposited over the gate electrode and substrate using Plasma-Enhanced Chemical Vapor Deposition (PECVD).

- Subsequently, a layer of hydrogenated amorphous silicon (a-Si:H) is deposited on top of the  $\text{SiN}_x$  layer, also by PECVD.

- Finally, a highly doped n+ a-Si:H layer is deposited to ensure good ohmic contact with the source and drain electrodes.

- Source and Drain Electrode Formation:

- A metal layer, such as aluminum (Al) or a Mo/Al bilayer, is deposited by sputtering.

- The metal layer is then patterned using photolithography and etching to define the source and drain electrodes. The n+ a-Si:H layer in the channel region is also etched away during this step.

- Passivation:

- A final passivation layer of  $\text{SiN}_x$  is often deposited by PECVD to protect the device from environmental factors.

- Device Characterization:

- The TFTs are characterized using a semiconductor parameter analyzer to determine their electrical properties, including mobility, threshold voltage, and on/off ratio.

## Visualizing the Workflow and Operational Principles

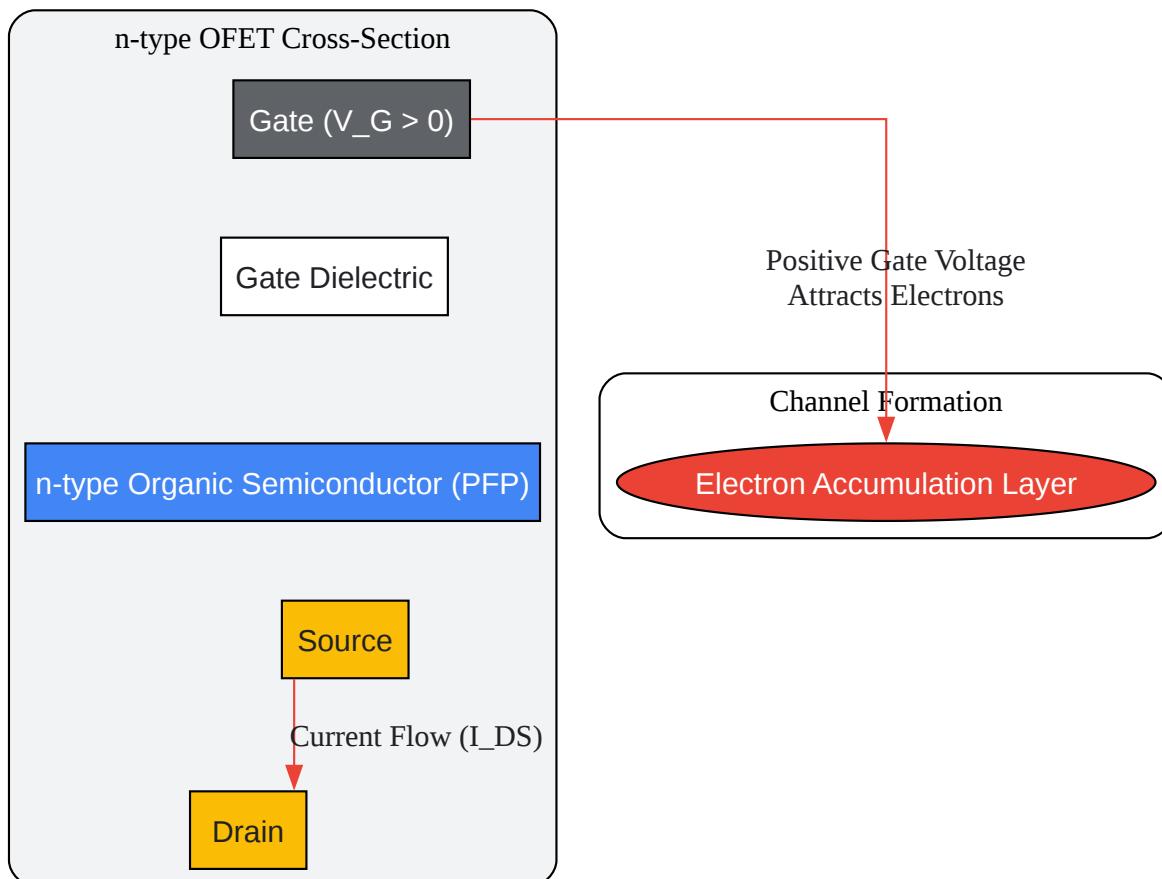

The following diagrams, generated using the DOT language, illustrate the fabrication workflow for a PFP OFET and the operational principle of an n-type OFET.

[Click to download full resolution via product page](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [datapdf.com](http://datapdf.com) [datapdf.com]

- 2. Ambient stable solution-processed organic field effect transistors from electron deficient planar aromatics: effect of end-groups on ambient stability - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [A Comparative Guide: Perfluoropentacene OFETs vs. Amorphous Silicon TFTs]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b8735957#benchmarking-perfluoropentacene-ofets-against-amorphous-silicon-tfts>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)