# Technical Support Center: Optimizing 2D Heterostructure Device Performance with Annealing

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: 3-(Dicyanomethylidene)indan-1-one

Cat. No.: B085603

[Get Quote](#)

Welcome to the technical support center for researchers, scientists, and drug development professionals working with two-dimensional (2D) heterostructure devices. This resource provides troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during experimental work, with a focus on leveraging annealing strategies to enhance device performance.

## Frequently Asked Questions (FAQs)

**Q1:** What is the primary purpose of annealing 2D heterostructure devices?

Annealing is a critical post-fabrication thermal treatment step used to improve the quality and performance of 2D heterostructure devices.[\[1\]](#)[\[2\]](#)[\[3\]](#) Its main goals are to:

- Improve Interfacial Quality: By heating the device, trapped contaminants, such as organic residues and water molecules, at the interface between the stacked 2D materials can be removed.[\[1\]](#) This leads to a cleaner and more intimate van der Waals interface, which is crucial for efficient charge transport.

- Reduce Bubbles and Wrinkles: During the transfer and stacking of 2D materials, bubbles and wrinkles can form, which negatively impact device performance.[\[1\]](#)[\[2\]](#) Annealing can help to

reduce the density of these defects by allowing smaller bubbles to coalesce and migrate to the edges of the material flakes.[1]

- **Enhance Electrical Contacts:** High contact resistance between the metal electrodes and the 2D semiconductor is a common issue that limits device performance.[2][3][4] Annealing can improve the metal-semiconductor interface, leading to lower contact resistance and improved charge injection.[2]

- **Activate Dopants and Repair Lattice Damage:** In some cases, annealing can be used to activate implanted dopants or to repair crystal lattice damage that may have occurred during device fabrication.

Q2: What are the typical annealing temperatures and durations for 2D heterostructure devices?

The optimal annealing parameters, including temperature and duration, are highly dependent on the specific materials in the heterostructure and the substrate. However, some general guidelines can be provided:

| Material System                  | Typical Annealing Temperature (°C) | Typical Duration (hours) | Atmosphere                      | Reference |

|----------------------------------|------------------------------------|--------------------------|---------------------------------|-----------|

| Graphene/hBN Heterostructures    | 250 - 350                          | 6 - 8                    | UHV or Forming Gas              | [1]       |

| Graphene/hBN with metal contacts | ~300                               | 3                        | H <sub>2</sub> /Ar              | [5]       |

| General 2D Heterostructures      | 150 - 400                          | 2 - 12                   | Inert Gas (Ar, N <sub>2</sub> ) |           |

Note: It is crucial to carefully consider the thermal stability of all materials in the device stack, including the substrate and metal contacts, to prevent degradation. For instance, high-vacuum annealing of devices with metal leads can lead to "balling up" of the metal.[1] In such cases, annealing in a forming gas environment is preferable.[1]

## Troubleshooting Guide

### Issue 1: High Contact Resistance in the Device

**Symptom:** The device exhibits poor current-voltage (I-V) characteristics, with a non-linear or highly resistive behavior at the contacts.

**Possible Cause:** Incomplete removal of polymer residues from the transfer process or a poor interface between the metal electrode and the 2D semiconductor.

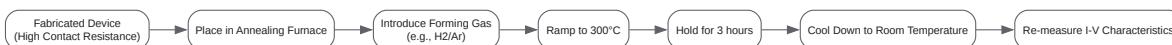

**Annealing Strategy:**

- **Protocol:** Perform a post-fabrication anneal in a forming gas (a mixture of hydrogen and an inert gas like argon or nitrogen) or ultra-high vacuum (UHV) environment.

- **Experimental Workflow:**

[Click to download full resolution via product page](#)

**Fig. 1:** Annealing workflow for reducing contact resistance.

- **Expected Outcome:** A significant reduction in contact resistance, leading to improved linearity and higher current in the I-V characteristics.

### Issue 2: Presence of Bubbles and Wrinkles at the Heterostructure Interface

**Symptom:** Atomic Force Microscopy (AFM) or optical microscopy reveals the presence of bubbles and wrinkles between the stacked 2D material layers. These defects can lead to inconsistent device performance and reduced carrier mobility.

**Possible Cause:** Trapped air, moisture, or organic contaminants between the layers during the mechanical stacking process.

**Annealing Strategy:**

- Protocol: Annealing in a UHV environment (better than  $10^{-6}$  mbar) can effectively reduce the density of bubbles.[1] The heat allows trapped gases to escape and smaller bubbles to merge and move to the edges of the flakes.[1]

- Experimental Protocol:

- Transfer the fabricated device into a UHV chamber.

- Gradually ramp up the temperature to 250-350°C.

- Maintain the temperature for 6-8 hours.

- Slowly cool the device back to room temperature before removal.

- Characterize the device using AFM to confirm the reduction in bubble density.

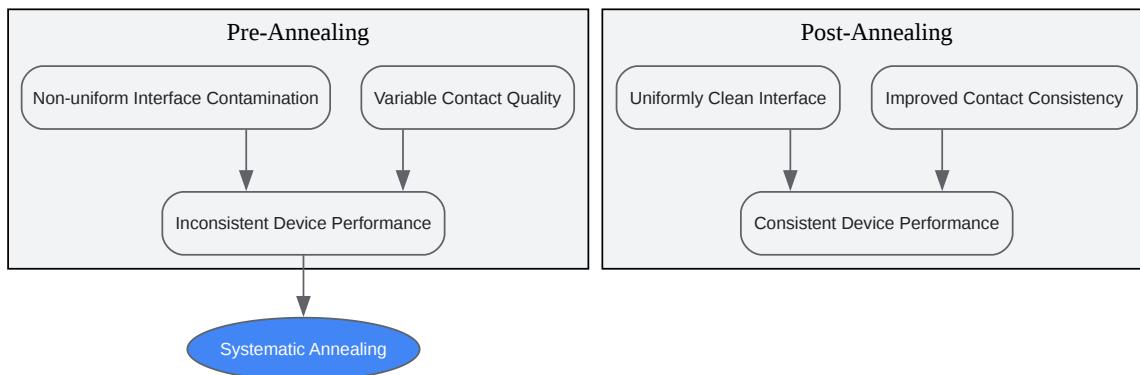

## Issue 3: Inconsistent Device Performance Across a Wafer

Symptom: Devices fabricated on the same wafer exhibit significant variations in their electrical characteristics.

Possible Cause: Non-uniformity in the interfacial cleanliness or the quality of the 2D material transfer across the substrate.

Annealing Strategy:

- Protocol: A systematic annealing process can help to improve the uniformity of the devices by promoting more consistent interfacial properties.

- Logical Relationship Diagram:

[Click to download full resolution via product page](#)

**Fig. 2:** Impact of annealing on device performance consistency.

## Key Experimental Protocols

### Protocol 1: Forming Gas Annealing for Contact Improvement

- System Preparation: Ensure the annealing furnace is clean and can be purged with high-purity forming gas (e.g., 5% H<sub>2</sub> in Ar).

- Sample Loading: Place the device on a clean quartz boat and load it into the center of the furnace tube.

- Purging: Purge the tube with the forming gas for at least 30 minutes to remove any residual oxygen and moisture.

- Heating: Ramp the temperature to the desired setpoint (e.g., 300°C) at a controlled rate (e.g., 10°C/min).

- Annealing: Hold the temperature for the specified duration (e.g., 3 hours).

- Cooling: Turn off the heater and allow the furnace to cool down naturally to room temperature while maintaining the forming gas flow.

- Unloading: Once at room temperature, stop the gas flow and carefully remove the sample.

#### Protocol 2: UHV Annealing for Bubble Reduction

- System Preparation: The UHV chamber should be baked out to achieve a base pressure of at least  $10^{-6}$  mbar.

- Sample Loading: Mount the sample on a UHV-compatible sample holder and transfer it into the main chamber.

- Heating: Use a resistive or radiative heater to slowly ramp the sample temperature to the target value (e.g., 300°C). Monitor the pressure to ensure it does not rise excessively due to outgassing.

- Annealing: Maintain the target temperature for the desired duration (e.g., 6-8 hours).

- Cooling: Slowly decrease the heater power to allow the sample to cool to room temperature.

- Unloading: Once cooled, the sample can be safely removed from the UHV chamber.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. researchgate.net [researchgate.net]

- 2. pubs.aip.org [pubs.aip.org]

- 3. pubs.acs.org [pubs.acs.org]

- 4. From Lab Curiosity to Industry-Ready: How CDimension is Making 2D Materials Work for the Future of Electronics [cdimension.com]

- 5. par.nsf.gov [par.nsf.gov]

- To cite this document: BenchChem. [Technical Support Center: Optimizing 2D Heterostructure Device Performance with Annealing]. BenchChem, [2025]. [Online PDF].

Available at: [<https://www.benchchem.com/product/b085603#annealing-strategies-for-optimizing-the-performance-of-2hic-based-devices>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

**Contact**

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)