# Applications of Tellurium Trioxide (TeO<sub>3</sub>) in Semiconductor Devices: Application Notes and Protocols

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Tellurium trioxide

Cat. No.: B085038

[Get Quote](#)

For Researchers, Scientists, and Drug Development Professionals

## Introduction

## Core Application: High-Performance p-Channel Transistors

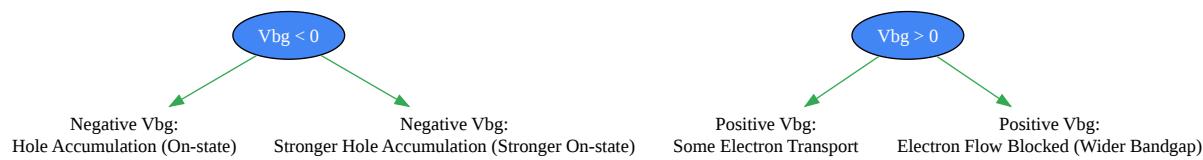

The development of high-performance p-channel transistors is a critical challenge in the advancement of complementary metal-oxide-semiconductor (CMOS) logic circuits. Amorphous TeO<sub>3</sub> has demonstrated breakthrough potential in this area by overcoming the limitations of traditional p-type semiconductor materials.[\[1\]](#)[\[2\]](#)[\[3\]](#)

Application Note:

Amorphous **tellurium trioxide** (a-TeO<sub>3</sub>), formed by the UV-ozone oxidation of two-dimensional (2D) tellurium, serves as the channel material in p-type field-effect transistors (FETs). This transformation from crystalline 2D-Te to a-TeO<sub>3</sub> induces a significant widening of the bandgap to approximately 3.04 eV and results in an exceptionally low Schottky barrier height of about 10 meV at the metal-semiconductor interface.[\[2\]](#)[\[3\]](#)[\[4\]](#) These properties lead to p-channel transistors with remarkable performance characteristics, including high hole mobility, superior on/off current ratios, and reduced hysteresis compared to their crystalline 2D-Te counterparts.[\[2\]](#)[\[5\]](#) The enhanced performance is attributed to the improved interface quality between the a-

TeO<sub>3</sub> channel and the gate dielectric.[2] This makes a-TeO<sub>3</sub> a promising candidate for next-generation, low-power, and high-speed electronic devices.[2][3]

## Quantitative Data Summary

The following table summarizes the key performance parameters of amorphous TeO<sub>3</sub>-based p-channel transistors as reported in the literature.

| Parameter                                                 | Value                   | Unit                | Reference(s) |

|-----------------------------------------------------------|-------------------------|---------------------|--------------|

| Material Properties of a-TeO <sub>3</sub>                 |                         |                     |              |

| Bandgap (Eg)                                              | ~3.04                   | eV                  | [2][4]       |

| Transistor Performance Metrics                            |                         |                     |              |

| Hole Mobility (μh)                                        | 238.6                   | cm <sup>2</sup> /Vs | [2]          |

| On/Off Current Ratio (I <sub>on</sub> /I <sub>off</sub> ) | 0.81 x 10 <sup>5</sup>  | -                   | [2]          |

| Schottky Barrier Height (SBH)                             | 10                      | meV                 | [2][3]       |

| Contact Resistance (R <sub>c</sub> )                      | 626.81                  | Ω·μm                | [2]          |

| Interface Trap Density                                    | 2.69 x 10 <sup>14</sup> | cm <sup>-2</sup>    | [2]          |

## Experimental Protocols

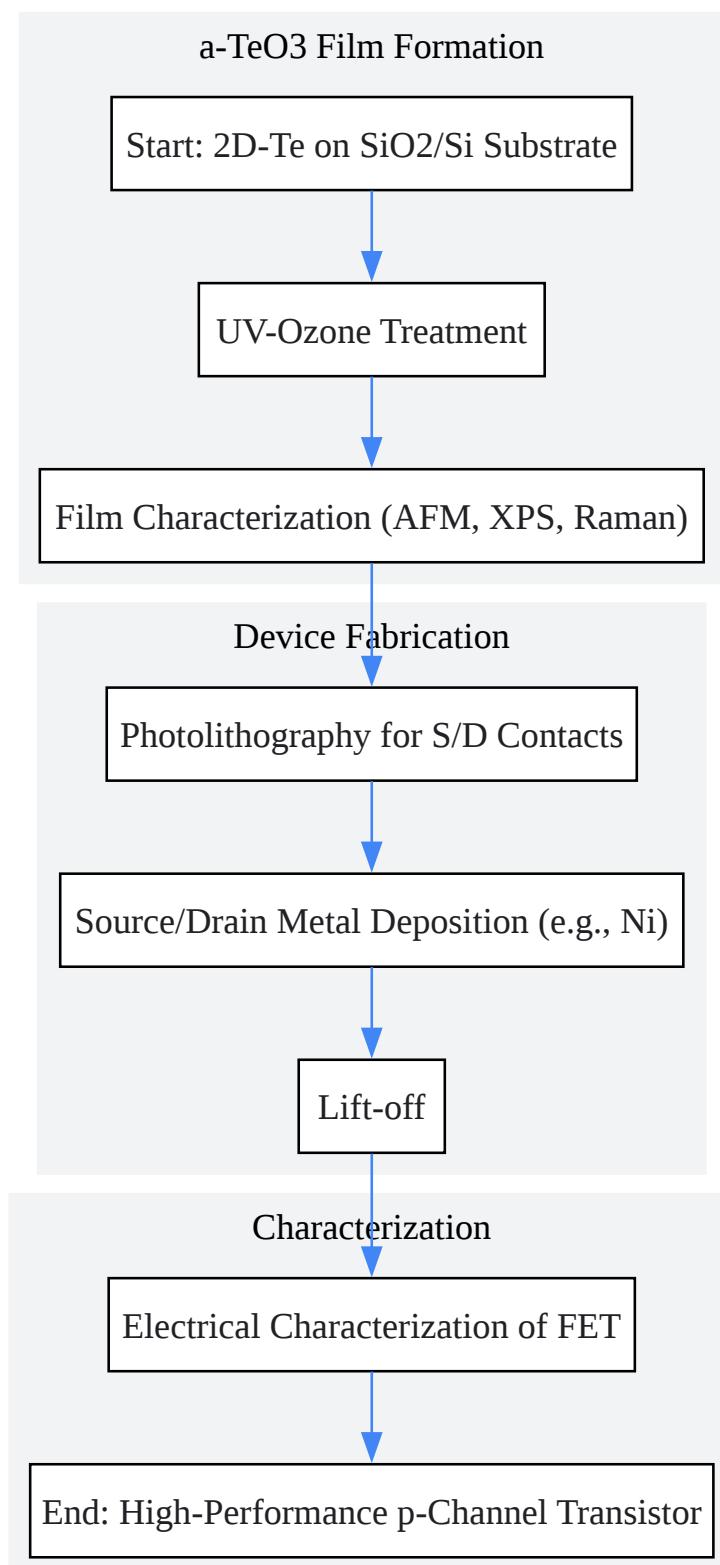

### Synthesis of Amorphous TeO<sub>3</sub> Thin Films via UV-Ozone Treatment of 2D Tellurium

This protocol describes the conversion of a crystalline 2D tellurium thin film into an amorphous TeO<sub>3</sub> thin film, which serves as the active channel in a p-type transistor.

Materials:

- 2D Tellurium (2D-Te) thin film (10-15 nm thickness) on a suitable substrate (e.g., SiO<sub>2</sub>/Si)[2]

- UV-Ozone cleaner

**Procedure:**

- Place the 2D-Te thin film sample inside the chamber of a UV-Ozone cleaner.

- Expose the sample to UV irradiation in the presence of ozone. The UV source should generate wavelengths that can produce ozone (e.g., 185 nm) and dissociate it (e.g., 254 nm).

- The duration of the treatment is a critical parameter. A 60-minute treatment has been shown to achieve complete transformation to a-TeO<sub>3</sub>.[5] The transformation can be monitored by observing the change in thickness; for example, an initial ~8 nm 2D-Te film increases to ~13.7 nm upon full conversion to a-TeO<sub>3</sub>.[5]

- After the treatment, the resulting amorphous TeO<sub>3</sub> thin film is ready for device fabrication.

**Characterization of the Transformation:**

- Atomic Force Microscopy (AFM): To monitor the change in film thickness and surface morphology.[5]

- X-ray Photoelectron Spectroscopy (XPS): To confirm the chemical composition and the formation of TeO<sub>3</sub> by observing the shifts in the Te 3d and O 1s core-level peaks.[5]

- Raman Spectroscopy: To verify the structural transformation from crystalline 2D-Te to amorphous TeO<sub>3</sub>. The characteristic peaks of 2D-Te will disappear, and a new vibrational mode for a-TeO<sub>3</sub> may emerge (e.g., around 618 cm<sup>-1</sup>).[2]

- High-Resolution Transmission Electron Microscopy (HRTEM): To directly visualize the amorphous nature of the TeO<sub>3</sub> layer and the interface with any remaining crystalline Te.[2][5]

## **Fabrication of an Amorphous TeO<sub>3</sub> p-Channel Field-Effect Transistor (FET)**

This protocol outlines the fabrication of a bottom-gate, top-contact p-channel FET using the a-TeO<sub>3</sub> film.

#### Materials:

- Substrate with pre-patterned gate electrode and dielectric (e.g., 90 nm SiO<sub>2</sub> on a heavily doped Si wafer, where the Si serves as the back gate)[2]

- Amorphous TeO<sub>3</sub> thin film on the substrate (prepared as in Protocol 1)

- Photoresist and developer for lithography

- Metal for source and drain contacts (e.g., Nickel)[6]

- Metal deposition system (e.g., thermal evaporator or e-beam evaporator)

- Lift-off solvent (e.g., acetone)

#### Procedure:

- Substrate Preparation: Start with a clean substrate, typically a highly doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer to act as the gate dielectric.[2]

- a-TeO<sub>3</sub> Formation: Grow or transfer a 2D-Te thin film onto the SiO<sub>2</sub>/Si substrate and subsequently convert it to a-TeO<sub>3</sub> using the UV-Ozone treatment described in Protocol 1.

- Photolithography for Source/Drain Contacts:

- Spin-coat a layer of photoresist onto the a-TeO<sub>3</sub> film.

- Use a photomask to define the source and drain contact regions.

- Expose the photoresist to UV light through the mask.

- Develop the photoresist to create openings for metal deposition.

- Metal Deposition:

- Deposit the source and drain contact metal (e.g., Ni) using a suitable deposition technique like thermal evaporation.[6]

- Lift-off:

- Immerse the sample in a solvent (e.g., acetone) to dissolve the remaining photoresist, lifting off the excess metal and leaving the patterned source and drain electrodes.

- Annealing (Optional): A post-fabrication annealing step may be performed to improve the contact quality.

#### Device Characterization:

- Electrical Measurements: Use a semiconductor parameter analyzer to measure the output and transfer characteristics (IDS-VDS and IDS-VGS) of the fabricated FET. From these measurements, key performance metrics such as hole mobility, on/off ratio, subthreshold swing, and threshold voltage can be extracted.[5]

## Visualizations

### Experimental Workflow for a-TeO<sub>3</sub> p-Channel Transistor Fabrication

[Click to download full resolution via product page](#)

Caption: Workflow for fabricating an amorphous  $\text{TeO}_3$  p-channel transistor.

# Signaling Pathway: Carrier Transport in a-TeO<sub>3</sub> vs. 2D-Te Transistors

[Click to download full resolution via product page](#)

Caption: Carrier transport comparison in 2D-Te and a-TeO<sub>3</sub> transistors.

## Other Potential Applications (Limited Data)

While the application of a-TeO<sub>3</sub> in p-channel transistors is the most well-documented, other potential uses of tellurium oxides in semiconductor devices are being explored, though with less specific data available for TeO<sub>3</sub>.

- **Gate Dielectric:** Due to its oxide nature, TeO<sub>3</sub> could potentially be used as a gate dielectric material. However, current research has focused more on the self-forming TiO<sub>x</sub>-Te gate dielectric in tellurium-based transistors, where a thin layer of native TeO<sub>x</sub> is reduced during the deposition of titanium.<sup>[7]</sup> Further investigation is needed to evaluate the dielectric properties of pure TeO<sub>3</sub> films for this purpose.

- **Gas Sensors:** While there is research on tellurium dioxide (TeO<sub>2</sub>) nanowires for gas sensing applications, specific studies on the use of TeO<sub>3</sub> for gas sensors are not prevalent in the current literature.<sup>[8]</sup>

- **Memory Devices:** Tellurium-based materials are key components in phase-change memory (PCM) devices. However, these typically involve telluride alloys (e.g., Ge-Sb-Te) rather than pure **tellurium trioxide**.

## Conclusion

**Tellurium trioxide**, particularly in its amorphous form, has demonstrated significant promise for advancing semiconductor technology, most notably in the development of high-performance p-channel transistors. The protocols and data presented here provide a foundation for researchers to explore and build upon the current understanding of this emerging material. Further research into scalable synthesis methods and the exploration of other potential applications, such as in gate dielectrics, will be crucial for realizing the full potential of  $\text{TeO}_3$  in next-generation electronic devices.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. openresearch-repository.anu.edu.au [openresearch-repository.anu.edu.au]

- 2. High Performance P-Channel Transistor Based on Amorphous Tellurium Trioxide - PMC [pmc.ncbi.nlm.nih.gov]

- 3. High Performance P-Channel Transistor Based on Amorphous Tellurium Trioxide - PubMed [pubmed.ncbi.nlm.nih.gov]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. Selenium-alloyed tellurium oxide for amorphous p-channel transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 7. Ultralow Voltage Operation of p- and n-FETs Enabled by Self-Formed Gate Dielectric and Metal Contacts on 2D Tellurium - PMC [pmc.ncbi.nlm.nih.gov]

- 8. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Applications of Tellurium Trioxide ( $\text{TeO}_3$ ) in Semiconductor Devices: Application Notes and Protocols]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b085038#applications-of-teo3-in-semiconductor-devices>

---

#### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)