# Technical Support Center: Minimizing Junction Leakage in NiSi-Contacted Devices

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Nickel;silicon

Cat. No.: B084514

[Get Quote](#)

Welcome to the technical support center for researchers and scientists working with Nickel Silicide (NiSi) contacted devices. This resource provides troubleshooting guides and answers to frequently asked questions (FAQs) to help you diagnose and resolve issues related to junction leakage during your experiments.

## Frequently Asked Questions (FAQs) & Troubleshooting Guides

### Q1: What are the primary causes of high junction leakage in our NiSi-contacted devices?

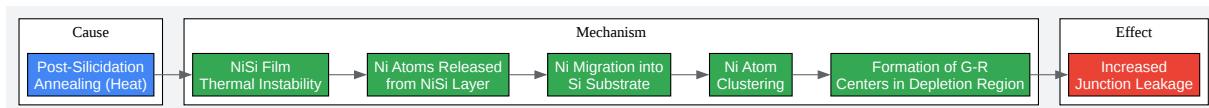

A1: High junction leakage in NiSi-contacted devices typically originates from several key mechanisms. Understanding these root causes is the first step in troubleshooting.

- Nickel (Ni) Diffusion and Defect Formation: The primary cause is often the thermal instability of the NiSi film, especially during post-silicidation annealing.<sup>[1][2][3][4]</sup> This instability allows Ni atoms to be released from the silicide layer and diffuse into the silicon substrate. These migrant Ni atoms can then cluster and form generation-recombination (G-R) centers deep within the Si, significantly increasing leakage current.<sup>[1][4]</sup>

- Abnormal Silicide Growth: Leakage can be caused by the formation of silicide spikes (e.g., NiSi<sub>2</sub>) or the lateral encroachment of the silicide into the junction region.<sup>[1][5]</sup> These

structural anomalies can create localized high-field regions or shorting paths, leading to excessive leakage.

- Interface Quality: A rough or non-uniform NiSi/Si interface can contribute to higher leakage. [1][6] The presence of crystal defects at or near the interface can also act as leakage pathways.[1][5]

- Process-Induced Damage: Residual damage from processes like ion implantation, if not fully annealed, can introduce defects that increase junction leakage.[4]

## Q2: We are observing a significant increase in leakage current after our post-silicidation annealing step. What is happening and how can we fix it?

A2: This is a common issue directly related to the thermal stability of the NiSi film. The thermal energy from the anneal promotes the dissociation of Ni atoms from the NiSi layer and their subsequent diffusion into the silicon, creating leakage-inducing defects.[1][2][4]

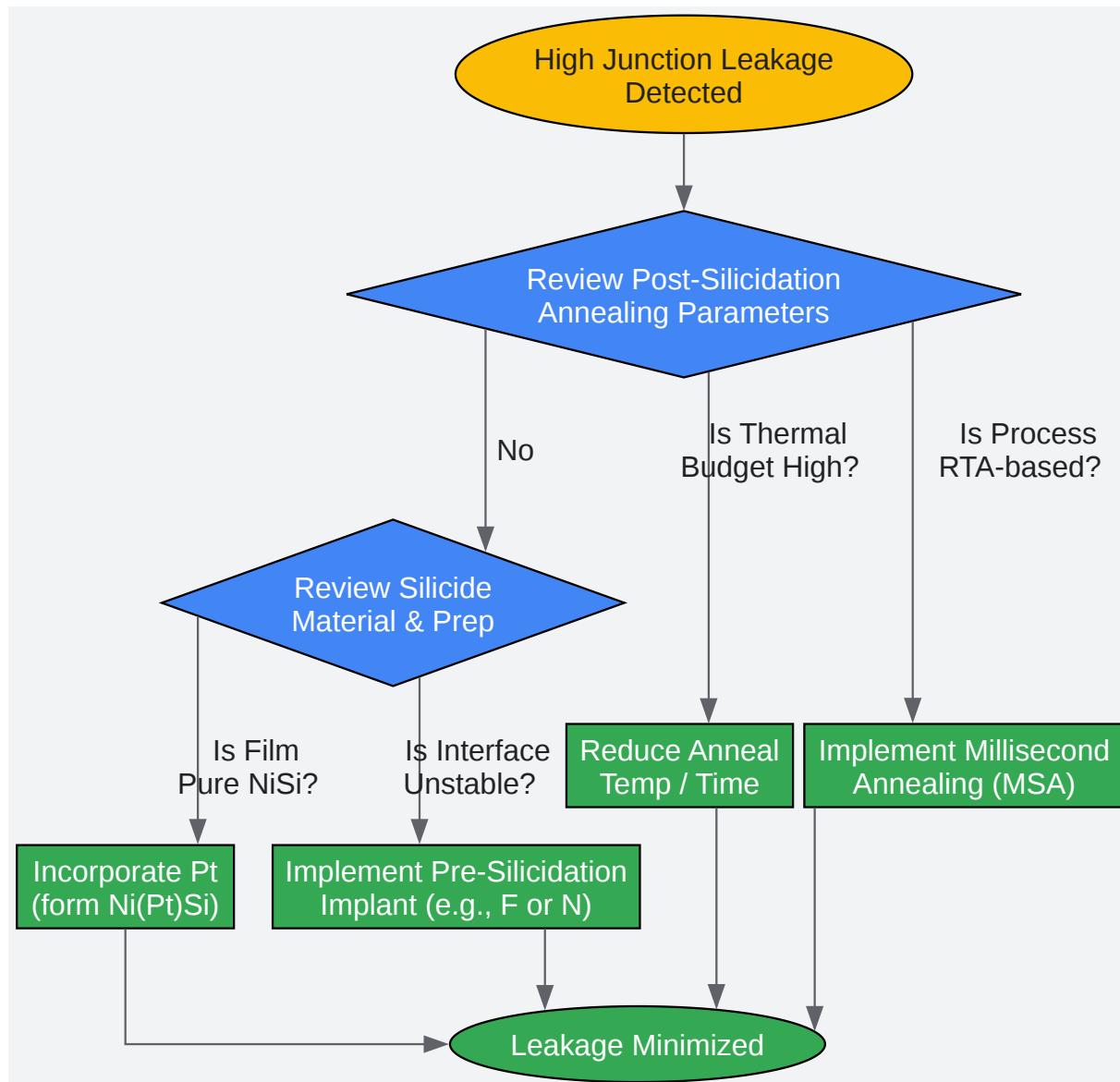

Troubleshooting Steps:

- Optimize Annealing Parameters:

- Reduce Thermal Budget: A consistent rise in leakage is observed with increased annealing time and temperature.[1][4] Reduce the temperature and/or duration of your post-silicidation anneal to minimize Ni diffusion.

- Consider Millisecond Annealing (MSA): MSA techniques provide a very high temperature anneal for an extremely short duration (e.g., 1 ms). This has been shown to effectively reduce Ni diffusion and lower junction leakage by approximately 50% compared to conventional Rapid Thermal Annealing (RTA).[7][8]

- Improve Silicide Thermal Stability:

- Incorporate Platinum (Pt): Alloying Ni with Pt (typically ~5-10%) to form Ni(Pt)Si significantly enhances the thermal stability of the silicide film.[1] The presence of Pt can reduce the generation of NiSi defects in the Si substrate and suppress the excessive diffusion of Ni.[1][9]

- Pre-Silicidation Implantation (PSI): Implanting certain elements into the silicon substrate before Ni deposition can stabilize the resulting NiSi film. Fluorine (F) implantation, in particular, has been shown to be highly effective, suppressing leakage by up to six orders of magnitude by passivating the NiSi/Si interface.[1][10]

### Q3: How does Pre-Amorphization Implantation (PAI) affect junction leakage?

A3: Pre-Amorphization Implantation (PAI) is a technique where the silicon substrate is implanted with a heavy, neutral ion (like Germanium or Xenon) to create a thin amorphous layer before subsequent processing steps.[11]

- Function: The primary goal of PAI is to prevent ion channeling during the source/drain dopant implantation, which allows for the formation of shallower and more abrupt junctions.[11]

- Impact on Leakage: In the context of NiSi, PAI can be beneficial. A cold Si PAI, for instance, has been shown to suppress the agglomeration of the NiSi film at elevated temperatures.[12] By ensuring a more uniform and stable silicide formation, PAI indirectly helps in maintaining low junction leakage. However, it is critical that the end-of-range (EOR) damage created by the PAI is fully annealed out, as residual defects can themselves become a source of leakage.[13]

### Q4: We need to choose a pre-silicidation implant (PSI) species. Is Fluorine (F) or Nitrogen (N) better for leakage suppression?

A4: Both Fluorine (F) and Nitrogen (N) pre-silicidation implants (PSI) can reduce junction leakage, but their effectiveness depends on the silicon crystal orientation and their underlying mechanisms differ.[10]

- Fluorine (F) PSI: F-PSI is exceptionally effective, especially on standard Si(100) substrates. [10] Its leakage suppression mechanism is primarily attributed to the passivation of the incoherent and unstable NiSi/Si(100) interface.[1][10]

- Nitrogen (N) PSI: The effectiveness of N-PSI is more pronounced on Si(110) substrates.[10] Nitrogen is thought to stabilize the abundant grain boundaries of the highly oriented NiSi

films that form on Si(110).[\[1\]](#)[\[10\]](#)

Recommendation:

- For devices on Si(100) substrates, Fluorine (F) PSI is the superior choice for drastic leakage reduction.[\[10\]](#)

- For devices on Si(110) substrates, Nitrogen (N) PSI is a very effective and complementary option to consider.[\[1\]](#)[\[10\]](#)

## Quantitative Data Summary

The following tables summarize key quantitative data from referenced experiments on controlling NiSi junction leakage.

Table 1: Effect of Annealing Technique on nMOS Junction Leakage

| Annealing Method | Temperature / Time | Relative Junction Leakage | Source(s)           |

|------------------|--------------------|---------------------------|---------------------|

| RTA (Reference)  | 420 °C for 20 s    | ~ 1.0 (Normalized)        | <a href="#">[8]</a> |

| MSA              | 750 °C for 1 ms    | ~ 0.5                     | <a href="#">[8]</a> |

| MSA              | 800 °C for 1 ms    | ~ 0.5                     | <a href="#">[8]</a> |

| MSA              | 850 °C for 1 ms    | ~ 0.5                     | <a href="#">[8]</a> |

| MSA              | 900 °C for 1 ms    | ~ 0.5                     | <a href="#">[8]</a> |

Note: MSA demonstrates a ~50% reduction in leakage current compared to conventional RTA due to the efficient suppression of Ni diffusion.[\[8\]](#)

Table 2: Impact of Post-Annealing on Leakage in Shallow Junctions ( $x_j \approx 61\text{nm}$ )

| Post-Annealing Temperature | Post-Annealing Time | Leakage Current Density (A/cm <sup>2</sup> ) at 4V Reverse Bias | Source(s) |

|----------------------------|---------------------|-----------------------------------------------------------------|-----------|

| 450 °C                     | 30 min              | ~ 1 x 10 <sup>-9</sup>                                          | [2]       |

| 500 °C                     | 10 min              | ~ 1 x 10 <sup>-7</sup>                                          | [2]       |

| 500 °C                     | 30 min              | ~ 1 x 10 <sup>-6</sup>                                          | [2]       |

| 500 °C                     | 90 min              | ~ 1 x 10 <sup>-5</sup>                                          | [2]       |

Note: A significant increase in leakage is observed at 500°C, highlighting the thermal instability of NiSi even at typical temperatures for interlayer dielectric deposition.[2][3]

## Diagrams & Workflows

[Click to download full resolution via product page](#)

Caption: Mechanism of thermally-induced junction leakage in NiSi devices.

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for high junction leakage.

## Experimental Protocols

## Protocol 1: Fabrication of Damage-Free Junctions for Intrinsic Leakage Analysis

This protocol describes a method to create n+/p junctions that are free from heavy implantation damage, allowing for the sensitive measurement of leakage currents caused intrinsically by the NiSi film itself.[\[2\]](#)[\[3\]](#)[\[4\]](#)

**Objective:** To isolate and study the leakage mechanisms inherent to the NiSi/Si interface and thermal processing, independent of process-induced defects from high-dose implantation.

**Methodology:**

- **Substrate Preparation:** Start with p-type Si (100) or (110) wafers with a flat p-well concentration (e.g.,  $2 \times 10^{17} \text{ cm}^{-3}$ ).

- **Junction Delineation:**

- Deposit a pad oxide layer (e.g., TEOS) followed by a silicon nitride (SiN) film.

- Use photolithography and reactive-ion etching (RIE) to pattern the SiN, stopping on the pad oxide.

- Wet etch the underlying pad oxide to define the junction area without exposing the Si substrate to plasma damage.

- **n+ Region Formation (Solid Phase Diffusion):**

- Deposit an arsenic-doped silicate glass (AsSG) layer to act as the dopant source.

- Perform a drive-in anneal to diffuse arsenic from the AsSG into the silicon, forming the n+ region. The junction depth ( $x_j$ ) can be precisely controlled by adjusting the anneal time and temperature.[\[3\]](#)

- **Sidewall Formation:**

- Remove the AsSG layer by wet etching.

- Deposit a second SiN film and use an anisotropic RIE process to form SiN sidewalls. This step is crucial to guard the junction perimeter against anomalous leakage.[2][3]

- Silicide Formation:

- Perform a final wet etch to remove the pad oxide from the active junction area.

- Sputter deposit a thin layer of Ni (and Pt, if forming Ni(Pt)Si).

- Perform the silicidation anneal (e.g., RTA or MSA) to form the NiSi phase (typically ~30 nm thick).

- Selectively wet etch to remove any unreacted metal from the surface.

- Characterization: The resulting structure has the NiSi film well-contained within the damage-free, diffused n+ region, allowing for accurate measurement of areal junction leakage.[2][3]

## Protocol 2: Pre-Silicidation Implantation (PSI) for Leakage Suppression

This protocol outlines the general steps for incorporating a Fluorine (F) or Nitrogen (N) implant prior to silicidation to enhance thermal stability and reduce leakage.[10]

**Objective:** To improve the thermal stability of the NiSi film and passivate the NiSi/Si interface, thereby suppressing thermally-induced junction leakage.

**Methodology:**

- Junction Formation: Fabricate the source/drain junctions up to the point just before metal deposition for silicidation. This can be done using the damage-free method described above or a standard implantation and activation anneal process.

- Pre-Silicidation Implant (PSI):

- Load the wafers into an ion implanter.

- Implant the desired species (e.g., F<sup>+</sup> or N<sup>+</sup>) into the silicon.

- Key Parameters:

- Energy: The implant energy must be low enough to confine the implanted species near the surface where the silicide will be formed.

- Dose: The dose must be optimized. An insufficient dose will be ineffective, while an excessive dose can introduce damage that increases leakage.

- Pre-Cleaning: Perform a standard pre-clean (e.g., with dilute HF) immediately before Ni deposition to remove the native oxide.

- Silicidation:

- Immediately transfer the wafers to a deposition tool and sputter a thin film of Ni.

- Perform the silicidation anneal (e.g., RTA) to form the NiSi layer.

- Strip the unreacted metal.

- Post-Silicide Processing: Proceed with subsequent processing steps, such as interlayer dielectric deposition and contact formation. The PSI step should make the junction more robust against the thermal budget of these later steps.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [researchgate.net](#) [researchgate.net]

- 2. [confit.atlas.jp](#) [confit.atlas.jp]

- 3. [confit.atlas.jp](#) [confit.atlas.jp]

- 4. [researchgate.net](#) [researchgate.net]

- 5. Analysis of Junction Leakage Current Failure of Nickel Silicide Abnormal Growth Using Advanced Transmission Electron Microscopy | IEEE Journals & Magazine | IEEE Xplore

[ieeexplore.ieee.org]

- 6. researchgate.net [researchgate.net]

- 7. Effect of Millisecond Annealing Temperature of Ni<sub>1-x</sub>Pt<sub>x</sub> Si Formation on Leakage Current Characteristics of Static Random- Access Memory Cells | Semantic Scholar [semanticscholar.org]

- 8. Effect of Millisecond Annealing Temperature of Ni<sub>1-x</sub>Pt<sub>x</sub> Si Formation on Leakage Current Characteristics of Static Random- Access Memory Cells | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 9. pubs.aip.org [pubs.aip.org]

- 10. researchgate.net [researchgate.net]

- 11. axcelis.com [axcelis.com]

- 12. Cold Silicon Preamorphization Implant and Presilicide Sulfur Implant for Advanced Nickel Silicide Contacts | Semantic Scholar [semanticscholar.org]

- 13. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Minimizing Junction Leakage in NiSi-Contacted Devices]. BenchChem, [2025]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b084514#minimizing-junction-leakage-in-nisi-contacted-devices\]](https://www.benchchem.com/product/b084514#minimizing-junction-leakage-in-nisi-contacted-devices)

---

#### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)