# Application Notes and Protocols for Nickel Silicide in Semiconductor Fabrication

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Nickel;silicon

Cat. No.: B084514

[Get Quote](#)

For Researchers, Scientists, and Drug Development Professionals

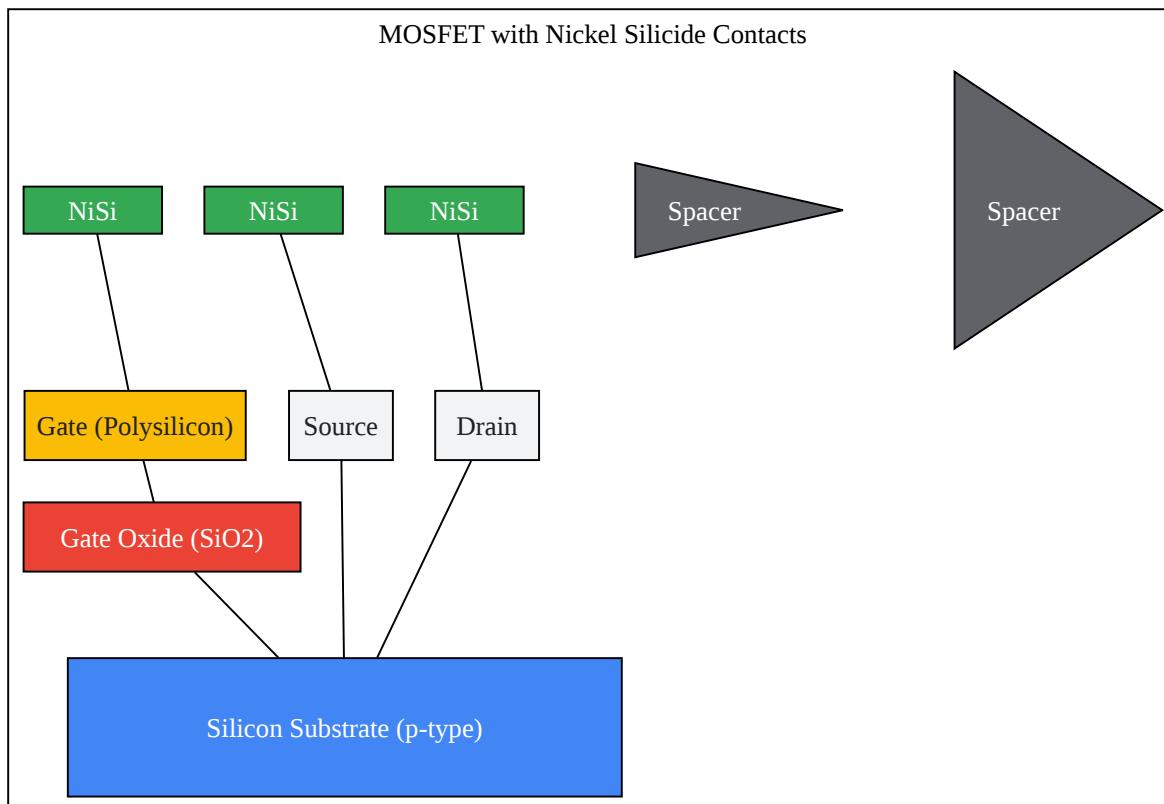

These application notes provide a comprehensive overview and detailed protocols for the utilization of nickel silicide (NiSi) for source, drain, and gate contacts in semiconductor device fabrication. Nickel silicide has emerged as a critical material in advanced complementary metal-oxide-semiconductor (CMOS) technologies due to its low electrical resistivity, reduced silicon consumption compared to other silicides, and favorable formation process.[\[1\]](#)[\[2\]](#)

## Introduction to Nickel Silicide Contacts

Nickel silicide is employed to reduce the parasitic resistance at the source, drain, and gate contacts of transistors, a crucial step in enhancing device performance.[\[1\]](#)[\[2\]](#) The formation of a low-resistance silicide layer is typically achieved through a self-aligned silicide (salicide) process, where a deposited nickel film reacts with the underlying silicon in the active regions of the device.[\[3\]](#)[\[4\]](#)

Key Advantages of Nickel Silicide:

- Low Resistivity: The NiSi phase exhibits low electrical resistivity, comparable to other commonly used silicides like titanium silicide (TiSi<sub>2</sub>) and cobalt silicide (CoSi<sub>2</sub>).[\[4\]](#)[\[5\]](#)

- Low Silicon Consumption: The formation of NiSi consumes less silicon from the substrate compared to TiSi<sub>2</sub> and CoSi<sub>2</sub>, which is advantageous for the fabrication of ultra-shallow junctions in scaled-down devices.[\[1\]](#)[\[2\]](#)

- Reduced Linewidth Dependency: The sheet resistance of NiSi is less dependent on the linewidth of the contact, making it suitable for nanoscale devices.[6]

- Low Formation Temperature: NiSi can be formed at relatively low temperatures, which helps in minimizing the thermal budget of the overall fabrication process.[1][2]

#### Challenges:

- Thermal Stability: One of the main challenges with NiSi is its thermal stability. At elevated temperatures, the low-resistivity NiSi phase can transform into the higher-resistivity nickel disilicide (NiSi<sub>2</sub>) phase or agglomerate, leading to increased contact resistance and device degradation.[7][8]

- Process Control: The formation of a uniform and stable NiSi layer requires precise control over process parameters such as annealing temperature, time, and ambient conditions.[1]

## Data Presentation: Properties of Nickel Silicide

The following tables summarize key quantitative data for different phases of nickel silicide, compiled from various research findings.

Table 1: Electrical Resistivity of Nickel Silicide Phases

| Silicide Phase                    | Electrical Resistivity<br>( $\mu\Omega\cdot\text{cm}$ ) | Reference |

|-----------------------------------|---------------------------------------------------------|-----------|

| NiSi                              | 10.5–18                                                 | [9]       |

| Ni <sub>2</sub> Si                | 24–30                                                   | [9]       |

| NiSi <sub>2</sub>                 | 34–50                                                   | [9]       |

| Ni <sub>31</sub> Si <sub>12</sub> | 90–150                                                  | [9]       |

Table 2: Sheet Resistance of Nickel Silicide Films under Various Conditions

| Initial Ni Thickness        | Annealing Conditions | Resulting Phase       | Sheet Resistance ( $\Omega/\text{sq}$ ) | Reference |

|-----------------------------|----------------------|-----------------------|-----------------------------------------|-----------|

| 30 nm                       | RTA, various temps   | NiSi                  | ~10 - 20 (at 400-600°C)                 | [10]      |

| 5 nm                        | 500°C, 10 s          | NiSi                  | ~16.5 (specific resistivity)            | [11]      |

| 3 nm                        | >450°C               | epi-NiSi <sub>2</sub> | ~45.0 (specific resistivity)            | [11]      |

| 25 nm with Zn interlayer    | 300-600°C            | NiSi                  | ~2.5                                    | [12]      |

| 25 nm with Ta/Ti interlayer | 450-650°C            | NiSi                  | 12-15                                   | [12]      |

Table 3: Formation Temperatures of Nickel Silicide Phases

| Silicide Phase     | Typical Formation Temperature Range (°C) | Reference |

|--------------------|------------------------------------------|-----------|

| Ni <sub>2</sub> Si | 200–350                                  | [7]       |

| NiSi               | 400–550                                  | [7]       |

| NiSi <sub>2</sub>  | >650                                     | [7]       |

## Experimental Protocols

This section outlines the detailed methodologies for the formation and characterization of nickel silicide contacts.

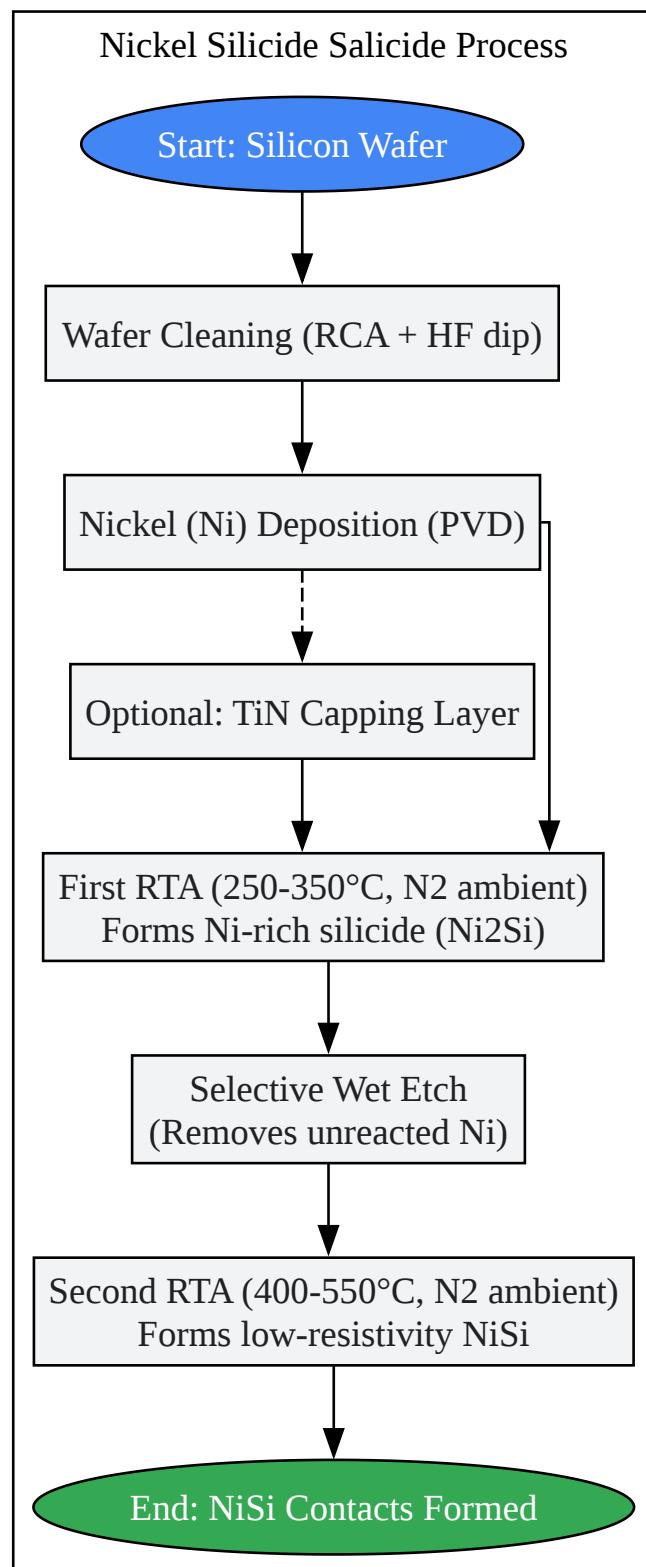

### Protocol for Nickel Silicide Formation (Two-Step Salicide Process)

This protocol describes a widely used two-step rapid thermal annealing (RTA) process to form self-aligned nickel silicide contacts on a silicon substrate.

#### Materials and Equipment:

- Silicon wafers (p-type or n-type)

- Nickel (Ni) sputtering target

- Titanium Nitride (TiN) sputtering target (optional, for capping layer)

- Rapid Thermal Annealing (RTA) system with N<sub>2</sub> ambient

- Wet etching station with a selective etchant for unreacted nickel (e.g., a mixture of sulfuric acid (H<sub>2</sub>SO<sub>4</sub>) and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>))

- Deionized (DI) water rinse station

- Standard wafer cleaning solutions (e.g., RCA clean)

#### Procedure:

- Wafer Cleaning:

- Perform a standard pre-deposition clean of the silicon wafers to remove any organic and metallic contaminants. An RCA clean is recommended.

- Immediately before loading into the deposition system, perform a brief dip in a dilute hydrofluoric acid (HF) solution to remove the native oxide layer.

- Nickel Deposition:

- Transfer the cleaned wafers to a physical vapor deposition (PVD) or sputtering system.

- Deposit a thin film of nickel onto the wafer surface. The thickness of the nickel layer will determine the final silicide thickness (typically 10-20 nm of Ni).

- (Optional) Deposit a thin capping layer of TiN on top of the nickel film. This can help prevent oxidation of the nickel during the subsequent annealing step.[1]

- First Rapid Thermal Anneal (RTA1):

- Transfer the wafers to the RTA system.

- Perform the first anneal in a nitrogen (N<sub>2</sub>) ambient to form the high-resistivity Ni-rich silicide phase (Ni<sub>2</sub>Si).

- Typical RTA1 conditions are in the range of 250°C to 350°C for 30-60 seconds.[7][13] The exact temperature and time should be optimized based on the specific process and desired outcome.

- Selective Etching:

- After RTA1, remove the wafers from the RTA system.

- Submerge the wafers in a selective wet etch solution to remove the unreacted nickel from the oxide or nitride regions, leaving the nickel silicide only in the areas where nickel was in direct contact with silicon. A common etchant is a solution of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub>.[1]

- Rinse the wafers thoroughly with DI water and dry them.

- Second Rapid Thermal Anneal (RTA2):

- Return the wafers to the RTA system.

- Perform the second anneal at a higher temperature to convert the Ni-rich silicide into the low-resistivity NiSi phase.

- Typical RTA2 conditions are in the range of 400°C to 550°C for 30-60 seconds in a N<sub>2</sub> ambient.[7][8]

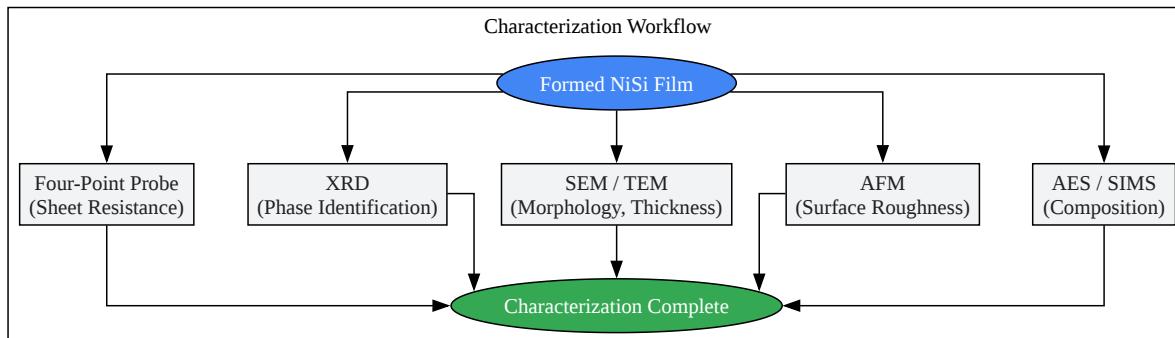

## Protocol for Characterization of Nickel Silicide Films

This protocol outlines the key techniques for characterizing the physical and electrical properties of the formed nickel silicide films.

**Equipment:**

- Four-Point Probe

- X-Ray Diffractometer (XRD)

- Scanning Electron Microscope (SEM)

- Transmission Electron Microscope (TEM)

- Atomic Force Microscope (AFM)

- Auger Electron Spectroscopy (AES) or Secondary Ion Mass Spectrometry (SIMS)

**Procedures:**

- Sheet Resistance Measurement:

- Use a four-point probe to measure the sheet resistance (Rs) of the silicide film at multiple points across the wafer to assess uniformity.[1][14]

- Phase Identification:

- Perform XRD analysis to identify the crystalline phases of the nickel silicide present in the film. This is crucial to confirm the formation of the desired NiSi phase.[1][14]

- Morphology and Thickness Analysis:

- Use SEM to visualize the surface morphology of the silicide film. Cross-sectional SEM can be used to estimate the film thickness.[14]

- For high-resolution imaging of the silicide/silicon interface and precise thickness measurements, use TEM.[1]

- AFM can be employed to characterize the surface roughness of the silicide film.[14][15]

- Compositional Analysis:

- Utilize AES or SIMS depth profiling to determine the elemental composition of the film and to check for any contaminants or oxygen at the interface.[15][16]

## Visualizations

The following diagrams illustrate key processes and structures related to the use of nickel silicide in semiconductor devices.

[Click to download full resolution via product page](#)

### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [jos.ac.cn](http://jos.ac.cn) [jos.ac.cn]

- 2. [repository.rit.edu](http://repository.rit.edu) [repository.rit.edu]

- 3. [researchgate.net](http://researchgate.net) [researchgate.net]

- 4. US20030235973A1 - Nickel SALICIDE process technology for CMOS devices - Google Patents [patents.google.com]

- 5. [researchgate.net](http://researchgate.net) [researchgate.net]

- 6. [researchgate.net](http://researchgate.net) [researchgate.net]

- 7. [osti.gov](http://osti.gov) [osti.gov]

- 8. [researchgate.net](http://researchgate.net) [researchgate.net]

- 9. Nickel silicide - Wikipedia [en.wikipedia.org]

- 10. researchgate.net [researchgate.net]

- 11. researchgate.net [researchgate.net]

- 12. davidpublisher.com [davidpublisher.com]

- 13. US6362095B1 - Nickel silicide stripping after nickel silicide formation - Google Patents [patents.google.com]

- 14. gcris.iyte.edu.tr [gcris.iyte.edu.tr]

- 15. science24.com [science24.com]

- 16. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols for Nickel Silicide in Semiconductor Fabrication]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b084514#using-nickel-silicide-for-source-drain-and-gate-contacts>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)