# Application Notes and Protocols: Titanium Silicide (TiSi<sub>2</sub>) for Integrated Circuit Interconnects

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Titanium disilicide*

Cat. No.: *B078298*

[Get Quote](#)

Audience: Researchers, scientists, and engineering professionals in microelectronics and materials science.

**Abstract:** Titanium silicide (TiSi<sub>2</sub>) is a critical material in the fabrication of integrated circuits (ICs), primarily used to reduce the parasitic resistance of polysilicon gates and source/drain regions. Its low resistivity, high thermal stability, and compatibility with the self-aligned silicide (salicide) process have made it a cornerstone in semiconductor manufacturing for several technology generations.<sup>[1][2][3]</sup> These notes provide a comprehensive overview of the properties, formation protocols, and characterization of TiSi<sub>2</sub> thin films for interconnect applications.

## Introduction to Titanium Silicide in ICs

As the dimensions of transistors in integrated circuits have scaled down, the resistance of interconnects has become a significant factor limiting device performance.<sup>[4][5]</sup> Polysilicon, the standard material for transistor gates, has a relatively high resistance, which leads to undesirable RC delays. To mitigate this, a low-resistance material is formed on top of the polysilicon gate and the source/drain regions. Refractory metal silicides, such as TiSi<sub>2</sub>, are ideal for this application due to their low resistivity and stability at high processing temperatures.<sup>[6]</sup>

The salicide (self-aligned silicide) process is a key technology that enables the formation of these contacts without requiring additional photolithography steps.[\[7\]](#)[\[8\]](#) In this process, a thin film of titanium is deposited over a fully formed transistor. Upon heating, the titanium reacts with the exposed silicon of the gate, source, and drain to form  $\text{TiSi}_2$ .[\[9\]](#) The unreacted titanium over the insulating oxide regions is then selectively etched away, leaving silicide contacts only where they are needed.[\[7\]](#)

## Properties of Titanium Silicide ( $\text{TiSi}_2$ ) Phases

Titanium silicide exists in two primary crystalline phases, which have significantly different electrical properties. The formation of the correct phase is critical for its application in ICs.[\[1\]](#)

[\[10\]](#)

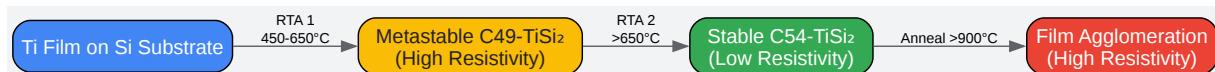

- C49- $\text{TiSi}_2$  (Metastable Phase): This is the first phase to form at lower annealing temperatures, typically between 450°C and 650°C.[\[1\]](#)[\[6\]](#) It has a base-centered orthorhombic crystal structure and a relatively high electrical resistivity, making it unsuitable for low-resistance contacts.[\[11\]](#)[\[12\]](#)

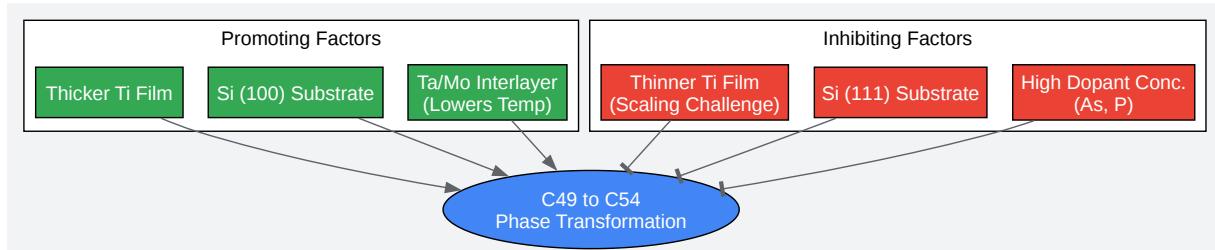

- C54- $\text{TiSi}_2$  (Stable Phase): A second, higher-temperature anneal (typically >650°C) is required to transform the C49 phase into the stable C54 phase.[\[1\]](#)[\[6\]](#) This phase has a face-centered orthorhombic structure and a much lower resistivity, which is essential for high-performance interconnects.[\[11\]](#)[\[12\]](#) The C49 to C54 transformation is a nucleation-and-growth process.[\[13\]](#)

The process window for forming the C54 phase is critical; temperatures above 900°C can lead to agglomeration of the  $\text{TiSi}_2$  film, where it becomes discontinuous and its resistance increases.

[\[1\]](#)[\[9\]](#)

## Data Presentation: Properties of $\text{TiSi}_2$ and Other Silicides

Table 1: Electrical and Physical Properties of  $\text{TiSi}_2$  Phases

| Property              | C49-TiSi <sub>2</sub>             | C54-TiSi <sub>2</sub>             | Reference(s) |

|-----------------------|-----------------------------------|-----------------------------------|--------------|

| Crystal Structure     | Base-Centered Orthorhombic        | Face-Centered Orthorhombic        | [1][10]      |

| Formation Temperature | 450°C - 650°C                     | > 650°C                           | [1][6]       |

| Thin Film Resistivity | 60 - 70 $\mu\Omega\cdot\text{cm}$ | 12 - 24 $\mu\Omega\cdot\text{cm}$ | [1][11]      |

| Stability             | Metastable                        | Stable                            | [1]          |

| Silicon Consumption   | 2.27 nm Si per nm Ti              | 2.27 nm Si per nm Ti              | [1]          |

| Resulting Silicide Thickness | 2.51 nm Silicide per nm Ti | 2.51 nm Silicide per nm Ti | [1] |

Table 2: Comparison of Silicides for Interconnect Applications

| Property                | TiSi <sub>2</sub> (C54)                             | CoSi <sub>2</sub>                                   | NiSi                                                | Reference(s) |

|-------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------|

| Resistivity             | <b>12 - 24 <math>\mu\Omega\cdot\text{cm}</math></b> | <b>10 - 25 <math>\mu\Omega\cdot\text{cm}</math></b> | <b>14 - 20 <math>\mu\Omega\cdot\text{cm}</math></b> | [1]          |

| Thermal Stability on Si | Good (up to ~900°C)                                 | Good                                                | Poor                                                | [1]          |

| Mechanical Stress       | $(2 - 2.25) \times 10^{10}$ dyne/cm <sup>2</sup>    | $(8 - 10) \times 10^9$ dyne/cm <sup>2</sup>         | Low                                                 | [1]          |

| Silicon Consumption     | 0.904 nm Si / nm Silicide                           | 1.03 nm Si / nm Silicide                            | 0.82 nm Si / nm Silicide                            | [1]          |

| Reaction with SiO<sub>2</sub> | ~700°C | > 1000°C | ~600°C | [1] |

## Experimental Protocols

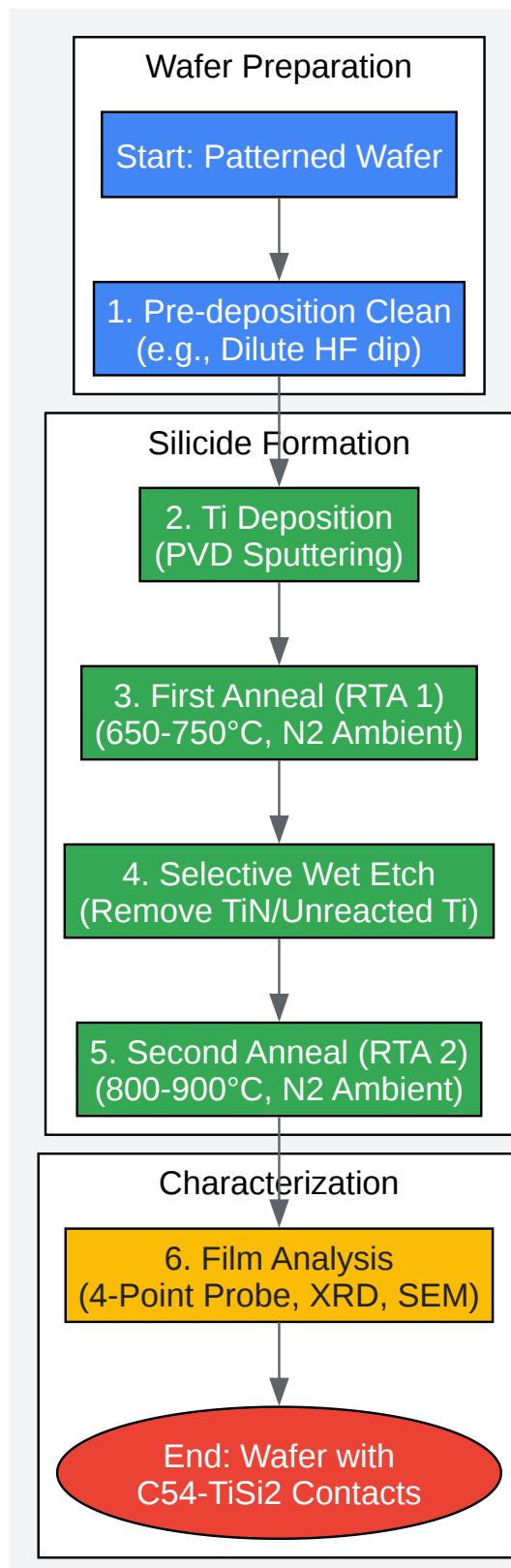

### Protocol 1: TiSi<sub>2</sub> Formation via Two-Step Salicide Process

This protocol describes a typical two-step rapid thermal annealing (RTA) process for forming self-aligned C54-TiSi<sub>2</sub> contacts on silicon wafers.

## Materials and Equipment:

- Silicon wafer with patterned active areas (source/drain/gate) and oxide isolation regions.

- Sputter deposition system (PVD).

- Rapid Thermal Annealing (RTA) system with nitrogen (N<sub>2</sub>) ambient control.

- Wet etching bench with selective etch solution (e.g., H<sub>2</sub>O<sub>2</sub>:NH<sub>4</sub>OH:H<sub>2</sub>O mixture).

- Deionized (DI) water.

## Procedure:

- Substrate Preparation:

- Perform a standard pre-deposition clean on the silicon wafer to remove any native oxide from the exposed silicon regions. A common method is a dilute hydrofluoric acid (HF) dip followed by a DI water rinse and spin dry.

- Titanium Deposition:

- Load the wafer into a physical vapor deposition (PVD) or sputter system.

- Deposit a thin film of titanium, typically 30-40 nm thick, across the entire wafer surface.[14]

- First Anneal (C49 Formation):

- Transfer the wafer to the RTA system.

- Perform the first anneal at a relatively low temperature, around 650°C - 750°C, for 20-30 seconds in a nitrogen (N<sub>2</sub>) ambient.[14]

- Note: The nitrogen ambient is crucial as it causes the unreacted titanium over the oxide regions to form a titanium nitride (TiN) layer, which aids in the subsequent selective etch step.[9] This step forms the high-resistivity C49-TiSi<sub>2</sub> phase on the silicon regions.

- Selective Etch:

- Remove the wafer from the RTA system.

- Submerge the wafer in a selective wet etch solution (e.g., a mixture of H<sub>2</sub>O<sub>2</sub>, NH<sub>4</sub>OH, and H<sub>2</sub>O) to remove the TiN and any unreacted titanium from the oxide surfaces.[14] This etchant does not significantly attack the newly formed TiSi<sub>2</sub>.

- Rinse thoroughly with DI water and dry the wafer.

- Second Anneal (C54 Transformation):

- Return the wafer to the RTA system.

- Perform the second, higher-temperature anneal at approximately 800°C - 900°C for 20-30 seconds in a nitrogen (N<sub>2</sub>) ambient.[14]

- This step provides the thermal energy required to convert the metastable C49-TiSi<sub>2</sub> into the low-resistivity, stable C54-TiSi<sub>2</sub> phase.[6]

## Protocol 2: Characterization of TiSi<sub>2</sub> Thin Films

### 1. Sheet Resistance Measurement (Four-Point Probe):

- Objective: To determine the average sheet resistance (Rs) of the formed silicide film, which is a key indicator of the successful C49-to-C54 phase transformation.

- Procedure:

- Use a four-point probe measurement system.

- Place the probe head gently on the surface of the TiSi<sub>2</sub> film on a test area of the wafer.

- Apply a known current (I) through the outer two probes and measure the voltage (V) across the inner two probes.

- The sheet resistance is calculated as  $Rs = (V/I) * k$ , where k is a geometric correction factor (typically ~4.53 for a large film area).

- A successful transformation to C54-TiSi<sub>2</sub> should yield a low sheet resistance (e.g., ~5 ohms/sq for a 30 nm film).[14]

## 2. Phase Identification (X-Ray Diffraction - XRD):

- Objective: To confirm the crystal structure of the formed titanium silicide and verify the presence of the desired C54 phase.

- Procedure:

- Place the wafer sample in an X-ray diffractometer.

- Perform a scan over a range of 2θ angles.

- The resulting diffraction pattern will show peaks corresponding to specific crystal planes.

- Compare the peak locations to standard powder diffraction files for C49-TiSi<sub>2</sub> and C54-TiSi<sub>2</sub> to identify the phases present in the film.[15][16]

## 3. Morphological Analysis (SEM/TEM):

- Objective: To visually inspect the surface and interface morphology of the silicide film.

- Procedure:

- Scanning Electron Microscopy (SEM): Used to examine the top-down surface of the film. It can reveal information about grain size, uniformity, and potential issues like agglomeration or islanding.[15]

- Transmission Electron Microscopy (TEM): Requires preparing a cross-sectional sample of the film. TEM provides high-resolution imaging of the silicide layer, the silicide-silicon interface, and the film's thickness and grain structure.[15]

# Visualizations: Workflows and Logical Relationships

## Diagram 1: Experimental Workflow for Salicide Process

[Click to download full resolution via product page](#)

Caption: Workflow diagram of the two-step salicide process for TiSi<sub>2</sub> formation.

## Diagram 2: TiSi<sub>2</sub> Phase Transformation Pathway

[Click to download full resolution via product page](#)

Caption: Temperature-driven phase transformation pathway for titanium silicide.

## Diagram 3: Factors Influencing C54-TiSi<sub>2</sub> Formation

[Click to download full resolution via product page](#)

Caption: Key factors that promote or inhibit the C49-to-C54 TiSi<sub>2</sub> phase transformation.

### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. C49-C54 Titanium Disilicide (TiSi<sub>2</sub>) [globalsino.com]

- 2. Formation of Silicides and Germanides | Queen's Advanced MicroEngineering Centre [qub.ac.uk]

- 3. digital-library.theiet.org [digital-library.theiet.org]

- 4. web.stanford.edu [web.stanford.edu]

- 5. researchgate.net [researchgate.net]

- 6. nemanich.physics.asu.edu [nemanich.physics.asu.edu]

- 7. Salicide - Wikipedia [en.wikipedia.org]

- 8. researchgate.net [researchgate.net]

- 9. web.stanford.edu [web.stanford.edu]

- 10. qed2.com [qed2.com]

- 11. researchgate.net [researchgate.net]

- 12. nemanich.physics.asu.edu [nemanich.physics.asu.edu]

- 13. semanticscholar.org [semanticscholar.org]

- 14. A thermally stable salicide process using N<sub>sub</sub> 2/ implantation into TiSi<sub>sub</sub> 2/ | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 15. nemanich.physics.asu.edu [nemanich.physics.asu.edu]

- 16. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Application Notes and Protocols: Titanium Silicide (TiSi<sub>2</sub>) for Integrated Circuit Interconnects]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b078298#tisi-for-interconnects-in-integrated-circuits>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)