# Application Notes: Tantalum Silicide (TaSi<sub>2</sub>) as a Gate Material in Integrated Circuits

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Tantalum silicide*

Cat. No.: *B078852*

[Get Quote](#)

## 1.0 Introduction

As the dimensions of metal-oxide-semiconductor (MOS) devices continue to shrink in very-large-scale integration (VLSI) circuits, the performance limitations of traditional gate materials become more pronounced. For many years, heavily doped polycrystalline silicon (polysilicon) has been the dominant gate material due to its process compatibility and reliability. However, the relatively high resistivity of polysilicon leads to significant RC time delays, which can limit the switching speed of integrated circuits.<sup>[1][2]</sup> This has driven research into alternative gate materials with higher conductivity.

Refractory metal silicides, such as **tantalum silicide** (TaSi<sub>2</sub>), have emerged as a leading alternative.<sup>[1]</sup> TaSi<sub>2</sub> offers a compelling combination of low resistivity, high-temperature stability, and compatibility with existing silicon fabrication processes.<sup>[1][3]</sup> It is often used in a "polycide" structure, where a layer of silicide is deposited on top of a polysilicon layer. This approach maintains the stable and well-understood polysilicon-gate dielectric interface while significantly reducing the overall resistance of the gate line. These notes provide a comprehensive overview of the properties, deposition, and integration of **tantalum silicide** as a gate material for researchers and professionals in semiconductor device fabrication.

## 2.0 Properties of Tantalum Silicide (TaSi<sub>2</sub>)

**Tantalum silicide** possesses a range of electrical and physical properties that make it highly suitable for gate applications in integrated circuits.

- Low Resistivity: The primary advantage of  $\text{TaSi}_2$  is its low electrical resistivity, which is significantly lower than that of heavily doped polysilicon. As-deposited films have resistivities that can be further reduced by high-temperature annealing. After annealing at temperatures around  $1000^\circ\text{C}$ , resistivities in the range of  $45\text{--}60 \mu\Omega\cdot\text{cm}$  can be reproducibly achieved.[4][5] This low resistivity is critical for minimizing signal propagation delays in high-speed circuits.

- High Thermal Stability:  $\text{TaSi}_2$  is thermally stable at the high temperatures required for subsequent processing steps in device fabrication, such as dopant activation anneals. It is reported to be stable on silicon at temperatures up to  $1000^\circ\text{C}$ .[6]

- Work Function: The work function of **tantalum silicide** is a critical parameter for setting the threshold voltage ( $V_t$ ) of a MOS transistor. The effective work function can be influenced by the Si:Ta ratio.[7][8] For  $\text{TaSi}_2$ , the work function is generally suitable for CMOS applications, and its use has been shown to result in device parameters that are virtually identical to those with conventional polysilicon gates.[9]

- High Melting Point: **Tantalum silicide** has a high melting point of approximately  $2200^\circ\text{C}$ , contributing to its excellent thermal stability.[3][10]

- Process Compatibility:  $\text{TaSi}_2$  demonstrates good compatibility with standard silicon processing. It can be deposited using common thin-film deposition techniques like sputtering and chemical vapor deposition (CVD).[11][12] Furthermore, it exhibits good resistance to oxidation at high temperatures; during steam oxidation, a protective layer of silicon dioxide ( $\text{SiO}_2$ ) can be grown on the silicide surface.[4][13][14]

## 2.1 Data Presentation: Comparison of Gate Materials

The following table summarizes the key quantitative properties of **tantalum silicide** in comparison to heavily doped polysilicon, highlighting the significant advantage of  $\text{TaSi}_2$  in terms of electrical conductivity.

| Property                        | Tantalum Silicide<br>(TaSi <sub>2</sub> ) | n <sup>+</sup> Polysilicon | p <sup>+</sup> Polysilicon |

|---------------------------------|-------------------------------------------|----------------------------|----------------------------|

| Resistivity (μΩ·cm)             | 35 - 55 (annealed)[6]                     | 500 - 1000                 | 1000 - 2000                |

| Work Function (eV)              | ~4.5 - 4.6                                | ~4.1                       | ~5.1                       |

| Melting Point (°C)              | ~2200[3][10]                              | ~1414                      | ~1414                      |

| Thermal Stability on Si<br>(°C) | ~1000[6]                                  | >1100                      | >1100                      |

### 3.0 Deposition and Patterning of TaSi<sub>2</sub> Gates

Several methods are available for depositing **tantalum silicide** films, with sputtering and chemical vapor deposition being the most common.

- **Sputtering:** DC magnetron sputtering is a widely used physical vapor deposition (PVD) technique for TaSi<sub>2</sub>.[12][15] This can be done either by co-sputtering from separate tantalum and silicon targets or, more commonly, by sputtering from a composite TaSi<sub>2</sub> target.[1][4][5] Sputtering offers good control over film stoichiometry and uniformity. Post-deposition annealing is typically required to crystallize the film and achieve the lowest possible resistivity.[1][16]

- **Chemical Vapor Deposition (CVD):** Low-Pressure CVD (LPCVD) is another viable method for depositing high-quality TaSi<sub>2</sub> films.[11][17] A common chemistry involves the reaction of tantalum pentachloride (TaCl<sub>5</sub>) and silane (SiH<sub>4</sub>).[11][18] CVD processes can provide excellent conformal coverage over complex topographies, which is advantageous for advanced device structures.

- **Patterning and Etching:** After deposition, the TaSi<sub>2</sub> (or polycide) layer is patterned using standard photolithography and etching processes. Dry etching, specifically reactive ion etching (RIE), is typically employed. The plasma chemistry for etching TaSi<sub>2</sub> often involves fluorine-based or chlorine-based gases, such as SF<sub>6</sub>, CF<sub>4</sub>, or Cl<sub>2</sub>. The etching process must be carefully optimized to achieve anisotropic profiles and high selectivity to the underlying gate dielectric (e.g., SiO<sub>2</sub>) to prevent damage.

# Experimental Protocols

## Protocol 1: Sputter Deposition of a TaSi<sub>2</sub>/Polysilicon Polycide Gate Stack

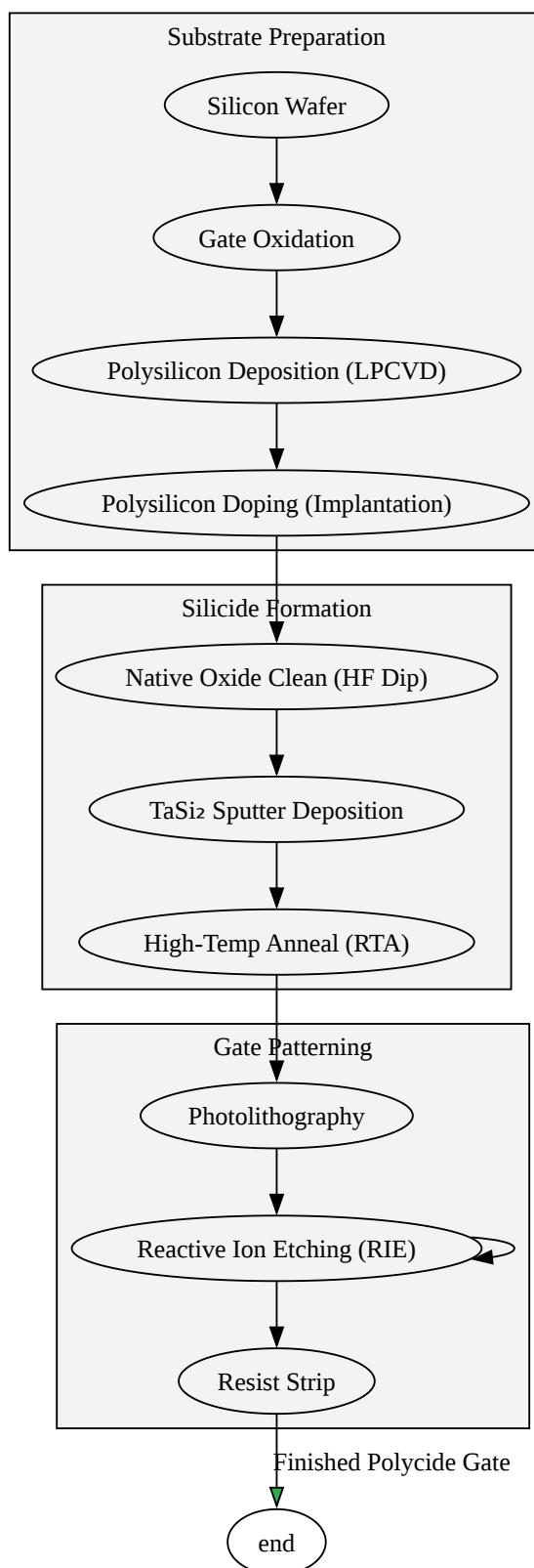

This protocol outlines the steps for depositing a **tantalum silicide** film onto a polysilicon layer using DC magnetron sputtering from a composite target.

1. Substrate Preparation: 1.1. Begin with silicon wafers that have a thermally grown gate oxide layer of the desired thickness. 1.2. Immediately transfer the wafers to an LPCVD furnace for polysilicon deposition to minimize contamination of the oxide surface. 1.3. Deposit a layer of undoped polysilicon (e.g., 200-300 nm thick) via the thermal decomposition of silane (SiH<sub>4</sub>) at approximately 620°C. 1.4. Dope the polysilicon layer to the desired conductivity type (n<sup>+</sup> or p<sup>+</sup>) through ion implantation or gas-phase doping.

2. Pre-Sputtering Procedure: 2.1. Perform a native oxide removal step on the polysilicon surface. This is typically done using a dilute hydrofluoric acid (HF) dip (e.g., 50:1 H<sub>2</sub>O:HF) for 30-60 seconds, followed by a deionized water rinse and spin-dry. 2.2. Immediately load the wafers into the load-lock of the sputtering system to prevent re-oxidation of the polysilicon surface.

3. **Tantalum Silicide** Sputtering: 3.1. Pump the deposition chamber down to a base pressure of < 5 x 10<sup>-7</sup> Torr.[13] 3.2. Introduce high-purity argon (Ar) gas into the chamber, establishing a stable process pressure (e.g., 5-10 mTorr).[13][14] 3.3. Pre-sputter the composite TaSi<sub>2</sub> target with the shutter closed for 5-10 minutes to clean the target surface. 3.4. Open the shutter and deposit the TaSi<sub>2</sub> film to the desired thickness (e.g., 150-250 nm) at a specific DC power setting. The substrate may be heated during deposition to influence film properties.

4. Post-Deposition Annealing: 4.1. After deposition, transfer the wafers to a furnace or rapid thermal annealing (RTA) system. 4.2. Perform an anneal in an inert atmosphere (e.g., N<sub>2</sub> or Ar) at a temperature between 800°C and 1000°C.[1][19] A typical RTA cycle might be 900°C for 30-60 seconds. This step serves to crystallize the TaSi<sub>2</sub> film into its low-resistivity phase and reduce film stress.

## Protocol 2: Fabrication of a MOS Capacitor with a TaSi<sub>2</sub> Gate

This protocol describes the fabrication of a basic MOS capacitor structure to evaluate the electrical quality of the TaSi<sub>2</sub> gate and the underlying dielectric.[20][21]

1. Wafer Cleaning and Oxidation: 1.1. Start with a p-type or n-type silicon wafer. 1.2. Perform a standard RCA clean or equivalent pre-oxidation cleaning procedure to remove organic and metallic contaminants. 1.3. Grow a high-quality gate oxide (e.g., silicon dioxide,  $\text{SiO}_2$ ) of a specific thickness (e.g., 10-50 nm) via thermal oxidation in a furnace.[20]

2. Gate Stack Deposition: 2.1. Deposit the  $\text{TaSi}_2$  gate electrode layer using a method such as the sputtering protocol described above (Protocol 1). For this test structure, a polycide stack is not strictly necessary, and  $\text{TaSi}_2$  can be deposited directly onto the gate oxide.[1]

3. Gate Patterning: 3.1. Apply a layer of photoresist to the wafer surface via spin-coating. 3.2. Expose the photoresist with a photomask that defines the capacitor gate areas (typically circular or square pads of known dimensions). 3.3. Develop the photoresist to create the etch mask. 3.4. Etch the  $\text{TaSi}_2$  layer using a suitable reactive ion etching (RIE) process. The etch should stop on the gate oxide. 3.5. Remove the remaining photoresist using a solvent strip or plasma ashing.

4. Backside Contact Formation: 4.1. Remove the oxide from the backside of the wafer using a buffered oxide etch (BOE) or HF dip. 4.2. Deposit a layer of aluminum (Al) or another suitable metal on the backside of the wafer using evaporation or sputtering to form a good ohmic contact to the substrate. 4.3. Perform a forming gas ( $\text{H}_2/\text{N}_2$ ) anneal at  $\sim 400\text{-}450^\circ\text{C}$ . This step sinters the backside contact and anneals out interface traps at the  $\text{Si}/\text{SiO}_2$  interface.

5. Electrical Characterization: 5.1. The completed MOS capacitors can now be electrically tested. 5.2. Perform Capacitance-Voltage (C-V) measurements to determine properties such as oxide thickness, flat-band voltage ( $V_{fb}$ ), and interface trap density ( $D_{it}$ ). 5.3. Perform Current-Voltage (I-V) measurements to assess the leakage current through the gate dielectric and determine its breakdown voltage.

## Visualizations

[Click to download full resolution via product page](#)

```

// TaSi2 Properties tasi2 [label="Tantalum Silicide (TaSi2)", pos="-3,1.5!", fillcolor="#4285F4",

fontcolor="#FFFFFF"]; tasi2_res [label="Low Resistivity\n(35-55 μΩ·cm)", pos="-4.5,0!",

fillcolor="#34A853", fontcolor="#FFFFFF"]; tasi2_temp [label="High Thermal

Stability\n(~1000°C)", pos="-4.5,3!", fillcolor="#34A853", fontcolor="#FFFFFF"];

// Polysilicon Properties poly [label="Doped Polysilicon", pos="3,1.5!", fillcolor="#EA4335",

fontcolor="#FFFFFF"]; poly_res [label="High Resistivity\n(>500 μΩ·cm)", pos="4.5,0!",

fillcolor="#FBBC05", fontcolor="#202124"]; poly_int [label="Excellent Interface\nwith SiO2",

pos="4.5,3!", fillcolor="#FBBC05", fontcolor="#202124"];

// Edges center -> tasi2 [color="#4285F4"]; center -> poly [color="#EA4335"];

tasi2 -> tasi2_res [label="Advantage", dir=back, color="#34A853"]; tasi2 -> tasi2_temp

[label="Advantage", dir=back, color="#34A853"];

poly -> poly_res [label="Disadvantage", dir=back, color="#FBBC05"]; poly -> poly_int

[label="Advantage", dir=back, color="#FBBC05"]; } end_dot

Caption: Comparison of TaSi2 and

Polysilicon Properties.

```

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. web.njit.edu [web.njit.edu]

- 2. ias.ac.in [ias.ac.in]

- 3. Tantalum Disilicide Powder (TaSi<sub>2</sub>) [fusnano.com]

- 4. researchgate.net [researchgate.net]

- 5. Tantalum silicide films deposited by dc sputtering for Journal of Electronic Materials - IBM Research [research.ibm.com]

- 6. web.stanford.edu [web.stanford.edu]

- 7. pubs.aip.org [pubs.aip.org]

- 8. [pubs.aip.org](https://pubs.aip.org) [pubs.aip.org]

- 9. [pubs.aip.org](https://pubs.aip.org) [pubs.aip.org]

- 10. Synthesis, Characterization, and Mechanism of Formation of Janus-Like Nanoparticles of Tantalum Silicide-Silicon (TaSi<sub>2</sub>/Si) | MDPI [mdpi.com]

- 11. Low pressure chemical vapor deposition of tantalum silicide. | Nokia.com [nokia.com]

- 12. [aemdeposition.com](https://aemdeposition.com) [aemdeposition.com]

- 13. [researchgate.net](https://researchgate.net) [researchgate.net]

- 14. [researchgate.net](https://researchgate.net) [researchgate.net]

- 15. [PDF] PREPARATION AND PROPERTIES OF TANTALUM SILICIDE FILMS ON SILICON SUBSTRATES by Lei Jin Tantalum silicide | Semantic Scholar [semanticscholar.org]

- 16. Optimization of TaSi<sub>2</sub> Processing for 500 °C Durable SiC JFET-R Integrated Circuits | Scientific.Net [scientific.net]

- 17. [files01.core.ac.uk](https://files01.core.ac.uk) [files01.core.ac.uk]

- 18. [2024.sci-hub.st](https://2024.sci-hub.st) [2024.sci-hub.st]

- 19. "Electrical and compositional properties of TaSi<sub>2</sub> films" by N. M. Ravindra, Lei Jin et al. [digitalcommons.njit.edu]

- 20. [sturm.scholar.princeton.edu](https://sturm.scholar.princeton.edu) [sturm.scholar.princeton.edu]

- 21. US6667203B2 - Method of fabricating a MOS capacitor - Google Patents [patents.google.com]

- To cite this document: BenchChem. [Application Notes: Tantalum Silicide (TaSi<sub>2</sub>) as a Gate Material in Integrated Circuits]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b078852#tantalum-silicide-as-a-gate-material-in-integrated-circuits>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)