# troubleshooting low on/off ratios in violanthrone transistors

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Violanthrone*

Cat. No.: B7798473

[Get Quote](#)

## Technical Support Center: Violanthrone-Based Transistors

This guide provides troubleshooting assistance for researchers encountering low on/off current ratios in **violanthrone**-based organic field-effect transistors (OFETs).

## Frequently Asked Questions (FAQs)

Q1: My **violanthrone**-based OFET exhibits a very low on/off ratio. What are the most common causes?

A low on/off ratio is typically a symptom of a high off-state current ( $I_{off}$ ) or a low on-state current ( $I_{on}$ ). The primary factors contributing to this issue can be categorized as:

- Material Impurities: Purity of the **violanthrone** semiconductor is critical. Impurities can act as charge traps or create unintended doping, increasing the off-state current.[1][2][3][4][5]

- Interfacial Defects: The interface between the organic semiconductor and the gate dielectric is where the conductive channel forms. Traps, contaminants, or poor surface energy matching at this interface can disrupt charge accumulation and transport.[6][7][8]

- High Contact Resistance: A significant energy barrier between the source/drain electrodes and the **violanthrone** layer can impede charge injection, thereby lowering the on-state current.[9][10][11][12]

- Film Morphology: Poor crystallinity, small grain sizes, or a disordered molecular arrangement in the **violanthrone** thin film can hinder efficient charge transport, reducing the on-current. [\[13\]](#)

- Device Architecture and Fabrication: Issues like gate leakage, inappropriate device geometry, or residual solvents from the fabrication process can all contribute to poor performance.[\[8\]](#)[\[13\]](#)

Q2: How does the purity of the **violanthrone** material affect the on/off ratio, and how can I improve it?

Impurities in the organic semiconductor are a major cause of poor device performance. They can introduce trap states within the energy gap, which hinder charge transport and can increase the off-state current.[\[1\]](#)[\[2\]](#)[\[3\]](#) Studies consistently show that rigorous purification of organic semiconductors leads to orders-of-magnitude improvements in charge carrier mobility and other device parameters.[\[4\]](#)[\[5\]](#)

Troubleshooting Action: Material Purification

The most effective method for purifying **violanthrone** and similar organic molecules is temperature gradient sublimation.[\[4\]](#)[\[5\]](#) This technique separates materials based on their different sublimation and deposition temperatures under high vacuum.

## Experimental Protocol: Temperature Gradient Sublimation

Objective: To purify **violanthrone** powder by separating it from less volatile and more volatile impurities.

Apparatus:

- A three-zone tube furnace

- A quartz or glass sublimation tube sealed at one end

- A vacuum pump capable of reaching high vacuum ( $< 10^{-5}$  Torr)

- A carrier gas line (e.g., Argon or Nitrogen)

- Temperature controllers for each furnace zone

Procedure:

- Loading: Place the crude **violanthrone** powder in the sealed end of the sublimation tube.

- Assembly: Insert the tube into the furnace, connecting the open end to the vacuum system.

- Evacuation: Evacuate the tube to a high vacuum to remove air and volatile contaminants.

- Heating:

- Set the temperature of the first zone (source zone) to the sublimation temperature of **violanthrone**. This must be determined empirically but is typically the highest temperature.

- Establish a temperature gradient across the subsequent zones, with the temperature decreasing along the length of the tube away from the source. This gradient is material-specific and crucial for effective separation.<sup>[4]</sup>

- Sublimation & Deposition: As the source material heats up, **violanthrone** sublimes, travels along the tube via a carrier gas (or under vacuum), and deposits as purified crystals in a cooler zone. Impurities with different sublimation points will deposit in different zones.

- Collection: After the process is complete (typically several hours to days), cool the system down. Carefully remove the sublimation tube and collect the purified crystalline material from the desired deposition zone.

Q3: The off-current of my device is too high. What role does the gate dielectric interface play?

A high off-current is often caused by charge traps or unwanted charge carriers at the semiconductor-dielectric interface.<sup>[6]</sup> The properties of the dielectric surface—such as roughness, surface energy, and the presence of functional groups—can significantly impact the molecular ordering of the **violanthrone** film and the density of trap states.<sup>[8][14]</sup> Modifying the dielectric surface is a common strategy to improve device performance.<sup>[6][15]</sup>

## Troubleshooting Action: Dielectric Surface Treatment

Treating the gate dielectric (commonly  $\text{SiO}_2$ ) with a self-assembled monolayer (SAM) like octadecyltrichlorosilane (OTS) can dramatically improve the interface. OTS treatment makes the surface hydrophobic, which promotes better molecular ordering of many organic semiconductors and passivates surface traps.

## Experimental Protocol: OTS Surface Treatment of Si/ $\text{SiO}_2$ Substrates

Objective: To form a high-quality self-assembled monolayer of OTS on a silicon dioxide surface to improve the semiconductor/dielectric interface.

### Materials:

- Si/ $\text{SiO}_2$  wafers

- Deionized water, acetone, isopropanol

- Piranha solution ( $\text{H}_2\text{SO}_4$  and  $\text{H}_2\text{O}_2$  mixture - EXTREME CAUTION REQUIRED) or UV-Ozone cleaner

- Anhydrous toluene

- Octadecyltrichlorosilane (OTS)

### Procedure:

- Substrate Cleaning:

- Cut the Si/ $\text{SiO}_2$  wafer to the desired size.

- Sonicate the substrate sequentially in deionized water, acetone, and isopropanol for 15 minutes each.[\[16\]](#)

- Dry the substrate with a stream of high-purity nitrogen gas.

- Surface Hydroxylation:

- Option A (Piranha Etch): Immerse the cleaned substrate in a freshly prepared piranha solution for 10-15 minutes to remove organic residues and create hydroxyl (-OH) groups on the surface. Rinse thoroughly with deionized water and dry with nitrogen.

- Option B (UV-Ozone): Place the substrate in a UV-Ozone cleaner for 10-15 minutes. This is a safer alternative to piranha solution for hydroxylation.

- SAM Formation:

- Prepare a dilute solution of OTS in anhydrous toluene (e.g., 1-10 mM) inside a nitrogen-filled glovebox to avoid moisture-induced polymerization.

- Immerse the cleaned and hydroxylated substrate in the OTS solution for 30-60 minutes. [16] This allows the OTS molecules to form a covalent bond with the surface hydroxyl groups.

- Rinsing and Curing:

- Remove the substrate from the solution and rinse thoroughly with fresh anhydrous toluene to remove any unbound OTS molecules.[16]

- Dry the substrate with a nitrogen stream.

- (Optional) Bake the substrate at 100-120 °C for 10-20 minutes to further cure the monolayer.

- Verification: The surface should now be highly hydrophobic. A simple contact angle measurement with a water droplet can verify the quality of the OTS layer (a high contact angle indicates a successful coating).

Q4: My on-current is very low, even with a high gate voltage. Could this be a contact resistance issue?

Yes, a low on-current is a classic sign of high contact resistance ( $R_c$ ).[9][10] This resistance arises at the interface between the metal source/drain electrodes and the organic semiconductor layer, impeding the injection of charge carriers into the channel.[11][12]  $R_c$  can

sometimes dominate the total device resistance, limiting the on-state current and leading to an underestimation of the material's true mobility.[9][17]

#### Troubleshooting Action: Post-Deposition Annealing

Thermal annealing of the completed transistor is a widely used technique to improve the structural and electronic properties of the thin film and its interfaces.[13][18] Annealing can enhance the crystallinity of the **violanthrone** film, increase grain size, and improve the physical and electrical contact between the semiconductor and the electrodes, thereby reducing contact resistance.[13]

## Data on Annealing Effects

While specific data for **violanthrone** is limited, the table below, based on general principles for organic semiconductors, illustrates the expected impact of annealing temperature on key transistor parameters.[13]

| Annealing Temperature      | Film Crystallinity       | Contact Resistance | Carrier Mobility ( $\mu$ ) | On/Off Ratio |

|----------------------------|--------------------------|--------------------|----------------------------|--------------|

| No Annealing (RT)          | Low                      | High               | Low                        | Low          |

| Optimal Temp ( $T_{opt}$ ) | High                     | Reduced            | High                       | High         |

| Above $T_{opt}$            | May decrease (dewetting) | May increase       | Decreases                  | Decreases    |

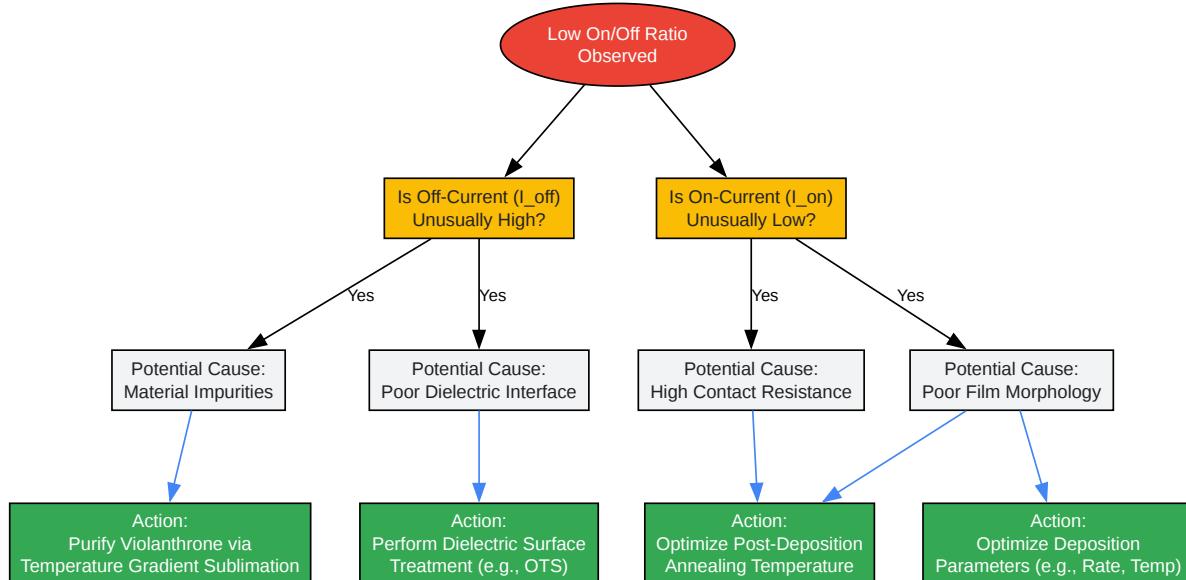

## Troubleshooting Workflow

The following diagram illustrates a logical workflow for diagnosing and addressing low on/off ratios in **violanthrone** transistors.

## Troubleshooting Workflow for Low On/Off Ratios

[Click to download full resolution via product page](#)

Caption: A logical flowchart for troubleshooting low on/off ratios.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. anirban.people.iitgn.ac.in [anirban.people.iitgn.ac.in]

- 2. researchgate.net [researchgate.net]

- 3. [1908.11854] The influence of impurities on the charge carrier mobility of small molecule organic semiconductors [arxiv.org]

- 4. Purity of organic semiconductors as a key factor for the performance of organic electronic devices - Materials Chemistry Frontiers (RSC Publishing) DOI:10.1039/D0QM00690D [pubs.rsc.org]

- 5. Purity of organic semiconductors as a key factor for the performance of organic electronic devices - Materials Chemistry Frontiers (RSC Publishing) [pubs.rsc.org]

- 6. dr.ntu.edu.sg [dr.ntu.edu.sg]

- 7. Single-crystal dielectrics for organic field-effect transistors - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 8. pubs.acs.org [pubs.acs.org]

- 9. pubs.aip.org [pubs.aip.org]

- 10. fkf.mpg.de [fkf.mpg.de]

- 11. Origin of large contact resistance in organic field-effect transistors | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 12. researchgate.net [researchgate.net]

- 13. benchchem.com [benchchem.com]

- 14. pubs.acs.org [pubs.acs.org]

- 15. ICMAB - Gate-Dielectric Surface Engineering With Fluorinated Monolayers: Minimizing Contact Resistance and Nonidealities in OFETs [icmab.es]

- 16. benchchem.com [benchchem.com]

- 17. pubs.acs.org [pubs.acs.org]

- 18. m.youtube.com [m.youtube.com]

- To cite this document: BenchChem. [troubleshooting low on/off ratios in violanthrone transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b7798473#troubleshooting-low-on-off-ratios-in-vianthrone-transistors]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)