# Technical Support Center: Surface Passivation of Alumina-Based Electronic Substrates

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Alumina**

Cat. No.: **B075360**

[Get Quote](#)

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers, scientists, and drug development professionals working on the surface passivation of **alumina**-based electronic substrates.

## Troubleshooting Guide

This guide addresses common issues encountered during experimental work, offering potential causes and solutions in a question-and-answer format.

### Issue 1: Poor Adhesion or Blistering of the Passivation Film

- Question: Why is my deposited passivation layer peeling or forming blisters?

- Answer: Poor adhesion and blistering are often linked to improper surface preparation or stress within the deposited film. The natural oxide layer on aluminum, if not properly treated, can be an unstable foundation for subsequent coatings.[\[1\]](#)

- Potential Cause 1: Inadequate Substrate Cleaning. Organic residues (oils, fingerprints), dust, or other contaminants on the **alumina** surface can interfere with the bonding of the passivation layer.[\[2\]](#)[\[3\]](#)

- Solution: Implement a thorough cleaning protocol. This should include immersion in a heated solvent within an ultrasonic cleaner to remove organic contaminants, followed by

a rinse with deionized or distilled water.<sup>[2]</sup> For inorganic contaminants, acid or alkaline treatments may be necessary.<sup>[2][4]</sup>

- Potential Cause 2: Surface Passivation. The substrate surface can become passivated if there are delays between cleaning and deposition, leading to the formation of a weak boundary layer.<sup>[3]</sup>

- Solution: Minimize the time between the final cleaning step and the deposition of the passivation film. Store cleaned substrates in a vacuum or inert environment if immediate processing is not possible.<sup>[2]</sup>

- Potential Cause 3: High Film Stress. Mismatched thermal expansion coefficients between the **alumina** substrate and the passivation layer can cause stress, especially after high-temperature annealing, leading to cracking or delamination.<sup>[5]</sup>

- Solution: Optimize the annealing process by using a slower temperature ramp-up and cool-down rate. For sol-gel coatings, controlling the coating thickness and the chemical composition of the sol can help mitigate stress.<sup>[6]</sup>

- Potential Cause 4: Incorrect Deposition Parameters (for ALD/PECVD). For techniques like Plasma-Enhanced Chemical Vapor Deposition (PECVD), improper process parameters can lead to blistering, although this may not always significantly affect the passivation quality for certain film thicknesses.<sup>[7]</sup>

- Solution: Optimize deposition parameters such as temperature, pressure, and precursor flow rates. Ensure the substrate surface is suitable for the chosen deposition chemistry.

#### Issue 2: High Leakage Current in the Passivated Device

- Question: My passivated **alumina** substrate exhibits unexpectedly high leakage currents. What could be the cause?

- Answer: High leakage current can be a result of defects in the passivation layer or at the interface between the layer and the substrate.

- Potential Cause 1: Crystalline Defects in the Passivation Layer. The crystalline structure of the passivation layer can influence leakage currents. For instance, the crystallization of

HfO<sub>2</sub> layers at lower temperatures compared to Al<sub>2</sub>O<sub>3</sub> can lead to increased leakage.[8]

- Solution: Introducing **alumina** layers into other high-k dielectric stacks can help reduce leakage.[8] Optimizing the annealing temperature is also crucial, as it affects the film's microstructure and density.[9]

- Potential Cause 2: Impurities and Charge Carriers. Impurities within the **alumina** substrate or introduced during processing can act as charge carriers, increasing leakage current.[10] This is particularly relevant at high operating temperatures.

- Solution: Use high-purity **alumina** substrates. Ensure all processing steps, including the application of electrode pastes, are done in a clean environment to prevent the introduction of mobile ions like sodium.[10]

- Potential Cause 3: Interfacial Traps and Defects. A high density of traps at the interface between the **alumina** and the semiconductor material can promote leakage.[8]

- Solution: Proper surface cleaning and preparation are critical to minimize interface defects.[11] Post-deposition annealing can also help to reduce the density of interface states.[12][13]

### Issue 3: Inconsistent or Non-Reproducible Passivation Quality

- Question: I am getting inconsistent results between different experimental runs. Why?

- Answer: Inconsistency in passivation quality often points to poor control over critical process variables.

- Potential Cause 1: Variability in Substrate Surface Condition. The effectiveness of passivation is highly sensitive to the initial state of the substrate surface.[12] Variations in cleaning procedures or exposure to ambient conditions can lead to different outcomes.

- Solution: Standardize your cleaning protocol and strictly control the time and environment between cleaning and deposition.[2] Using a pre-treatment that creates a stable, thin chemical oxide layer can sometimes improve reproducibility.[12]

- Potential Cause 2: Fluctuations in Deposition Parameters. For methods like CVD and ALD, even small variations in temperature, pressure, or precursor flow rates can affect film properties.[14][15]

- Solution: Calibrate and carefully monitor all deposition equipment. Ensure stable and reproducible control of all process parameters.

- Potential Cause 3: Sol-Gel Solution Aging. For sol-gel techniques, the properties of the precursor solution can change over time due to ongoing hydrolysis and condensation reactions.[6]

- Solution: Prepare fresh sol-gel solutions for each set of experiments or precisely control the aging time of the sol before use.

## Frequently Asked Questions (FAQs)

Q1: What is surface passivation and why is it important for **alumina** substrates?

A1: Surface passivation involves creating a thin, inert layer on a material to make it less chemically reactive with its environment.[16] For **alumina** substrates used in electronics, this is crucial for several reasons:

- Electrical Insulation: It helps to electrically isolate conductive paths, reducing leakage currents and preventing short circuits.

- Corrosion Protection: The passivation layer acts as a barrier against moisture and other corrosive agents that could degrade the electronic components.[7]

- Improved Device Performance: In semiconductor devices, passivation reduces the number of electronic trap states at the surface, which can otherwise degrade performance by acting as recombination centers for charge carriers.[17]

Q2: What are the common surface passivation techniques for **alumina** substrates?

A2: Several techniques are used to deposit passivation layers on **alumina**, each with its own advantages and disadvantages.

- Atomic Layer Deposition (ALD): This technique allows for the deposition of very thin, uniform, and conformal films with precise thickness control.[18] It is excellent for creating high-quality passivation layers like Al<sub>2</sub>O<sub>3</sub>. However, conventional ALD has a very low deposition rate.[17]

- Chemical Vapor Deposition (CVD): CVD is a cost-effective process for creating high-quality films and can achieve higher deposition rates than ALD.[19] It is widely used for industrial applications.[14]

- Plasma-Enhanced Chemical Vapor Deposition (PECVD): PECVD is an alternative to ALD and is known for its high-temperature process stability.[17]

- Sol-Gel Process: This is a wet-chemical technique used to produce ceramic or glass coatings.[20] It is a versatile and low-cost method but controlling the film thickness and avoiding cracks can be challenging.[6]

Q3: How do I properly clean an **alumina** substrate before passivation?

A3: A multi-step cleaning process is essential to remove various types of contaminants. The exact method depends on the nature of the contaminants and the requirements of the final product.[2] A general procedure is as follows:

- Organic Contaminant Removal: Immerse the substrate in a heated solvent (e.g., acetone, isopropanol) and place it in an ultrasonic cleaner for at least 15 minutes to remove oils, greases, and fingerprints.[2]

- Rinsing: Thoroughly rinse the substrate with deionized or distilled water to remove the solvent and any dislodged particles.[2]

- Inorganic Contaminant Removal (if necessary): For metallic or salt residues, an acid or alkaline treatment may be required. A 10% solution of hydrochloric or nitric acid can be used for soaking.[19] Alternatively, a warm 1-2% solution of a precision cleaner like Alconox® in an ultrasonic bath is also effective.[2] Be cautious, as strong acids can also etch the **alumina**.

- Final Rinse: Perform a final, thorough rinse with high-purity deionized water to remove any residual cleaning agents.[2][19]

- Drying: Dry the substrate in a clean environment, for example, by blowing it with dry nitrogen or placing it in a clean oven.[2] After cleaning, handle the substrates with ceramic or clean metal tweezers to avoid recontamination.[2]

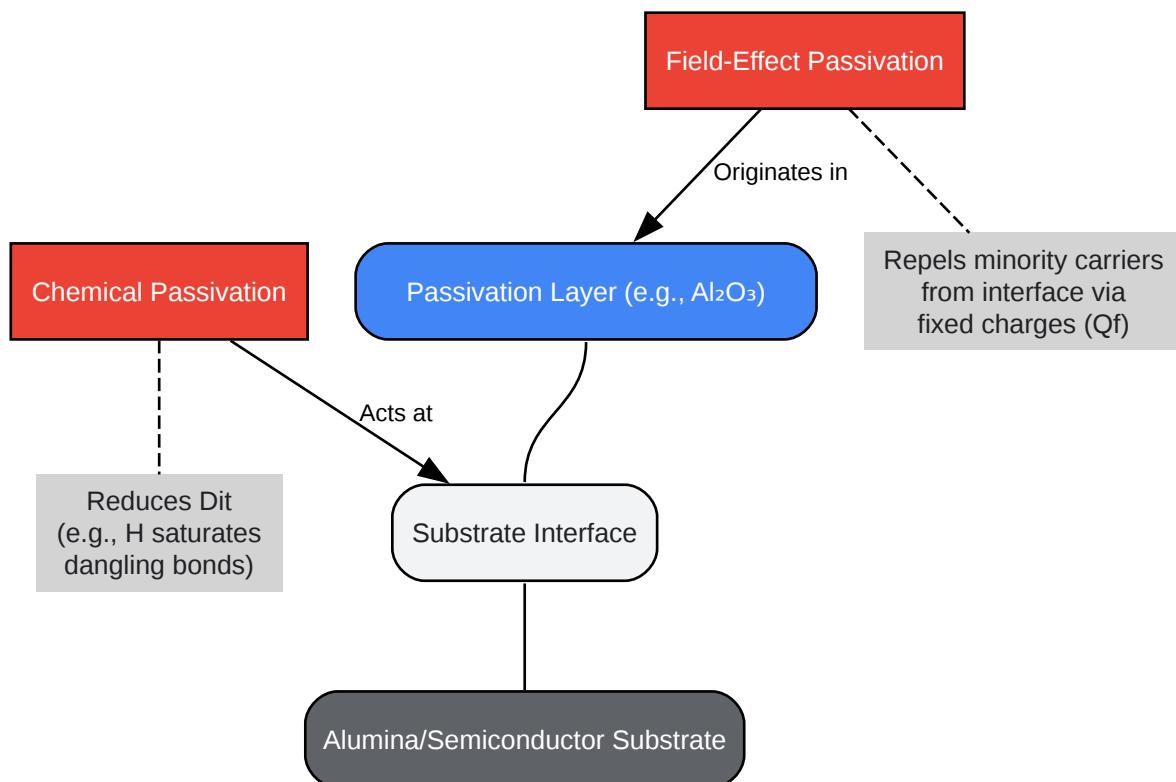

Q4: What is the difference between "chemical passivation" and "field-effect passivation"?

A4: Both are mechanisms by which a passivation layer reduces surface recombination in semiconductors, and they often work in conjunction.

- Chemical Passivation: This refers to the reduction of the density of electronic interface states (Dit) by satisfying dangling bonds at the semiconductor surface. For example, hydrogen atoms can diffuse to the interface and bond with silicon dangling bonds, neutralizing them as recombination centers.[18]

- Field-Effect Passivation: This mechanism relies on a high density of fixed electrical charges (Qf) within the passivation layer. These charges create an electric field that repels one type of charge carrier (e.g., electrons) from the surface, thereby preventing them from recombining at interface states. Al<sub>2</sub>O<sub>3</sub> is known for its high density of negative fixed charges, which makes it particularly effective for passivating p-type silicon surfaces.[18]

## Data Presentation

Table 1: Performance Comparison of ALD Al<sub>2</sub>O<sub>3</sub> Passivation Techniques

| Parameter                      | PE-ALD Al <sub>2</sub> O <sub>3</sub> | T-ALD Al <sub>2</sub> O <sub>3</sub> | Unit                              | Reference |

|--------------------------------|---------------------------------------|--------------------------------------|-----------------------------------|-----------|

| Film Thickness                 | 15                                    | 15                                   | nm                                | [18]      |

| Fixed Charge Density (Qf)      | ~ $5.2 \times 10^{12}$                | ~ $2.3 \times 10^{12}$               | cm <sup>-2</sup>                  | [18]      |

| Interface State Density (Dit)  | ~ $3 \times 10^{11}$                  | ~ (1-3) $\times 10^{11}$             | cm <sup>-2</sup> eV <sup>-1</sup> | [18]      |

| Surface Recombination Velocity | < 3                                   | Not specified                        | cm/s                              | [18]      |

Table 2: Effect of Post-Deposition Annealing (PDA) on Thermal ALD Al<sub>2</sub>O<sub>3</sub> Passivation Quality

| Deposition Temp. (°C) | PDA Temp. (°C) | PDA Time (min) | Effective Carrier Lifetime ( $\tau_{eff}$ ) | Reference |

|-----------------------|----------------|----------------|---------------------------------------------|-----------|

| 100                   | As-deposited   | -              | A few tens of $\mu$ s                       | [12]      |

| 100                   | 200            | 5              | ~1 ms                                       | [12]      |

| 150                   | 200            | 5              | ~1 ms                                       | [12]      |

| 100                   | 250            | 5              | >1 ms                                       | [12]      |

| 100                   | 250            | 5              | ~0.5 ms (for 6-8 nm film)                   | [13]      |

Table 3: Typical Process Parameters for Different Passivation Techniques

| Parameter       | Atomic Layer Deposition (ALD)                             | Chemical Vapor Deposition (CVD)                                         | Sol-Gel                                       |

|-----------------|-----------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------|

| Precursors      | Trimethylaluminum (TMA), H <sub>2</sub> O, O <sub>3</sub> | AlCl <sub>3</sub> , H <sub>2</sub> , CO <sub>2</sub> , H <sub>2</sub> S | Aluminum isopropoxide, Aluminum chloride      |

| Temperature     | 100 - 300 °C[9][12]                                       | 960 - 1050 °C[15][21]                                                   | Room temp. synthesis; Annealing up to 1200 °C |

| Pressure        | Varies (e.g., APALD at atmospheric)[22]                   | 50 - 100 Torr[21]                                                       | Atmospheric                                   |

| Deposition Rate | ~0.1 nm/cycle[9]                                          | Varies (e.g., 0.06 $\mu$ m/hr)[15]                                      | N/A (Thickness controlled by coating method)  |

| Key Feature     | Excellent conformality and thickness control              | High throughput, cost-effective                                         | Low cost, simple equipment                    |

# Experimental Protocols

## Protocol 1: Standard Cleaning of **Alumina** Substrates

- Initial Degreasing:

- Place the **alumina** substrates in a clean glass beaker.

- Add enough acetone to fully submerge the substrates.[[11](#)]

- Place the beaker in an ultrasonic bath and sonicate for 15 minutes.[[2](#)]

- Carefully decant the acetone.

- Repeat the process with isopropyl alcohol (IPA) for 15 minutes.

- Deionized (DI) Water Rinse:

- Rinse the substrates thoroughly with flowing DI water for at least 3 minutes.

- Acid/Base Cleaning (Optional, for stubborn inorganic residues):

- Submerge the substrates in a 10% hydrochloric acid (HCl) solution at room temperature for 10-15 minutes.[[19](#)] CAUTION: Handle acid with appropriate personal protective equipment (PPE) in a fume hood.

- Alternatively, use a warm (50-60°C) 1-2% Alconox® solution in an ultrasonic bath for 15 minutes.[[2](#)]

- Final DI Water Rinse:

- Rinse the substrates extensively with flowing DI water for 5 minutes to ensure all cleaning agents are removed.

- Drying:

- Dry the substrates using a nitrogen (N<sub>2</sub>) gun.

- Place the cleaned substrates in an oven at 120°C for at least 30 minutes to ensure they are completely dry before transferring to the deposition chamber.[2]

#### Protocol 2: Deposition of Al<sub>2</sub>O<sub>3</sub> Film via Sol-Gel Method

This protocol describes the synthesis of an **alumina** sol using aluminum isopropoxide as a precursor.

- Sol Preparation:

- In a dry flask under an inert atmosphere (e.g., nitrogen), dissolve aluminum isopropoxide (AIP) in a solvent like 1-butanol (weight ratio of AIP to solvent can be ~1:60).[23]

- Stir the solution vigorously with a magnetic stirrer for 3 hours at room temperature until the AIP is fully dissolved.[23]

- Hydrolysis:

- Prepare a mixture of distilled water and acetic acid (to control the hydrolysis rate). A typical weight ratio of AIP to water is 1:1, and AIP to acetic acid is 40:1.[23]

- Add the water/acid mixture drop-wise to the AIP solution while continuing to stir.[23]

- Stir the resulting solution for another 3 hours to allow for hydrolysis and the formation of a stable sol.[23]

- Coating Application (Spin Coating):

- Place the cleaned **alumina** substrate on the spin coater chuck.

- Dispense the prepared sol onto the center of the substrate.

- Spin the substrate at a defined speed (e.g., 3000 rpm) for a set time (e.g., 30 seconds) to achieve a uniform film. The final thickness will depend on the sol viscosity and spin parameters.

- Gelling and Drying:

- After coating, place the substrate on a hotplate at 100°C for 10-15 minutes to evaporate the solvent and form a gel.

- Calcination and Annealing:

- Transfer the coated substrate to a tube furnace.

- Heat the sample to 600°C with a slow ramp rate (e.g., 2°C/minute).[\[23\]](#)

- Hold at the peak temperature for 2-6 hours to calcine the gel into an amorphous **alumina** film.[\[23\]](#)

- For crystallization into **α-alumina**, higher temperatures ( $\geq 1000^{\circ}\text{C}$ ) are required.

- Allow the furnace to cool down slowly to room temperature to prevent thermal shock and cracking of the film.

#### Protocol 3: Characterization using Capacitance-Voltage (C-V) Measurement

This protocol outlines the steps to determine the interface state density ( $D_{it}$ ) and fixed charge density ( $Q_f$ ) of a passivation layer.

- Device Fabrication:

- Deposit the passivation layer (e.g.,  $\text{Al}_2\text{O}_3$ ) on the substrate.

- Deposit metal contacts (e.g., aluminum) on top of the passivation layer through a shadow mask to form Metal-Insulator-Semiconductor (MIS) capacitors.

- Deposit a metal contact on the backside of the substrate for the ground connection.

- Measurement Setup:

- Use an LCR meter or a dedicated C-V analysis system.

- Connect the probes to the top and bottom contacts of the MIS capacitor.

- High-Frequency C-V Measurement:

- Set the measurement frequency to a high value (e.g., 1 MHz) where interface traps cannot respond.[24]

- Sweep the DC bias voltage from accumulation to deep depletion (e.g., from -5V to +5V for a p-type substrate) and record the capacitance.[24]

- The resulting C-V curve will show the capacitance in accumulation ( $C_{ox}$ ) and in deep depletion ( $C_{min}$ ).

- Quasi-Static C-V Measurement:

- Use a very slow voltage ramp to keep the device in thermal equilibrium, allowing interface traps to respond.[24]

- Sweep the voltage over the same range as the high-frequency measurement and record the low-frequency capacitance ( $C_{lf}$ ).

- Data Analysis:

- Fixed Charge Density (Qf): Calculate the flat-band voltage ( $V_{fb}$ ) shift from the ideal C-V curve. The fixed charge density can be determined from this shift. An introduction of fixed oxide charges shifts the entire C-V characteristic.[25]

- Interface State Density (Dit): The interface trap density can be calculated by comparing the high-frequency and quasi-static C-V curves.[26] The interface trap capacitance ( $C_{it}$ ) is given by:  $C_{it} = ( (1/C_{lf}) - (1/C_{ox}) )^{-1} - C_s$ , where  $C_s$  is the semiconductor capacitance derived from the high-frequency curve. The interface state density is then  $Dit = C_{it} / q$ , where  $q$  is the elementary charge.[24][27]

## Mandatory Visualizations

[Click to download full resolution via product page](#)

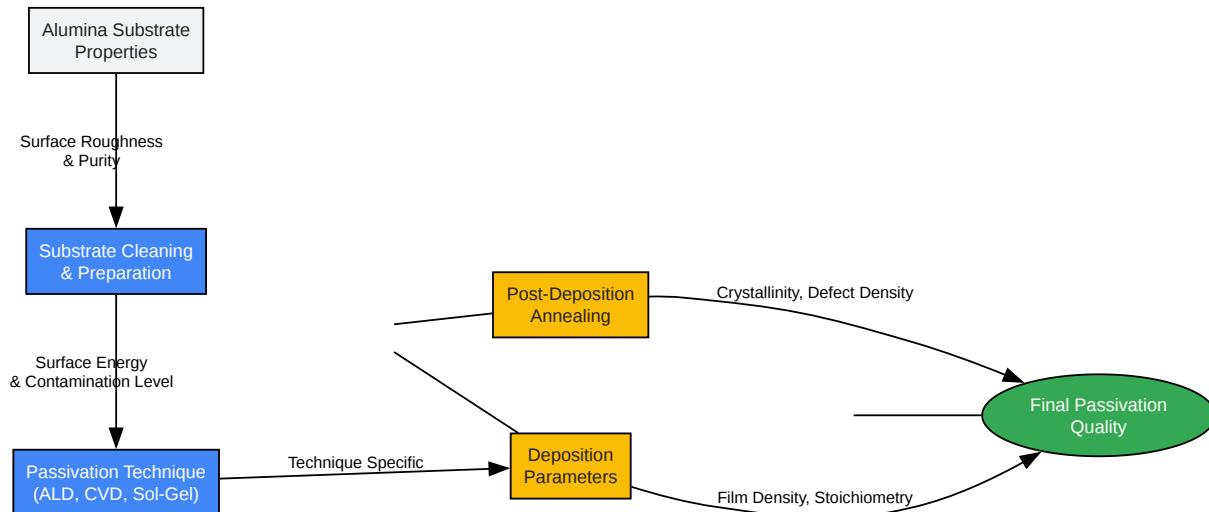

Caption: Factors influencing the final quality of surface passivation.

[Click to download full resolution via product page](#)

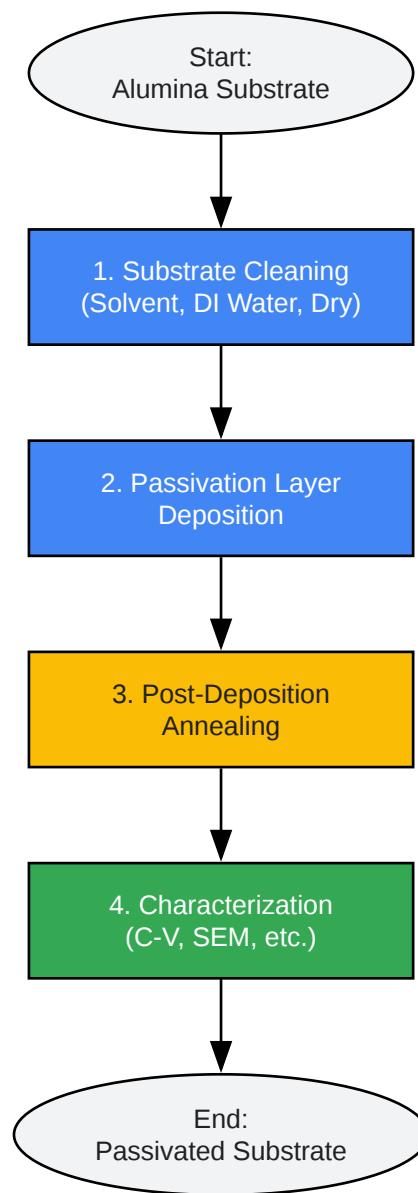

Caption: General experimental workflow for surface passivation.

[Click to download full resolution via product page](#)

Caption: The dual mechanisms of surface passivation.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [pjsir.org](http://pjsir.org) [pjsir.org]

- 2. [technotes.alconox.com](http://technotes.alconox.com) [technotes.alconox.com]

- 3. [nmfrc.org](http://nmfrc.org) [nmfrc.org]

- 4. [kta.com](http://kta.com) [kta.com]

- 5. [researchgate.net](http://researchgate.net) [researchgate.net]

- 6. [vb.nweurope.eu](http://vb.nweurope.eu) [vb.nweurope.eu]

- 7. ulprospector.com [ulprospector.com]

- 8. mdpi.com [mdpi.com]

- 9. pubs.acs.org [pubs.acs.org]

- 10. researchgate.net [researchgate.net]

- 11. researchgate.net [researchgate.net]

- 12. pubs.aip.org [pubs.aip.org]

- 13. sintef.no [sintef.no]

- 14. Influence of Process Conditions on the Growth and Texture of CVD Alpha-Alumina [mdpi.com]

- 15. researchgate.net [researchgate.net]

- 16. Passivation (chemistry) - Wikipedia [en.wikipedia.org]

- 17. researchgate.net [researchgate.net]

- 18. Passivation effects of atomic-layer-deposited aluminum oxide | EPJ Photovoltaics [epj-pv.org]

- 19. unipretec-ceramics.com [unipretec-ceramics.com]

- 20. 陶瓷材料溶胶-凝胶学 [sigmaaldrich.com]

- 21. US20060003100A1 - CVD process to deposit aluminum oxide coatings - Google Patents [patents.google.com]

- 22. mdpi.com [mdpi.com]

- 23. eds.yildiz.edu.tr [eds.yildiz.edu.tr]

- 24. mnccf.cense.iisc.ac.in [mnccf.cense.iisc.ac.in]

- 25. 4.3 Capacitance-Voltage Characteristics [iue.tuwien.ac.at]

- 26. drpradeepatuem.wordpress.com [drpradeepatuem.wordpress.com]

- 27. lab.semi.ac.cn [lab.semi.ac.cn]

- To cite this document: BenchChem. [Technical Support Center: Surface Passivation of Alumina-Based Electronic Substrates]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b075360#surface-passivation-techniques-for-alumina-based-electronic-substrates>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)