# Technical Support Center: Indium Telluride Memory Devices

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Indium telluride*

Cat. No.: B072746

[Get Quote](#)

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers and scientists working with **indium telluride** (InTe) and related chalcogenide phase-change memory (PCM) devices. The focus is on addressing the critical challenge of reducing the RESET current.

## Frequently Asked Questions (FAQs)

**Q1:** What are the primary causes of high RESET current in my InTe memory devices, and what are the main strategies to reduce it?

A high RESET current is a primary obstacle to developing low-power, high-density phase-change memory.<sup>[1][2]</sup> The RESET operation requires heating the phase-change material to its melting temperature (above 600°C for materials like GST) and then rapidly quenching it to achieve the amorphous, high-resistance state.<sup>[3]</sup> The current needed for this Joule heating ( $P = I^2R$ ) is the RESET current.

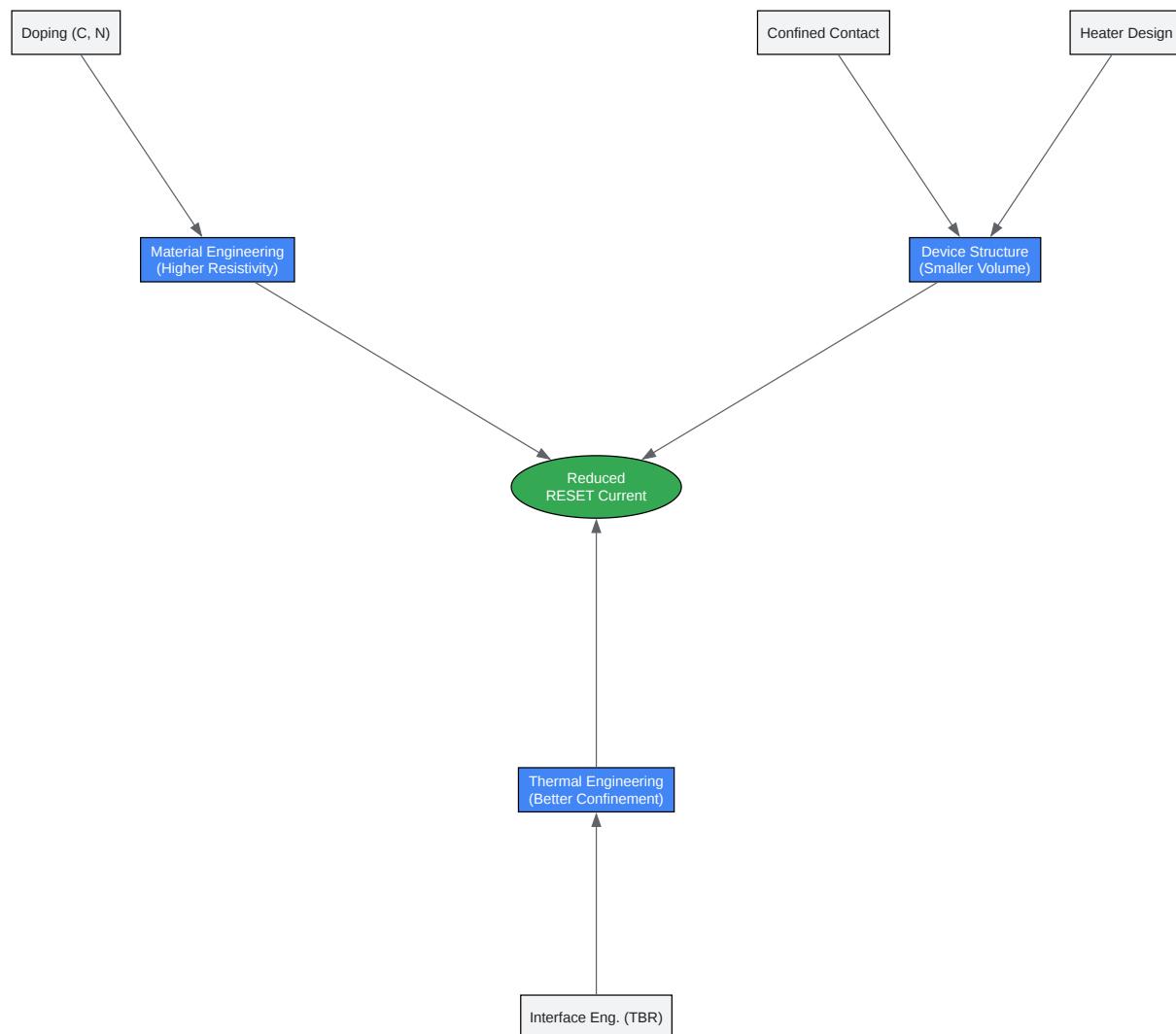

The main strategies to reduce this current fall into three categories:

- Material Engineering: Modifying the composition of the InTe alloy, primarily through doping, to increase its resistivity.<sup>[3][4]</sup>

- Device Structure Optimization: Reducing the active volume of the phase-change material that needs to be heated. This includes shrinking the contact area between the electrode and the InTe film.<sup>[3][5]</sup>

- Thermal Engineering: Improving the thermal confinement to ensure the generated heat is localized to the active region and not lost to the surroundings. This can be achieved through both device structure and interface engineering.[6]

Q2: How does doping the **indium telluride** material help in reducing the RESET current?

Doping the chalcogenide material is a highly effective method for reducing the RESET current. Introducing elements like carbon (C), nitrogen (N), or oxygen (O) into the material stack increases the resistivity of the crystalline (SET) state.[1][3][4] According to the Joule heating principle, a higher resistance material requires less current to generate the heat needed for amorphization.

For example, studies on the related GeSbTe (GST) material have shown that:

- Doping GST with 5% atomic content of carbon can reduce the RESET current by more than 50% compared to undoped GST.[4][7]

- Carbon doping in GeTe has been shown to lower the RESET current by about 30%. [8]

- Nitrogen doping also achieves a higher resistance material, leading to a reduced RESET current.[3]

Doping also influences other material properties, such as increasing the crystallization temperature, which can improve the thermal stability of the amorphous state and enhance data retention.[1][4]

Q3: In what ways can the physical device structure be modified to lower the RESET current?

The device architecture plays a crucial role in determining the magnitude of the RESET current. The primary goal of structural optimization is to minimize the volume of material that needs to be melted and to maximize heating efficiency.

Key structural approaches include:

- Reducing Contact Area: The RESET current scales almost linearly with the contact area of the device.[3] Creating a confined cell structure where the InTe material fills a small contact hole is a common strategy.[1]

- Edge Contact Devices: Using an edge contact, where the contact area is determined by the thickness of a thin film, can effectively diminish the contact area and increase the heater's thermal resistance, thereby reducing the required current.[3]

- Heater-Based Architectures: Implementing a dedicated heater element, such as in a "Wall" architecture, allows for more efficient and localized heating of the phase-change material.[5] This separates the heating element from the storage material, providing better control over the thermal profile.

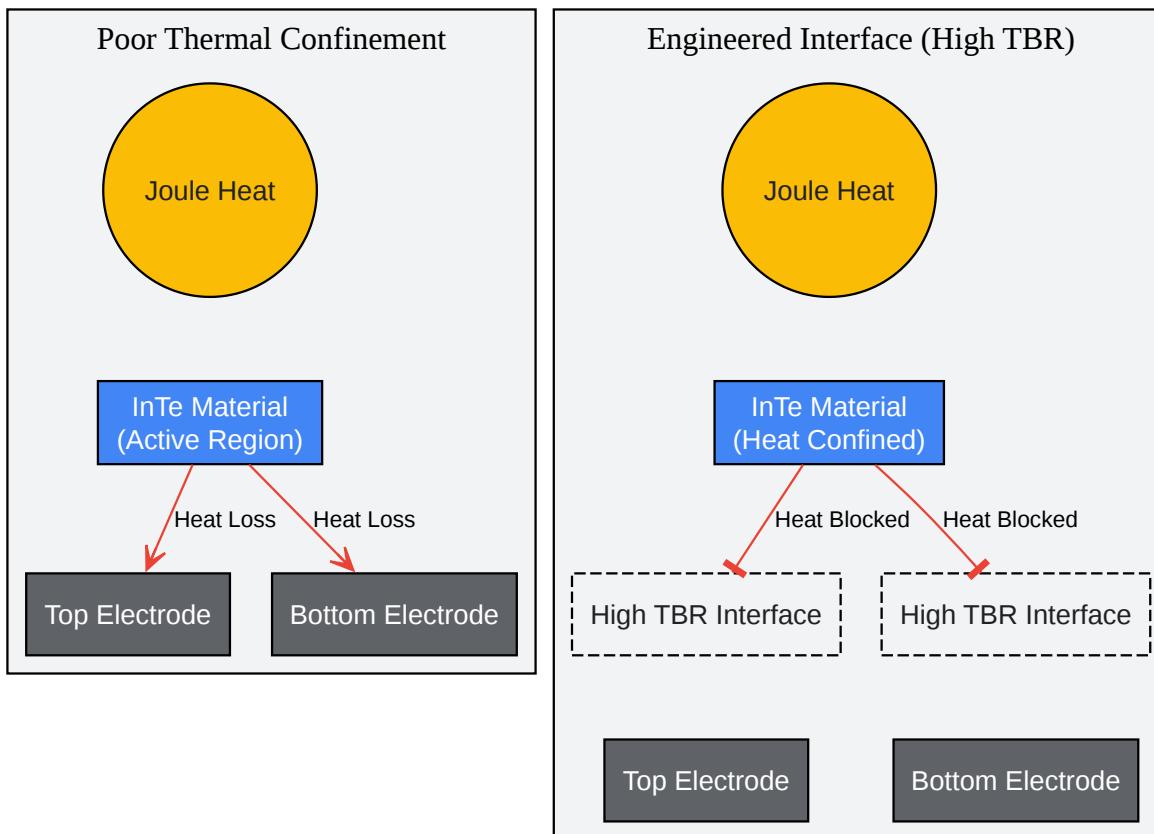

Q4: Can modifying the interfaces between the InTe film and the electrodes reduce the RESET current?

Yes, interface engineering is a powerful technique for thermal management. A significant amount of heat generated during the RESET pulse can be lost through the electrodes. By manipulating the thermal boundary resistance (TBR) at the interface between the phase-change material and the adjacent layers, you can create a thermal barrier.[6]

This improved thermal confinement ensures that more of the generated heat is kept within the active region of the InTe, reducing the total power needed to induce the phase change. Simulations have shown that increasing the interfacial resistance can reduce the RESET current by up to 40-50% without incorporating additional insulating layers, which could complicate fabrication.[6]

Q5: Are there any alternative programming methods that can achieve amorphization with lower energy?

Recent research on indium selenide ( $\text{In}_2\text{Se}_3$ ), a related material, has demonstrated a novel method for amorphization that avoids the energy-intensive melt-quench process altogether.[9] Instead of using a high-power thermal pulse, this technique induces amorphization through an electrical charge. This breakthrough approach has the potential to reduce the energy required for the RESET operation by a factor of up to one billion, addressing the core challenge of high power consumption in phase-change memories.[9]

Additionally, pre-programming techniques have been shown to be effective. A method involving a high-current RESET pulse followed by a DC SET pulse can control the active area size for subsequent operations, achieving a measurable reduction in the RESET current.[2]

# Troubleshooting Guide

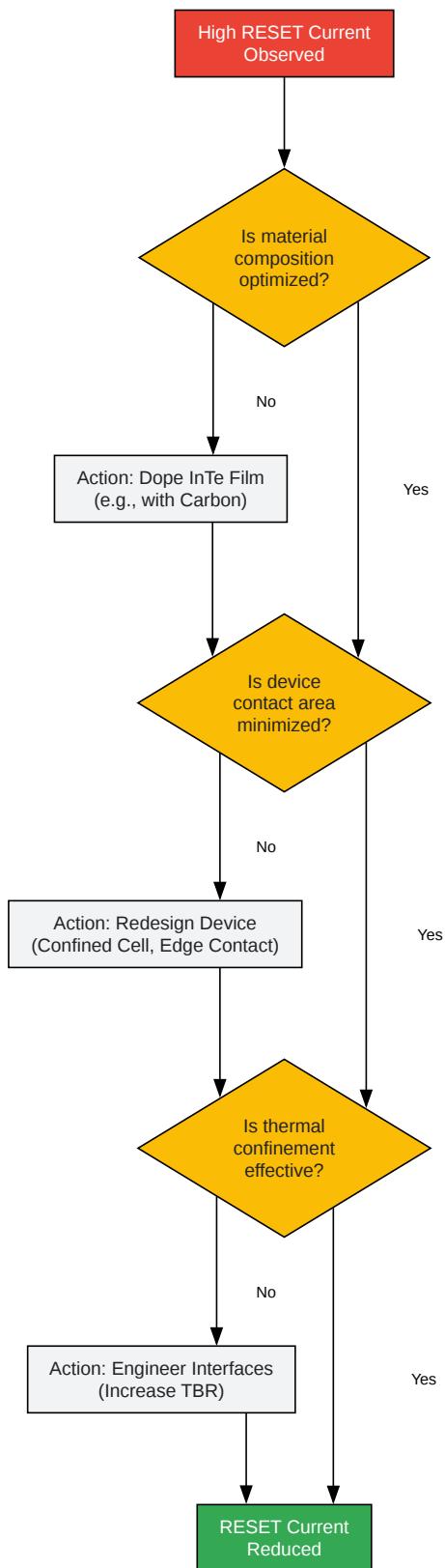

Problem: Consistently high RESET current leading to excessive power consumption.

| Possible Cause                     | Recommended Action                                                                                                                                                          | Experimental Protocol                                                                                                                                                                                                       |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Suboptimal Material Resistivity    | The intrinsic resistivity of your InTe film in the crystalline state may be too low, requiring high current for Joule heating.                                              | Introduce a dopant such as Carbon or Nitrogen into the InTe film during deposition. This increases the material's resistivity. <a href="#">[1]</a> <a href="#">[4]</a>                                                      |

| Large Active Volume / Contact Area | The entire area where the electrode contacts the InTe is being heated, leading to a large required current. The RESET current scales with contact size. <a href="#">[3]</a> | Redesign the device lithography to create a more confined structure. Utilize an "edge-contact" or "wall" architecture to minimize the active volume and improve heating efficiency. <a href="#">[3]</a> <a href="#">[5]</a> |

| Poor Thermal Confinement           | Significant heat generated during the RESET pulse is being dissipated through the top and bottom electrodes, wasting energy. <a href="#">[6]</a>                            | Focus on interface engineering to increase the thermal boundary resistance (TBR). This can be achieved by carefully selecting electrode materials and managing the interface quality during deposition. <a href="#">[6]</a> |

## Quantitative Data Summary

The following table summarizes key quantitative data from studies on reducing RESET current in chalcogenide memory devices. These values provide a reference for expected improvements.

| Technique                | Material System                                          | Parameter             | Result                   | Reference                                |

|--------------------------|----------------------------------------------------------|-----------------------|--------------------------|------------------------------------------|

| Carbon Doping            | Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub><br>(GST) | Carbon Content        | 5 at.%                   | >50% RESET<br>Current<br>Reduction       |

| Carbon Doping            | GeTe                                                     | Carbon Content        | 10 at.%                  | ~30% RESET<br>Current<br>Reduction       |

| Interface<br>Engineering | Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub><br>(GST) | Device Diameter       | 20 nm                    | Up to 40%<br>RESET Current<br>Reduction  |

| Interface<br>Engineering | Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub><br>(GST) | Device Diameter       | 120 nm                   | Up to 50%<br>RESET Current<br>Reduction  |

| Pre-<br>Programming      | Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub><br>(GST) | Programming<br>Method | High I-RESET +<br>DC SET | 0.3 mA max<br>RESET Current<br>Reduction |

| Pulsed Mode<br>Switching | In <sub>2</sub> Se <sub>3</sub>                          | RESET Pulse           | 70 ns, 3.1 V             | Successful<br>RESET<br>operation         |

## Experimental Protocols

### Protocol 1: Co-Sputtering for Carbon-Doped Indium Telluride Films

This protocol describes a general method for fabricating carbon-doped InTe films, adapted from techniques used for similar chalcogenides like GST.[1][4]

- Target Preparation: Use separate high-purity **indium telluride** (or individual In and Te targets) and graphite (C) targets in a magnetron sputtering system.

- Substrate Preparation: Use standard substrates like SiO<sub>2</sub>/Si. Ensure substrates are thoroughly cleaned using a standard RCA clean or sonication in acetone and isopropyl alcohol.

- Deposition:

- Achieve a base pressure below  $5 \times 10^{-7}$  Torr in the sputtering chamber.

- Introduce high-purity Argon (Ar) as the sputtering gas.

- Maintain a constant sputtering power on the InTe target(s).

- Vary the sputtering power on the Carbon target to control the atomic percentage of carbon incorporated into the film. The exact power will need to be calibrated for your specific system.

- Deposit the film at room temperature to ensure it is in an amorphous state.

- Characterization:

- Use X-ray Photoelectron Spectroscopy (XPS) or Energy-Dispersive X-ray Spectroscopy (EDX) to confirm the atomic composition of the doped film.

- Fabricate memory cell devices using standard lithography and etching processes.

- Perform electrical characterization to measure the R-I (Resistance-Current) curve and determine the new, lower RESET current.

#### Protocol 2: Characterization of the RESET Operation

This protocol outlines the electrical testing procedure to measure the RESET current of a fabricated memory cell.

- Equipment: A semiconductor parameter analyzer or a combination of a pulse generator and a source-measure unit (SMU).

- Initial State: Ensure the device is in the low-resistance (SET) state. If the as-fabricated device is in the high-resistance (RESET) state, apply a long, low-amplitude voltage pulse (e.g., 1V for 1μs) to crystallize the material.

- R-I Measurement:

- Apply a series of voltage or current pulses with increasing amplitude.

- The pulse width should be short, typically in the range of 10-100 ns, to allow for rapid heating and quenching.[3][10]

- After each programming pulse, use a small read voltage (e.g., 0.1V) to measure the resistance of the cell without disturbing its state.

- Plot the cell resistance as a function of the programming pulse amplitude.

- Determining RESET Current: The RESET current is the minimum current required in a short pulse that causes the device to switch from the low-resistance state to the high-resistance state. This will be visible as a sharp increase in resistance in your R-I plot.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for addressing high RESET current.

[Click to download full resolution via product page](#)

Caption: Key relationships in reducing device RESET current.

[Click to download full resolution via product page](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. Professor Robert B. Laughlin, Department of Physics, Stanford University [large.stanford.edu]

- 4. Lowering the Reset Current and Power Consumption of Phase-Change Memories with Carbon-Doped Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> | IEEE Conference Publication | IEEE Xplore [[ieeexplore.ieee.org](https://ieeexplore.ieee.org)]

- 5. [researchgate.net](https://www.researchgate.net) [[researchgate.net](https://www.researchgate.net)]

- 6. Interface controlled thermal resistances of ultra-thin chalcogenide-based phase change memory devices - PMC [[pmc.ncbi.nlm.nih.gov](https://www.ncbi.nlm.nih.gov)]

- 7. [researchgate.net](https://www.researchgate.net) [[researchgate.net](https://www.researchgate.net)]

- 8. Carbon-doped GeTe Phase-Change Memory featuring remarkable RESET current reduction | IEEE Conference Publication | IEEE Xplore [[ieeexplore.ieee.org](https://ieeexplore.ieee.org)]

- 9. [abachy.com](https://www.abachy.com) [[abachy.com](https://www.abachy.com)]

- 10. Phase-Change Memory from Molecular Tellurides - PMC [[pmc.ncbi.nlm.nih.gov](https://www.ncbi.nlm.nih.gov)]

- To cite this document: BenchChem. [Technical Support Center: Indium Telluride Memory Devices]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b072746#reducing-reset-current-in-indium-telluride-memory-devices>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)