# Reducing contact resistance in P3HT-based OTFTs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## *Compound of Interest*

Compound Name: 3-Hexadecylthiophene

Cat. No.: B052687

[Get Quote](#)

## Technical Support Center: P3HT-Based OTFTs

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers, scientists, and drug development professionals working with Poly(3-hexylthiophene) (P3HT)-based Organic Thin-Film Transistors (OTFTs), with a specific focus on mitigating high contact resistance.

## Frequently Asked Questions (FAQs)

**Q1:** What is contact resistance in P3HT OTFTs and why is it problematic?

**A1:** Contact resistance is the opposition to current flow at the interface between the metal source/drain electrodes and the P3HT semiconductor layer. High contact resistance can significantly limit the overall performance of the transistor, leading to reduced drain current, lower calculated field-effect mobility, and increased power consumption. It can become a dominant limiting factor, especially in short-channel devices.[\[1\]](#)[\[2\]](#)[\[3\]](#)

**Q2:** What are the primary causes of high contact resistance in P3HT OTFTs?

**A2:** High contact resistance in P3HT OTFTs typically stems from a few key factors:

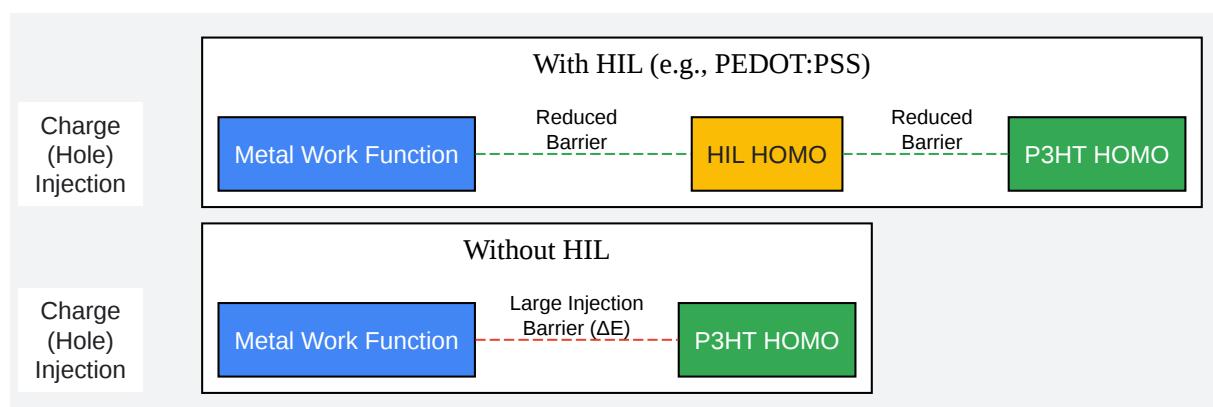

- Energy Barrier: A significant energy barrier between the work function of the metal electrode and the highest occupied molecular orbital (HOMO) of the P3.[\[4\]](#)

- Poor Interfacial Morphology: Incomplete or disordered contact between the electrode and the P3HT film can reduce the effective area for charge injection.

- Unfavorable Molecular Ordering: The orientation of P3HT chains at the interface can impact charge injection. Efficient injection is favored when there is strong  $\pi$ - $\pi$  stacking.[\[5\]](#)[\[6\]](#)

- Contamination: The presence of contaminants or residue at the interface can impede charge transfer.

Q3: What are some common strategies to reduce contact resistance?

A3: Several strategies can be employed to lower contact resistance:

- Electrode Modification: Introducing a hole-injection layer (HIL) like PEDOT:PSS or Graphene Oxide (GO) between the metal electrode and the P3HT can reduce the injection barrier.[\[4\]](#)[\[7\]](#)[\[8\]](#)

- Surface Treatment of Dielectric: Modifying the dielectric surface with self-assembled monolayers (SAMs) like octadecyltrichlorosilane (OTS) can improve the ordering of the P3HT film, which indirectly benefits charge injection.[\[5\]](#)[\[6\]](#)

- Choice of Electrode Metal: Using high work function metals like gold (Au) or palladium (Pd) can lead to a better energy level alignment with P3HT.[\[9\]](#)

- Device Architecture: Top-contact device structures can sometimes offer lower contact resistance compared to bottom-contact structures as the semiconductor layer is formed first, potentially leading to a cleaner interface.[\[9\]](#)

Q4: How is contact resistance typically measured and characterized?

A4: The most common method for determining contact resistance is the Transmission Line Method (TLM).[\[3\]](#)[\[10\]](#) This involves fabricating transistors with identical channel widths but varying channel lengths. By plotting the total device resistance against the channel length, the contact resistance can be extracted from the y-intercept. Other techniques include the Y-function method and the gated four-point probe method.[\[11\]](#)

## Troubleshooting Guide

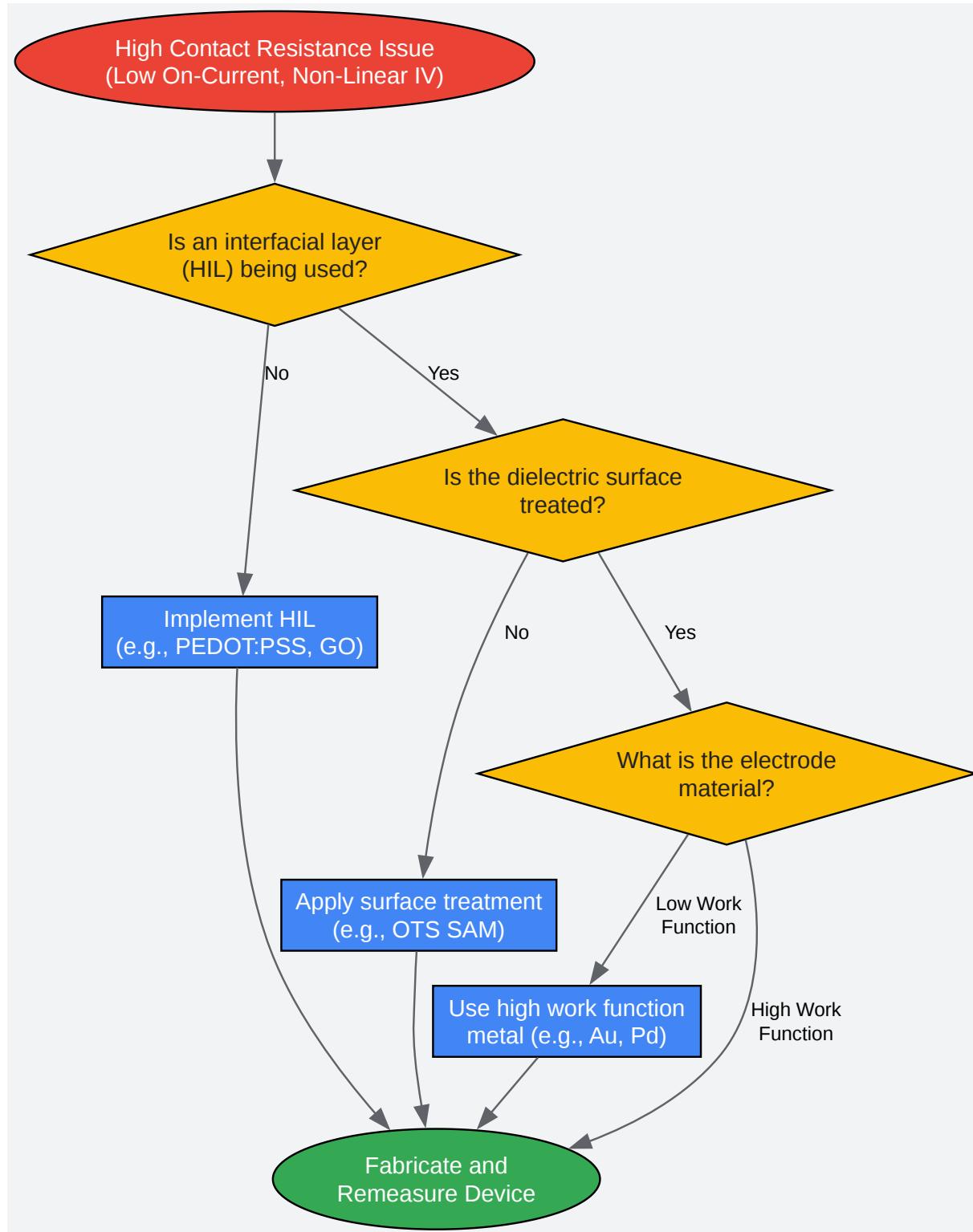

This guide is designed to help you diagnose and resolve common issues related to high contact resistance in your P3HT OTFT experiments.

| Problem                                           | Potential Cause(s)                                                                                  | Recommended Solution(s)                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low 'On' Current and Underestimated Mobility      | High contact resistance is limiting charge injection.                                               | <ol style="list-style-type: none"><li>1. Introduce a hole-injection layer (e.g., PEDOT:PSS or Graphene Oxide).</li><li>2. Treat the dielectric surface with a self-assembled monolayer (e.g., OTS).</li><li>3. Ensure the use of a high work function metal for the electrodes (e.g., Au, Pd).</li></ol> |

| Non-linear Output Characteristics at Low $V_{ds}$ | A significant Schottky barrier is present at the source contact, impeding charge injection.         | <ol style="list-style-type: none"><li>1. Functionalize the electrode surface with a suitable SAM to reduce the injection barrier.</li><li>2. Use a hole-injection layer like PEDOT:PSS to create a more ohmic contact.<sup>[4]</sup></li></ol>                                                           |

| Poor Device-to-Device Reproducibility             | Inconsistent surface preparation or contamination.                                                  | <ol style="list-style-type: none"><li>1. Implement a stringent and consistent substrate cleaning protocol.</li><li>2. Perform fabrication steps in a clean environment (e.g., a glovebox or cleanroom) to minimize airborne contaminants.</li></ol>                                                      |

| Degradation of Performance Over Time              | Environmental factors (e.g., oxygen, moisture) are affecting the electrode-semiconductor interface. | <ol style="list-style-type: none"><li>1. Encapsulate the devices to protect them from the ambient environment.</li><li>2. Perform measurements in an inert atmosphere (e.g., nitrogen or argon).</li></ol>                                                                                               |

## Experimental Protocols

### Protocol 1: PEDOT:PSS Hole-Injection Layer Deposition

This protocol describes how to deposit a PEDOT:PSS layer on gold electrodes to reduce the hole-injection barrier.[\[4\]](#)

- Substrate Preparation: Begin with pre-patterned gold electrodes on your chosen substrate (e.g., Si/SiO<sub>2</sub>).

- Cleaning: Thoroughly clean the substrate by sonicating in a sequence of deionized water, acetone, and isopropanol for 10-15 minutes each. Dry the substrate with a stream of nitrogen.

- PEDOT:PSS Solution: Use a filtered, commercially available PEDOT:PSS solution.

- Spin Coating: Dispense the PEDOT:PSS solution onto the substrate. Spin-coat at a speed of 3000-5000 rpm for 60 seconds to achieve a thin, uniform film.

- Annealing: Bake the substrate on a hotplate at 120-150°C for 10-15 minutes to remove residual water and solvent.

- P3HT Deposition: Proceed with the deposition of the P3HT active layer as per your standard procedure.

#### Protocol 2: Graphene Oxide (GO) Interfacial Layer

This protocol outlines the use of a virgin Graphene Oxide (GO) layer to enhance device performance by reducing contact resistance.[\[7\]](#)[\[8\]](#)

- Substrate Preparation: Use a Bottom-Gate Bottom-Contact (BGBC) device structure with pre-patterned Au electrodes on a SiO<sub>2</sub> dielectric.

- GO Dispersion: Obtain a stable aqueous dispersion of GO (e.g., 5 mg/mL).

- Deposition: The method of deposition can be spin-coating. The parameters will need to be optimized to achieve a monolayer or a thin, uniform layer.

- P3HT Deposition: Following the GO deposition, spin-coat the P3HT solution (e.g., 0.48 wt% in chloroform) onto the wafer. For instance, use a two-step spin-coating process with a final speed of 2000 rpm for 60 seconds.[\[8\]](#)

- Annealing: Anneal the P3HT film at approximately 110°C for 1 hour.[8]

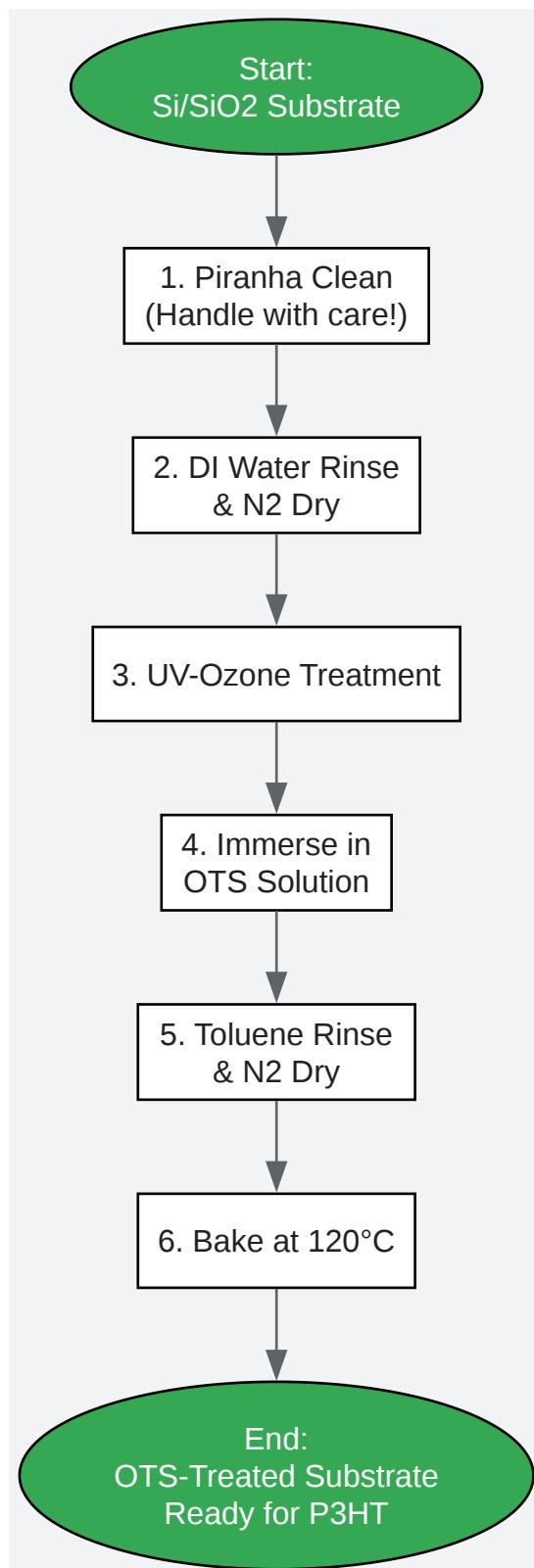

#### Protocol 3: Octadecyltrichlorosilane (OTS) Surface Treatment

This protocol details the surface treatment of a SiO<sub>2</sub> gate dielectric to improve the molecular ordering of the P3HT film.[5][6]

- Substrate Cleaning: Clean the Si/SiO<sub>2</sub> substrates in a piranha solution (a 3:1 mixture of sulfuric acid and 30% hydrogen peroxide) for 15-20 minutes. (Caution: Piranha solution is extremely corrosive and must be handled with extreme care in a fume hood with appropriate personal protective equipment).

- Rinsing and Drying: Rinse the substrates thoroughly with deionized water and then dry them with a nitrogen gun.

- UV-Ozone Treatment: Expose the substrates to UV-ozone for 10-15 minutes to remove any organic residues and to hydroxylate the surface.

- OTS Solution Preparation: Prepare a dilute solution of OTS in a non-polar solvent like toluene or hexadecane (e.g., 0.1 wt%).

- Immersion: Immerse the cleaned substrates in the OTS solution for a specified time (this can range from 30 minutes to several hours depending on the desired monolayer quality).

- Rinsing: After immersion, rinse the substrates with fresh solvent (toluene or hexadecane) to remove any excess, unreacted OTS.

- Baking: Bake the substrates at 120°C for 10 minutes to complete the silanization reaction.

- P3HT Deposition: The OTS-treated substrates are now ready for P3HT deposition.

## Data Summary

The following table summarizes the impact of various contact modification techniques on the performance of P3HT OTFTs.

| Modification Technique                                 | Effect on Contact Resistance       | Effect on Field-Effect Mobility                                                                                      | Reference |

|--------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------|

| PEDOT:PSS on Au electrodes                             | Significant reduction.             | Improvement from 0.031 to 0.218 cm <sup>2</sup> /Vs.                                                                 | [4]       |

| Graphene Oxide Interfacial Layer                       | Noticed decrease.                  | Considerable increase.                                                                                               | [7][8]    |

| OTS surface treatment                                  | Minimized in top-contact geometry. | Higher hole mobility (~0.072 cm <sup>2</sup> /Vs) compared to untreated (~5 x 10 <sup>-3</sup> cm <sup>2</sup> /Vs). | [5][6]    |

| Naphthalene (NL) functionalization on Au contacts      | Reduced by a factor of 16.         | Similar hole mobilities of about 10 <sup>-3</sup> cm <sup>2</sup> /Vs.                                               | [12]      |

| Pentacenequinone (PQ) functionalization on Au contacts | Reduced by a factor of 2.          | Similar hole mobilities of about 10 <sup>-3</sup> cm <sup>2</sup> /Vs.                                               | [12]      |

## Visual Guides

[Click to download full resolution via product page](#)

Caption: Energy level alignment at the electrode-semiconductor interface.

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for high contact resistance.

[Click to download full resolution via product page](#)

Caption: Experimental workflow for OTS surface treatment.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Contact resistance of organic TFTs [fkf.mpg.de]

- 2. fkf.mpg.de [fkf.mpg.de]

- 3. Request Rejected [ieeexplore.ieee.org]

- 4. researchgate.net [researchgate.net]

- 5. pubs.aip.org [pubs.aip.org]

- 6. pubs.aip.org [pubs.aip.org]

- 7. mdpi.com [mdpi.com]

- 8. Poly(3-hexylthiophene)-Based Organic Thin-Film Transistors with Virgin Graphene Oxide as an Interfacial Layer - PMC [pmc.ncbi.nlm.nih.gov]

- 9. pure.psu.edu [pure.psu.edu]

- 10. researchgate.net [researchgate.net]

- 11. researchgate.net [researchgate.net]

- 12. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Reducing contact resistance in P3HT-based OTFTs]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b052687#reducing-contact-resistance-in-p3ht-based-otfts>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)