# strategies to improve performance of 3,3'-Dihexyl-2,2'-bithiophene devices

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## *Compound of Interest*

Compound Name: **3,3'-Dihexyl-2,2'-bithiophene**

Cat. No.: **B173766**

[Get Quote](#)

## Technical Support Center: 3,3'-Dihexyl-2,2'-bithiophene (DHBT) Devices

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing the performance of **3,3'-Dihexyl-2,2'-bithiophene** (DHBT) based electronic devices.

## Frequently Asked Questions (FAQs) & Troubleshooting

This section addresses common issues encountered during the fabrication and characterization of DHBT devices.

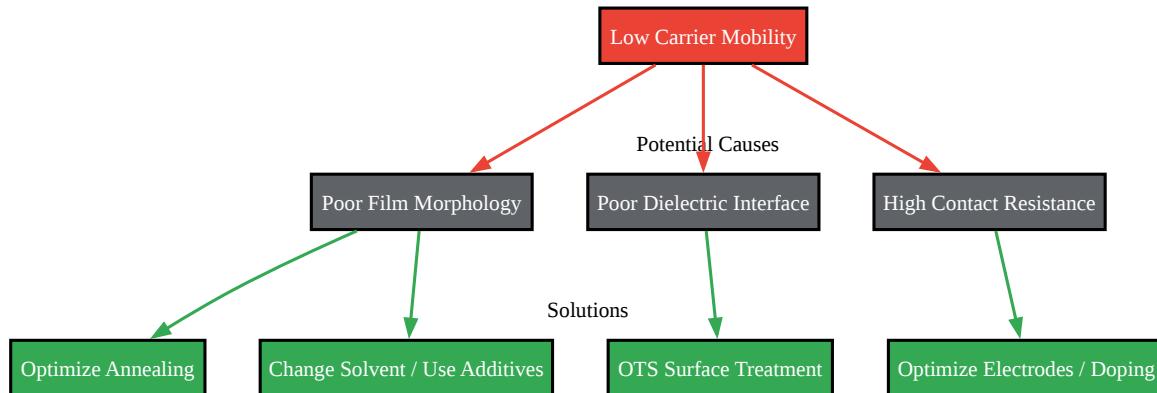

**Q1:** My DHBT Organic Field-Effect Transistor (OFET) shows low charge carrier mobility. What are the potential causes and how can I improve it?

**A1:** Low charge carrier mobility in DHBT OFETs can stem from several factors related to the morphology of the semiconductor film and the quality of the interfaces. Here are the primary causes and troubleshooting strategies:

- **Suboptimal Film Morphology:** The degree of molecular ordering in the DHBT thin film is critical for efficient charge transport.

- Troubleshooting:

- Annealing: Thermal annealing can significantly improve the crystallinity of the DHBT film. Experiment with a range of annealing temperatures and times. For similar thiophene-based polymers like P3HT, annealing temperatures between 100°C and 150°C have shown to enhance mobility.[1]

- Solvent Selection: The choice of solvent for dissolving DHBT affects the film's morphology. Solvents with higher boiling points can allow for more ordered film formation during spin-coating.[2][3]

- Solvent Vapor Annealing: Exposing the DHBT film to a solvent vapor atmosphere can also promote molecular rearrangement and improve crystallinity.[2][4][5]

- Poor Dielectric Interface: The interface between the gate dielectric and the DHBT semiconductor layer plays a crucial role in charge accumulation and transport.

- Troubleshooting:

- Substrate Treatment: Treating the dielectric surface with a self-assembled monolayer (SAM) like octadecyltrichlorosilane (OTS) can improve the ordering of DHBT molecules at the interface and reduce charge trapping.

- Dielectric Surface Roughness: A rough dielectric surface can disrupt the formation of a well-ordered DHBT film, leading to increased scattering and lower mobility. Ensure your dielectric layer is as smooth as possible.

- High Contact Resistance: Poor injection of charge carriers from the source electrode to the DHBT semiconductor can limit the measured mobility.

- Troubleshooting:

- Electrode Material: Ensure the work function of your source/drain electrodes is well-matched with the HOMO level of DHBT for efficient hole injection.

- Contact Doping: Introducing a thin p-dopant layer at the electrode-semiconductor interface can reduce the contact resistance.[6]

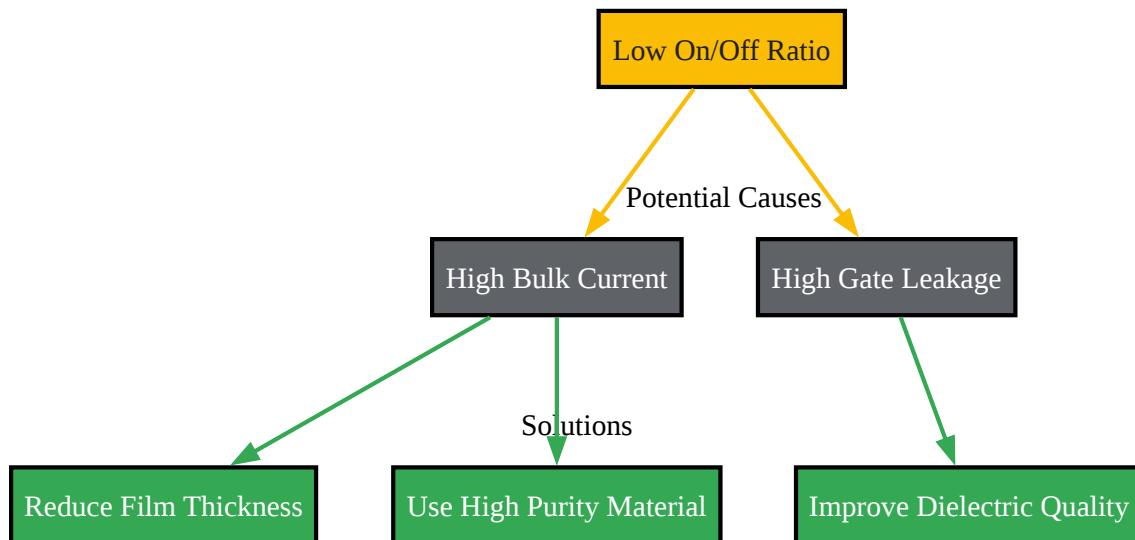

Q2: I am observing a high off-current in my DHBT transistor, leading to a low on/off ratio. What could be the reason and how can I fix it?

A2: A high off-current, which degrades the on/off ratio, is a common issue in OFETs. The primary causes are often related to bulk conductivity of the semiconductor or gate leakage.

- Bulk Conduction: If the DHBT film is too thick or has a high density of dopants/impurities, it can lead to significant current flow through the bulk of the material even when the channel is "off".

- Troubleshooting:

- Optimize Film Thickness: Reducing the thickness of the DHBT film can decrease the bulk current.<sup>[7]</sup> A thinner film confines charge transport more effectively to the channel region.

- Material Purity: Ensure the DHBT material used is of high purity to minimize unintentional doping.

- Gate Leakage Current: A significant current flowing from the gate electrode through the dielectric to the channel can contribute to the off-current.

- Troubleshooting:

- Dielectric Quality: Use a high-quality gate dielectric with low leakage current characteristics.

- Device Architecture: In some cases, optimizing the device architecture, such as using a dual-gate structure, can help control the off-current and improve the on/off ratio.<sup>[8][9]</sup>

Q3: My DHBT device exhibits significant hysteresis in its transfer characteristics. What is the cause of this, and how can I minimize it?

A3: Hysteresis, the difference in the transfer curve between forward and reverse gate voltage sweeps, is often caused by charge trapping phenomena.

- Charge Trapping at the Dielectric Interface: Trap states at the semiconductor-dielectric interface can capture and release charge carriers slowly, leading to a shift in the threshold voltage and hysteresis.[10][11]

- Troubleshooting:

- Surface Passivation: Treating the dielectric surface with a SAM like OTS can passivate trap states.

- Choice of Dielectric: Some dielectrics are more prone to causing hysteresis due to mobile ions or charge traps. Consider using a different dielectric material.

- Charge Trapping within the Semiconductor: Defects within the bulk of the DHBT film can also act as charge traps.

- Troubleshooting:

- Annealing: Thermal annealing can reduce the density of defects in the DHBT film.[1]

- Moisture and Oxygen: The presence of water or oxygen molecules can create trap states.

- Troubleshooting:

- Inert Atmosphere: Fabricate and measure your devices in an inert atmosphere (e.g., a glovebox) to minimize exposure to moisture and oxygen.

## Quantitative Data Summary

The following tables summarize the impact of various processing parameters on the performance of thiophene-based OFETs. While specific data for DHBT is limited in the literature, the trends observed for structurally similar materials like P3HT are highly relevant.

Table 1: Effect of Annealing Temperature on P3HT OFET Performance[1]

| Annealing Temperature (°C) | Hole Mobility (cm²/Vs)  | On/Off Ratio |

|----------------------------|-------------------------|--------------|

| No Annealing               | 0.0124 ( $\pm 0.0027$ ) | $> 10^4$     |

| 120                        | 0.0223 ( $\pm 0.0051$ ) | $> 10^4$     |

Table 2: Effect of Processing Additives and Annealing on P3HT OFET Mobility[1]

| Processing Additive      | Annealing   | Hole Mobility (cm²/Vs)  |

|--------------------------|-------------|-------------------------|

| None                     | No          | 0.0124 ( $\pm 0.0027$ ) |

| None                     | Yes (120°C) | 0.0223 ( $\pm 0.0051$ ) |

| 1-Chloronaphthalene (CN) | No          | 0.0609 ( $\pm 0.0085$ ) |

| 1-Chloronaphthalene (CN) | Yes (120°C) | 0.0914 ( $\pm 0.0120$ ) |

| 1,8-Diiodooctane (DIO)   | No          | 0.0364 ( $\pm 0.0099$ ) |

| 1,8-Diiodooctane (DIO)   | Yes (120°C) | 0.0937 ( $\pm 0.0127$ ) |

## Experimental Protocols

This section provides a detailed methodology for the fabrication of a top-contact, bottom-gate DHBT OFET.

### 1. Substrate Cleaning:

- Sequentially sonicate heavily n-doped Si wafers with a 300 nm thermally grown SiO<sub>2</sub> layer in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of nitrogen gas.

- Treat the substrates with UV-ozone for 10 minutes to remove any remaining organic residues and to hydroxylate the SiO<sub>2</sub> surface.

### 2. Dielectric Surface Treatment (Optional but Recommended):

- Prepare a 10 mM solution of octadecyltrichlorosilane (OTS) in anhydrous toluene.

- Immerse the cleaned substrates in the OTS solution for 30 minutes at room temperature inside a nitrogen-filled glovebox.

- Rinse the substrates with fresh toluene and then isopropanol.

- Anneal the substrates at 120°C for 30 minutes on a hotplate inside the glovebox.

### 3. DHBT Thin Film Deposition (Spin-Coating):

- Prepare a solution of **3,3'-Dihexyl-2,2'-bithiophene** (DHBT) in a suitable solvent (e.g., chloroform, chlorobenzene) at a concentration of 5-10 mg/mL.

- Filter the solution through a 0.2 µm PTFE syringe filter.

- Deposit the DHBT solution onto the substrate using a spin-coater. A two-step program is often effective:

- Step 1: 500 rpm for 10 seconds (to spread the solution).

- Step 2: 2000-4000 rpm for 30-60 seconds (to achieve the desired thickness).[\[12\]](#)

- Transfer the coated substrate to a hotplate inside the glovebox for thermal annealing. The optimal annealing temperature and time should be determined experimentally (e.g., start with 120°C for 15 minutes).[\[13\]](#)

### 4. Source-Drain Electrode Deposition:

- Deposit 50 nm of gold (Au) for the source and drain electrodes through a shadow mask using thermal evaporation at a rate of 0.1-0.2 Å/s. The base pressure of the evaporation chamber should be below 10<sup>-6</sup> Torr.

### 5. Device Characterization:

- Perform all electrical measurements in an inert atmosphere using a semiconductor parameter analyzer.

- Extract key performance metrics such as charge carrier mobility, on/off ratio, and threshold voltage from the transfer and output characteristics.

## Visualizations

The following diagrams illustrate key workflows and relationships in DHBT device fabrication and troubleshooting.

[Click to download full resolution via product page](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Synergistic Effects of Processing Additives and Thermal Annealing on Nanomorphology and Hole Mobility of Poly(3-hexylthiophene) Thin Films - PMC [pmc.ncbi.nlm.nih.gov]

- 2. mdpi.com [mdpi.com]

- 3. discovery.researcher.life [discovery.researcher.life]

- 4. mdpi.com [mdpi.com]

- 5. Effects of solvent vapor annealing on the optical properties and surface adhesion of conjugated D : A thin films - Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 6. researchgate.net [researchgate.net]

- 7. [pubs.aip.org](https://pubs.aip.org) [pubs.aip.org]

- 8. [publications.tno.nl](https://publications.tno.nl) [publications.tno.nl]

- 9. [researchgate.net](https://www.researchgate.net) [researchgate.net]

- 10. [mdpi.com](https://www.mdpi.com) [mdpi.com]

- 11. Effects of Charge Traps on Hysteresis in Organic Field-Effect Transistors and Their Charge Trap Cause Analysis through Causal Inference Techniques - PubMed [pubmed.ncbi.nlm.nih.gov]

- 12. [benchchem.com](https://www.benchchem.com) [benchchem.com]

- 13. [benchchem.com](https://www.benchchem.com) [benchchem.com]

- To cite this document: BenchChem. [strategies to improve performance of 3,3'-Dihexyl-2,2'-bithiophene devices]. BenchChem, [2026]. [Online PDF]. Available at: [https://www.benchchem.com/product/b173766#strategies-to-improve-performance-of-3-3-dihexyl-2-2-bithiophene-devices]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)