# Technical Support Center: 3,3'-Dihexyl-2,2'-bithiophene (DHBT) OFET Fabrication

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## Compound of Interest

Compound Name: 3,3'-Dihexyl-2,2'-bithiophene

Cat. No.: B173766

[Get Quote](#)

This guide provides troubleshooting advice and frequently asked questions for researchers and scientists fabricating Organic Field-Effect Transistors (OFETs) using the solution-processable organic semiconductor **3,3'-Dihexyl-2,2'-bithiophene** (DHBT).

## Frequently Asked Questions (FAQs)

**Q1:** What makes **3,3'-Dihexyl-2,2'-bithiophene** (DHBT) a suitable material for OFETs?

**A1:** **3,3'-Dihexyl-2,2'-bithiophene** is a specialized organic compound with favorable electronic properties for use in organic electronics.<sup>[1]</sup> Its bithiophene backbone provides good charge transport characteristics, while the dihexyl side chains enhance its solubility in common organic solvents.<sup>[1]</sup> This improved solubility and film-forming capability are crucial for developing high-performance electronic devices through solution-based processing techniques.<sup>[1]</sup>

**Q2:** What are the critical factors influencing the performance of DHBT OFETs?

**A2:** The performance of DHBT OFETs is primarily influenced by the morphology and crystallinity of the semiconductor thin film, the quality of the semiconductor-dielectric and electrode-semiconductor interfaces, and the overall device architecture. Key processing parameters that control these factors include the choice of solvent, deposition method, and post-deposition treatments such as thermal annealing.

**Q3:** What is a typical device architecture for a lab-scale DHBT OFET?

A3: A common and convenient architecture for laboratory-scale testing is the bottom-gate, top-contact (BGTC) or bottom-gate, bottom-contact (BGBC) configuration.[\[2\]](#) These typically utilize a heavily doped silicon wafer as the gate electrode with a thermally grown silicon dioxide ( $\text{SiO}_2$ ) layer as the gate dielectric.[\[3\]](#) The DHBT is then solution-deposited onto the dielectric, followed by the thermal evaporation of source and drain electrodes (for BGTC).[\[3\]](#)

## Troubleshooting Guide

### Low Carrier Mobility

Q: My DHBT OFET exhibits very low hole mobility. What are the potential causes and how can I improve it?

A: Low carrier mobility is a common issue that can stem from several factors throughout the fabrication process. Here's a breakdown of potential causes and solutions:

- Poor Film Morphology and Crystallinity: The arrangement of DHBT molecules in the thin film is critical for efficient charge transport.

- Solution: Optimize the solvent and deposition conditions. Solvents with slower evaporation rates can allow more time for molecular self-assembly, leading to more ordered films.[\[4\]](#) Experiment with different solvents such as chloroform, toluene, or dichlorobenzene. Additionally, consider post-deposition solvent vapor annealing to improve molecular ordering.[\[5\]](#)

- Sub-optimal Annealing Temperature: Thermal annealing is often necessary to improve the crystallinity of the organic semiconductor film.

- Solution: Systematically vary the annealing temperature and time. For many thiophene-based polymers, annealing at temperatures between 100°C and 150°C can enhance performance.[\[6\]](#)[\[7\]](#) However, excessive temperatures can lead to film degradation. It is crucial to find the optimal annealing conditions for DHBT.

- High Contact Resistance: A large potential drop at the interface between the source/drain electrodes and the DHBT film can impede charge injection and lead to an underestimation of the true mobility.[\[8\]](#)

- Solution: Ensure the work function of the electrode material (e.g., Gold) is well-matched with the HOMO level of DHBT for efficient hole injection.[9] Surface treatment of the electrodes or the semiconductor layer with self-assembled monolayers (SAMs) can reduce the contact barrier.[10]

- Traps at the Dielectric Interface: Defects and impurities at the semiconductor/dielectric interface can trap charge carriers, reducing mobility.

- Solution: Thoroughly clean the substrate before depositing the DHBT solution. Treating the dielectric surface with a hydrophobic self-assembled monolayer (SAM) like HMDS or OTS can reduce surface traps and promote better ordering of the DHBT film.

## High OFF Current / Low ON/OFF Ratio

Q: The ON/OFF ratio of my device is poor due to a high OFF current. What could be the reason?

A: A high OFF current suggests significant charge transport even when the transistor is supposed to be "off."

- Bulk Conduction: If the DHBT film is too thick, conduction may occur through the bulk of the film, which is not effectively modulated by the gate voltage.

- Solution: Reduce the thickness of the DHBT film by adjusting the solution concentration or spin-coating speed.

- Gate Leakage Current: A significant current flowing from the gate electrode through the dielectric to the channel can contribute to the measured OFF current.

- Solution: Verify the integrity of your gate dielectric. Pinholes or defects in the  $\text{SiO}_2$  can lead to leakage. Ensure proper cleaning and handling of the substrates.

- Impurities: Impurities in the DHBT material or residual solvent in the film can act as dopants, increasing the conductivity.

- Solution: Use high-purity DHBT. Ensure the film is thoroughly dried after deposition and annealing to remove any residual solvent.

## Device Instability and Hysteresis

Q: My OFET characteristics show significant hysteresis between forward and reverse voltage sweeps. What is causing this?

A: Hysteresis is often related to charge trapping phenomena.

- Mobile Ions: Contamination from processing chemicals or the environment can introduce mobile ions into the dielectric or at the interfaces.

- Solution: Maintain a clean fabrication environment and use high-purity materials.

- Slow Trap States: Traps at the semiconductor-dielectric interface or within the semiconductor bulk with slow charge trapping and de-trapping times can cause hysteresis.

- Solution: Improve the quality of the dielectric interface with SAM treatments. Proper thermal annealing can also reduce the density of bulk traps.[11]

- Water and Oxygen: Adsorbed water or oxygen molecules can act as charge traps.

- Solution: Fabricate and characterize the devices in an inert atmosphere (e.g., a nitrogen-filled glovebox). If testing in air, ensure the device is properly encapsulated.

## Quantitative Data Summary

While extensive quantitative data for **3,3'-Dihexyl-2,2'-bithiophene** is not readily available in the provided search results, the following table presents typical performance parameters for OFETs based on a well-studied thiophene-based polymer, P3HT. This data is intended to provide a general benchmark for expected performance and illustrates the impact of processing conditions.

| Parameter                            | Value                                          | Conditions                                                      | Reference |

|--------------------------------------|------------------------------------------------|-----------------------------------------------------------------|-----------|

| Hole Mobility ( $\mu$ )              | $\sim 0.1 \text{ cm}^2/\text{Vs}$              | Regioregular P3HT,<br>dip-coated                                | [6]       |

|                                      | $\sim 0.023 \text{ cm}^2/\text{Vs}$            | Pristine P3HT film                                              | [5]       |

| up to $0.102 \text{ cm}^2/\text{Vs}$ | P3HT film with solvent<br>vapor annealing      | [5]                                                             |           |

| ON/OFF Ratio                         | $> 3.3 \times 10^4$                            | P3HT device                                                     | [12]      |

| Threshold Voltage<br>( $V_{th}$ )    | $\sim -23.4 \text{ V}$                         | P3HT device                                                     | [12]      |

| Contact Resistance<br>( $R_c$ )      | $1.7 \text{ M}\Omega$ to $0.6 \text{ M}\Omega$ | P3HT with Ti/Pt<br>electrodes, dependent<br>on molecular weight | [10]      |

## Experimental Protocols

### Fabrication of a Bottom-Gate, Top-Contact DHBT OFET

This protocol outlines a typical procedure for fabricating a DHBT OFET.

- Substrate Cleaning:

- Use heavily n-doped Si wafers with a 300 nm thermally grown  $\text{SiO}_2$  layer as the substrate.

- Sequentially sonicate the substrates in a cleaning solution (e.g., Decon 90 or similar), deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of dry nitrogen and bake at  $120^\circ\text{C}$  for 20 minutes to remove any residual moisture.

- Dielectric Surface Treatment (Optional but Recommended):

- Treat the  $\text{SiO}_2$  surface with a self-assembled monolayer (SAM) to improve the interface quality. For example, expose the substrates to hexamethyldisilazane (HMDS) vapor in a vacuum oven at  $120^\circ\text{C}$  for 30 minutes.

- DHBT Solution Preparation:

- Prepare a solution of **3,3'-Dihexyl-2,2'-bithiophene** in a suitable solvent (e.g., chloroform, toluene) at a concentration of 5-10 mg/mL.

- Gently heat and stir the solution to ensure complete dissolution.

- Before use, filter the solution through a 0.2 µm PTFE syringe filter.

- DHBT Film Deposition:

- Deposit the DHBT solution onto the prepared substrate using spin-coating. Typical parameters are 2000-4000 rpm for 60 seconds. The spin speed should be optimized to achieve the desired film thickness.

- Perform this step in an inert atmosphere (glovebox) to minimize exposure to air and moisture.

- Thermal Annealing:

- Anneal the DHBT film on a hotplate inside the glovebox. A typical starting point is to anneal at 120°C for 30 minutes. This step is crucial for improving film crystallinity and device performance.[6][7]

- Source-Drain Electrode Deposition:

- Thermally evaporate Gold (Au) electrodes through a shadow mask to define the source and drain contacts. A typical thickness is 50 nm, with a thin (5 nm) adhesion layer of Chromium (Cr) or Titanium (Ti).

- The channel length (L) and width (W) are defined by the shadow mask dimensions.

- Characterization:

- Measure the electrical characteristics of the OFET using a semiconductor parameter analyzer in an inert atmosphere or in air, if the device is stable.

- Extract key parameters such as mobility ( $\mu$ ), ON/OFF ratio, and threshold voltage ( $V_{th}$ ) from the transfer and output characteristics.

## Visual Guides

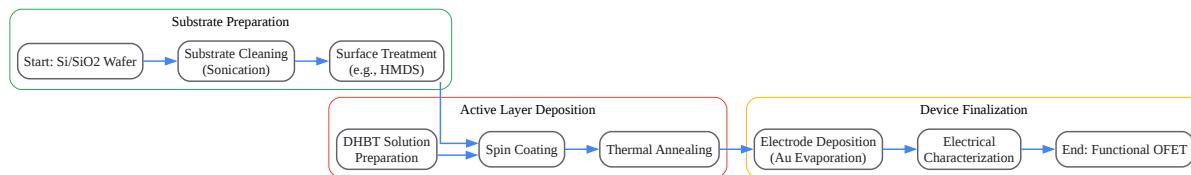

### DHBT OFET Fabrication Workflow

[Click to download full resolution via product page](#)

Caption: A typical workflow for the fabrication of a bottom-gate, top-contact DHBT OFET.

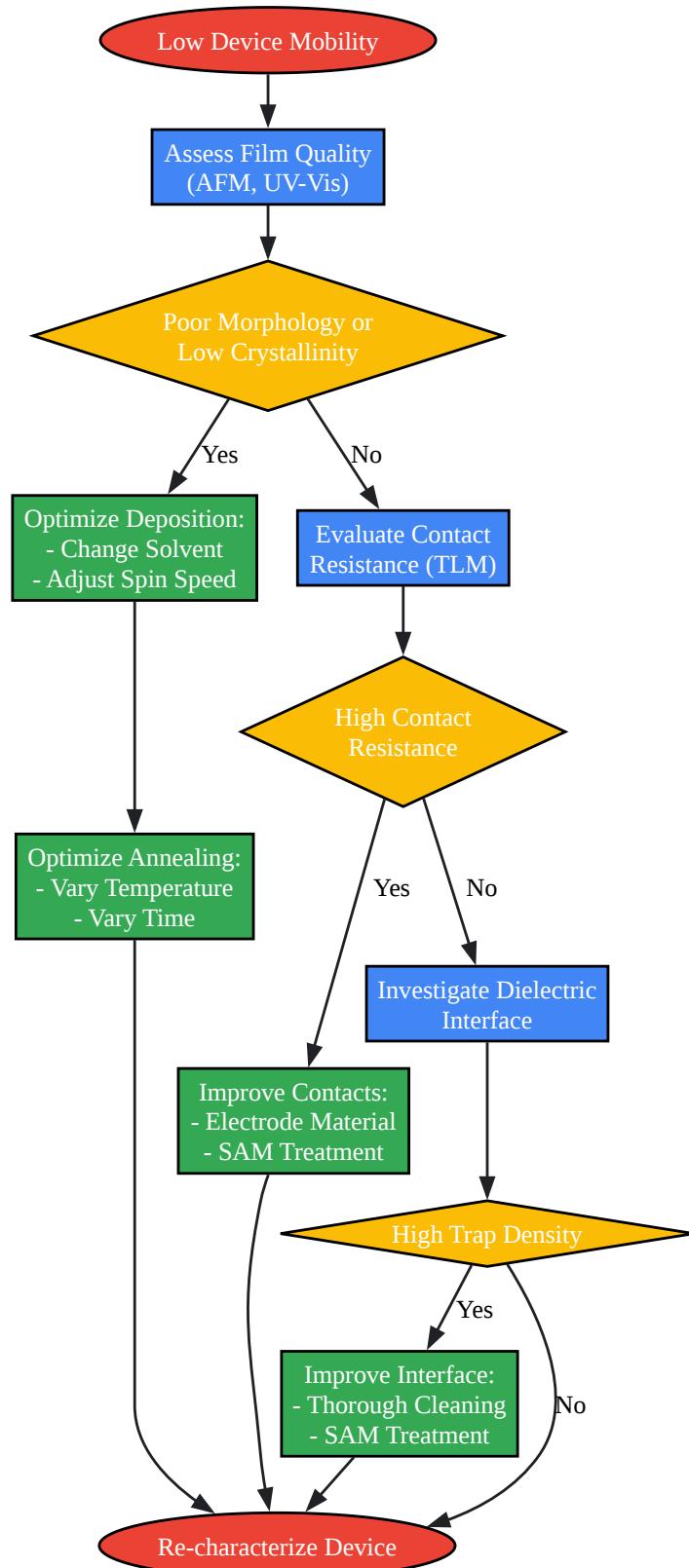

## Troubleshooting Logic for Low Mobility

[Click to download full resolution via product page](#)

Caption: A decision tree for troubleshooting low carrier mobility in DHBT OFETs.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. chemimpex.com [chemimpex.com]

- 2. pubs.aip.org [pubs.aip.org]

- 3. researchgate.net [researchgate.net]

- 4. researchspace.csir.co.za [researchspace.csir.co.za]

- 5. Effects of Solvent Vapor Annealing on Morphology and Charge Transport of Poly(3-hexylthiophene) (P3HT) Films Incorporated with Preformed P3HT Nanowires [mdpi.com]

- 6. docnum.umons.ac.be [docnum.umons.ac.be]

- 7. researchgate.net [researchgate.net]

- 8. Mobility overestimation due to gated contacts in organic field-effect transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 9. jics.org.br [jics.org.br]

- 10. researchgate.net [researchgate.net]

- 11. researchgate.net [researchgate.net]

- 12. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: 3,3'-Dihexyl-2,2'-bithiophene (DHBT) OFET Fabrication]. BenchChem, [2026]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b173766#troubleshooting-guide-for-3-3-dihexyl-2-2-bithiophene-ofet-fabrication>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)