# comparative analysis of SiPc electron mobility in different device architectures

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## Compound of Interest

Compound Name: *Silicon phthalocyanine*

Cat. No.: *B1681755*

[Get Quote](#)

An In-Depth Comparative Analysis of **Silicon Phthalocyanine** (SiPc) Electron Mobility in Different Device Architectures

## Introduction: The Promise of Silicon Phthalocyanine in Organic Electronics

**Silicon Phthalocyanine** (SiPc) has emerged as a distinct and promising organic semiconductor, drawing significant attention from the research community.<sup>[1]</sup> Unlike many other planar phthalocyanines, the silicon core of SiPc allows for two additional axial bonds. These out-of-plane ligands can be synthetically tailored to prevent the strong intermolecular aggregation that often plagues other phthalocyanines, thereby modulating its electronic and optical properties.<sup>[1]</sup> This unique structural feature, combined with its robust thermal stability and intense absorption in the far-red region of the spectrum, makes SiPc a compelling candidate for a range of electronic applications, including organic field-effect transistors (OFETs) and photovoltaic cells.<sup>[1][2]</sup>

A critical parameter governing the performance of these devices is the charge carrier mobility ( $\mu$ ), which quantifies how quickly an electron or hole can move through the material under the influence of an electric field.<sup>[3][4]</sup> High electron mobility is particularly sought after for n-channel transistors, a key component in complementary logic circuits. The measured electron mobility of SiPc, however, is not an intrinsic constant; it is profoundly influenced by the architecture of the device used for its measurement. Factors such as the semiconductor-

dielectric interface, the quality of the source-drain contacts, and the morphology of the SiPc thin film are all dictated by the device structure.

This guide provides a comparative analysis of SiPc electron mobility across different device architectures, primarily focusing on Organic Field-Effect Transistors (OFETs). We will dissect the causality behind performance variations, provide validated experimental protocols, and present a clear, data-driven comparison to empower researchers in materials science and device engineering to make informed design choices.

## Fundamentals of Charge Transport in Phthalocyanine Films

In organic semiconductors like SiPc, charge transport occurs through the overlap of  $\pi$ -orbitals between adjacent molecules. Unlike inorganic semiconductors with their delocalized energy bands, charge carriers in organic materials are more localized.<sup>[5]</sup> The transport mechanism is often described as "hopping," where an electron jumps from one molecule to the next. The efficiency of this process is highly dependent on:

- Molecular Packing (Polymorphism): The relative arrangement and orientation of SiPc molecules in the thin film are critical. A well-ordered, co-facial  $\pi$ -stacking arrangement maximizes orbital overlap, creating efficient pathways for charge transport.<sup>[5]</sup>

- Structural and Energetic Disorder: Defects, impurities, and grain boundaries within the polycrystalline film act as traps, impeding charge movement and reducing overall mobility.<sup>[5]</sup> <sup>[6]</sup> The interface with the substrate or dielectric can induce further disorder.<sup>[7]</sup>

The choice of device architecture directly impacts these factors, thereby determining the final measured mobility.

## Key Device Architectures: A Structural Comparison

OFETs are the most common structures for evaluating the charge mobility of organic semiconductors. They operate by using a gate voltage to modulate the charge carrier concentration in a channel between a source and a drain electrode, thus switching the transistor "on" or "off".<sup>[8]</sup> There are four primary OFET configurations, distinguished by the relative placement of the gate, semiconductor, and source/drain contacts.

## Bottom-Gate, Bottom-Contact (BGBC) Architecture

In the BGBC structure, the gate electrode and dielectric layer are prepared first on a substrate. The source and drain electrodes are then patterned on top of the dielectric, and the SiPc semiconductor layer is deposited last, covering the electrodes and the channel region.

Caption: Bottom-Gate, Bottom-Contact (BGBC) OFET structure.

## Bottom-Gate, Top-Contact (BGTC) Architecture

The BGTC configuration also starts with a bottom gate and dielectric. However, the SiPc semiconductor layer is deposited directly onto the dielectric, followed by the thermal evaporation of the source and drain electrodes on top of the semiconductor.

Caption: Bottom-Gate, Top-Contact (BGTC) OFET structure.

## Top-Gate, Bottom-Contact (TGBC) Architecture

For the TGBC architecture, the source and drain electrodes are patterned first on the substrate, followed by the deposition of the SiPc semiconductor. The device is completed by depositing the dielectric layer and then the gate electrode on top.

Caption: Top-Gate, Bottom-Contact (TGBC) OFET structure.

## Top-Gate, Top-Contact (TGTC) Architecture

In the TGTC structure, the SiPc semiconductor is deposited on the substrate first. The source and drain electrodes are then patterned on the SiPc layer. Finally, the device is capped with the gate dielectric and the top gate electrode.

Caption: Top-Gate, Top-Contact (TGTC) OFET structure.

## Comparative Analysis: How Architecture Impacts SiPc Electron Mobility

The choice of architecture creates a cascade of effects that influence the final measured electron mobility. The primary differentiators are the quality of the semiconductor-dielectric interface and the magnitude of the contact resistance at the source/drain electrodes.

## The Critical Role of the Semiconductor-Dielectric Interface

The accumulation of charge carriers occurs in a very thin layer (a few nanometers) of the semiconductor at the interface with the gate dielectric.<sup>[9]</sup> Therefore, the electronic quality of this interface is paramount.

- Bottom-Gate Architectures (BGBC & BGTC): In these configurations, the SiPc film is deposited onto the dielectric. This makes the interface susceptible to contamination and surface roughness of the pre-fabricated dielectric. However, it allows for the dielectric surface to be treated with self-assembled monolayers (SAMs) like HMDS or OTS prior to SiPc deposition.<sup>[6]</sup> Such treatments can reduce surface trap states and promote more ordered molecular growth, significantly boosting mobility.<sup>[10]</sup>

- Top-Gate Architectures (TGBC & TGTC): Here, the dielectric is deposited on top of the SiPc film. This can protect the sensitive semiconductor from atmospheric contaminants during operation. A key advantage is that the charge transport occurs at the interface buried away from the initial substrate, which can be beneficial. However, the deposition process of the dielectric (e.g., sputtering or evaporation) can potentially damage the underlying organic film, creating defects and degrading performance.<sup>[11]</sup>

## The Contact Resistance Bottleneck

Efficient injection of electrons from the source electrode into the SiPc semiconductor is crucial for high performance. High contact resistance ( $R_c$ ) can lead to a significant underestimation of the intrinsic material mobility.<sup>[12]</sup>

- Bottom-Contact Architectures (BGBC & TGBC): The SiPc film is deposited onto pre-patterned electrodes. This can lead to disordered film growth over the electrode edges, creating a morphology that is not conducive to efficient charge injection. This often results in higher contact resistance.<sup>[13]</sup>

- Top-Contact Architectures (BGTC & TGTC): Electrodes are evaporated onto the SiPc film. This typically forms a cleaner, more intimate interface, as the metal atoms can penetrate slightly into the organic layer, leading to better electrical contact and lower  $R_c$ .<sup>[14]</sup> For this

reason, top-contact devices often exhibit higher performance than their bottom-contact counterparts.[14]

## Quantitative Data Summary

The following table summarizes representative electron mobility values for phthalocyanine-based n-type transistors in different architectures. Note that direct comparisons are challenging as mobility is highly dependent on specific processing conditions (e.g., substrate temperature, deposition rate, dielectric material), which vary between studies.

| Device Architecture | Typical Electron Mobility (cm <sup>2</sup> /Vs) | Key Advantages                                                                              | Key Disadvantages                                                                      |

|---------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| BGBC                | 10 <sup>-4</sup> - 10 <sup>-3</sup>             | Simple fabrication; compatible with standard photolithography for electrodes.               | High contact resistance; potentially disordered film growth over electrodes.[13]       |

| BGTC                | 10 <sup>-3</sup> - 10 <sup>-2</sup>             | Lower contact resistance than BGBC; allows for dielectric surface treatment.[14]            | Susceptible to atmospheric degradation; deposition of top contacts can be complex.     |

| TGBC                | 10 <sup>-4</sup> - 10 <sup>-3</sup>             | Semiconductor is protected by the top dielectric layer.                                     | High contact resistance; potential for process-induced damage to the semiconductor.    |

| TGTC                | 10 <sup>-2</sup> - 10 <sup>-1</sup>             | Often yields the highest performance; lower contact resistance and a protected channel.[11] | Fabrication can be complex; potential for solvent/process damage to the semiconductor. |

Note: These are representative ranges for n-type phthalocyanines. Specific values for SiPc will depend heavily on the axial substituents and processing conditions.

## Experimental Protocols

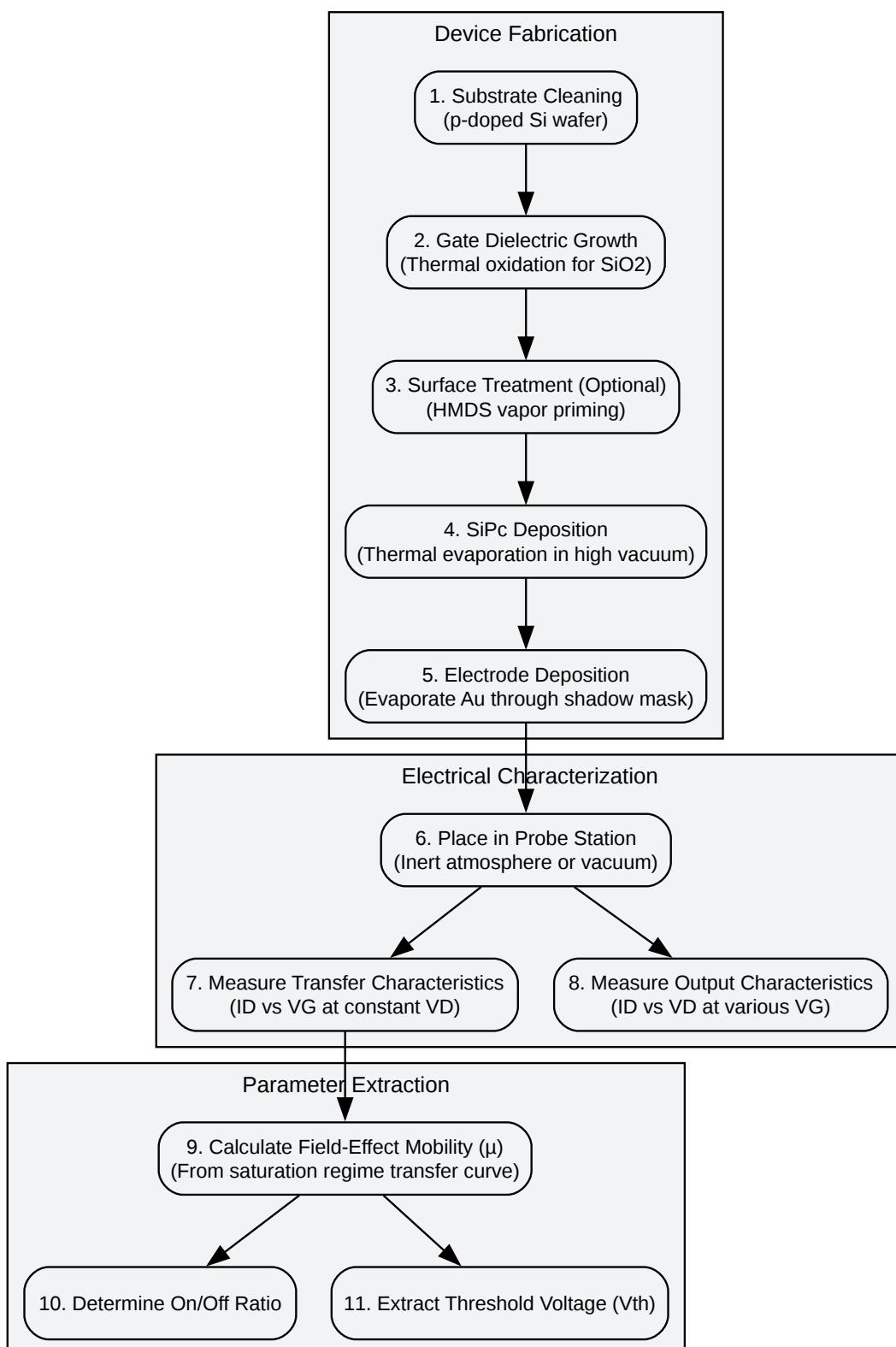

To ensure reproducibility and provide a self-validating framework, we outline a standard methodology for the fabrication and characterization of a SiPc-based OFET. We will use the BGTC architecture as a representative example due to its balance of performance and fabrication accessibility.

## Workflow: Fabrication and Characterization of a BGTC SiPc OFET

[Click to download full resolution via product page](#)

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Silicon phthalocyanines: synthesis and resurgent applications - Organic & Biomolecular Chemistry (RSC Publishing) DOI:10.1039/D0OB02299C [pubs.rsc.org]

- 2. Charge transport of silicon(iv) and zinc(ii) phthalocyanines by molecular junction models - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 3. Electron mobility - Wikipedia [en.wikipedia.org]

- 4. youtube.com [youtube.com]

- 5. pubs.rsc.org [pubs.rsc.org]

- 6. researchgate.net [researchgate.net]

- 7. mediatum.ub.tum.de [mediatum.ub.tum.de]

- 8. youtube.com [youtube.com]

- 9. DSpace [dr.lib.iastate.edu]

- 10. Performance Optimization Strategies for Polymer Organic Field-Effect Transistors as Sensing Platforms - PubMed [pubmed.ncbi.nlm.nih.gov]

- 11. scispace.com [scispace.com]

- 12. poplab.stanford.edu [poplab.stanford.edu]

- 13. researchgate.net [researchgate.net]

- 14. rogersgroup.northwestern.edu [rogersgroup.northwestern.edu]

- To cite this document: BenchChem. [comparative analysis of SiPc electron mobility in different device architectures]. BenchChem, [2026]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1681755#comparative-analysis-of-sipc-electron-mobility-in-different-device-architectures>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)