# benchmarking the performance of 2-tert-butylthiophene transistors against industry standards

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## Compound of Interest

Compound Name: *2-tert-Butylthiophene*

Cat. No.: *B1664577*

[Get Quote](#)

An In-Depth Performance Benchmark of Alkyl-Substituted Thiophene Transistors Against Industry Standards

## A Senior Application Scientist's Guide to Material Selection and Performance Verification

The pursuit of next-generation flexible, transparent, and low-cost electronics has placed a significant focus on organic semiconductor materials. Within this class, thiophene derivatives have emerged as a cornerstone due to their robust electronic properties and environmental stability. While simple molecules like **2-tert-butylthiophene** represent the basic structural motif, the field has rapidly evolved towards more complex, functionalized structures to achieve performance metrics comparable to incumbent technologies like amorphous silicon.

This guide provides a comprehensive performance benchmark of advanced alkyl-substituted thiophene semiconductors against established industry standards. We will move beyond a simple datasheet comparison to explore the causal relationships between molecular structure, thin-film morphology, and transistor performance. The protocols and insights provided herein are designed to be a self-validating framework for researchers and engineers working on the frontier of organic electronics.

# Performance Benchmarking: Thiophene Derivatives vs. Industry Standards

The efficacy of an Organic Thin-Film Transistor (OTFT) is primarily defined by three key performance metrics:

- Charge Carrier Mobility ( $\mu$ ): A measure of how quickly charge carriers (holes in p-type semiconductors) move through the material under an electric field. Higher mobility enables faster switching speeds and higher current output.

- On/Off Current Ratio ( $I_{on}/I_{off}$ ): The ratio of the current when the transistor is in its "on" state to the current when it is in its "off" state. A high ratio is crucial for low power consumption and clear signal discrimination in digital logic.

- Threshold Voltage ( $V_{th}$ ): The minimum gate voltage required to turn the transistor "on" and form a conductive channel. A low absolute threshold voltage is desirable for low-power operation.

Below is a comparative summary of a high-performing, complex thiophene derivative against two industry-standard p-type organic semiconductors: Pentacene and Poly(3-hexylthiophene) (P3HT).

| Parameter                         | High-Performance<br>Thiophene<br>Derivative (e.g., C8-<br>BTBT) | Pentacene (Vacuum<br>Deposited)                                                       | Regioregular P3HT<br>(Solution Processed)                                               |

|-----------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Hole Mobility ( $\mu$ )           | $>10 \text{ cm}^2/\text{Vs}$ <a href="#">[1]</a>                | $\sim 0.3 - 2.6 \text{ cm}^2/\text{Vs}$ <a href="#">[2]</a> <a href="#">[3]</a>       | $\sim 0.01 - 0.1 \text{ cm}^2/\text{Vs}$ <a href="#">[4]</a><br><a href="#">[5]</a>     |

| On/Off Ratio (Ion/Ioff)           | $> 10^7$                                                        | $> 10^6$ <a href="#">[3]</a>                                                          | $\sim 10^3 - 10^5$ <a href="#">[6]</a>                                                  |

| Threshold Voltage<br>( $V_{th}$ ) | $\sim -1.5 \text{ V}$ <a href="#">[2]</a>                       | $\sim -4 \text{ V} \text{ to } -15 \text{ V}$ <a href="#">[2]</a> <a href="#">[3]</a> | $\sim 20 \text{ V}$ (can be highly<br>variable) <a href="#">[5]</a> <a href="#">[6]</a> |

| Deposition Method                 | Solution or Vacuum                                              | Vacuum Thermal<br>Evaporation                                                         | Solution (Spin-<br>coating, Printing)                                                   |

| Air Stability                     | Good to Excellent <a href="#">[7]</a>                           | Moderate to Poor                                                                      | Good                                                                                    |

**Expert Insights:** The data clearly illustrates the performance evolution within the thiophene family. While simple thiophenes are not typically used as active semiconductors, extending the  $\pi$ -conjugated core (as in Benzothieno-benzothiophene, BTBT) and optimizing the alkyl side-chains (like octyl, C8) dramatically enhances molecular ordering and, consequently, charge mobility.[\[1\]](#) This allows solution-processed BTBT derivatives to outperform even vacuum-deposited pentacene, which has long been the gold standard for high-mobility p-type organic semiconductors. P3HT, a polymeric thiophene, offers excellent processability but its charge transport is limited by the disorder between polymer chains, resulting in lower mobility.[\[4\]](#)[\[5\]](#)

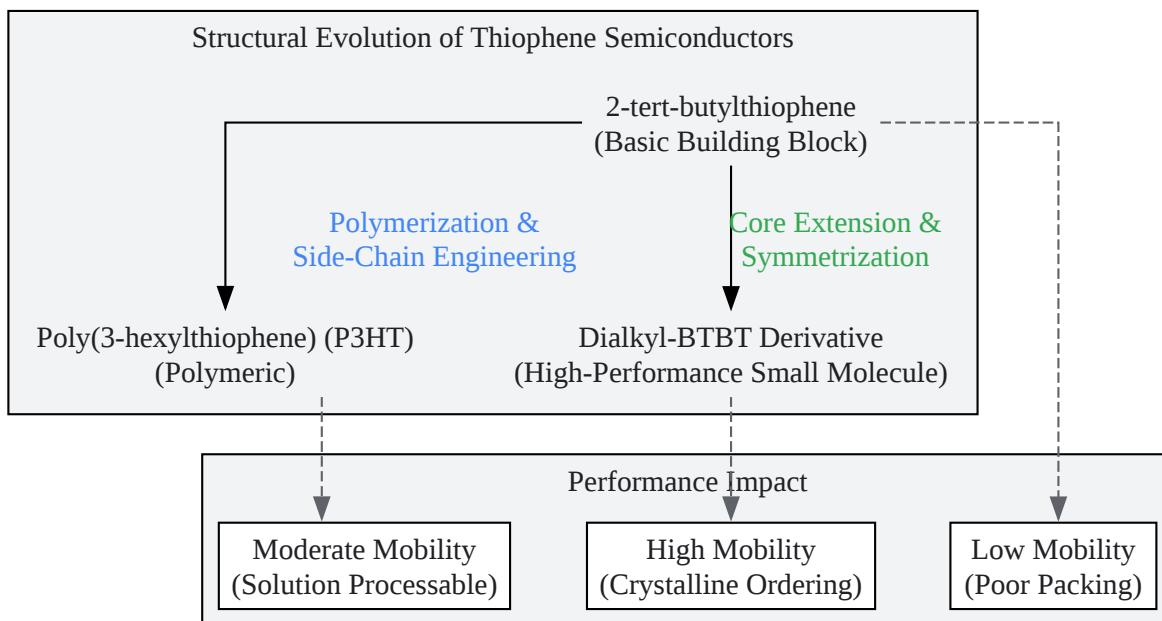

## The Role of Molecular Structure: From Building Block to High-Performance Semiconductor

The performance leap seen in advanced thiophene derivatives is not accidental; it is a direct result of rational molecular design. The **2-tert-butylthiophene** is a simple solubilizing group, but more sophisticated engineering is required for high-performance devices.

[Click to download full resolution via product page](#)

Caption: Evolution of thiophene semiconductors from a basic unit to complex structures.

- Core Extension: Fusing thiophene rings to create larger, more rigid planar cores like BTBT enhances  $\pi$ -orbital overlap between adjacent molecules, which is the primary pathway for charge transport.

- Alkyl Side-Chains: Long alkyl chains (e.g., hexyl in P3HT, octyl in C8-BTBT) serve two critical functions. They improve solubility for solution-based processing and critically mediate the intermolecular packing (self-assembly) in the solid state to ensure favorable  $\pi$ -stacking for efficient charge transport.<sup>[8]</sup>

## Experimental Protocols: A Validated Workflow for OTFT Fabrication and Characterization

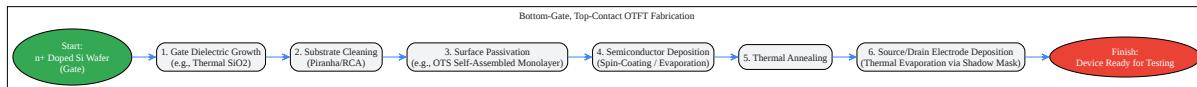

Reproducibility is paramount in semiconductor research. The following protocols describe a standard bottom-gate, top-contact (BGTC) device architecture, which is widely used for

characterizing new materials.

## OTFT Fabrication Workflow

[Click to download full resolution via product page](#)

Caption: Standard fabrication workflow for a bottom-gate, top-contact OTFT.

### Step-by-Step Methodology:

- **Substrate and Gate Formation:** Begin with a heavily n-doped silicon wafer, which serves as both the substrate and the common gate electrode. Grow a high-quality gate dielectric layer, typically 100-300 nm of silicon dioxide ( $\text{SiO}_2$ ), via thermal oxidation.

- **Substrate Cleaning & Surface Treatment (Trustworthiness Pillar):** This step is critical for device performance and reproducibility.

- **Causality:** The interface between the dielectric and the organic semiconductor is where charge transport occurs. An atomically clean, defect-free surface is essential to prevent charge trapping.

- **Protocol:**

1. Clean the  $\text{Si}/\text{SiO}_2$  substrate ultrasonically in acetone, then isopropyl alcohol (IPA), each for 15 minutes.

2. Rinse thoroughly with deionized (DI) water and dry under a stream of  $\text{N}_2$ .

3. Treat with UV-Ozone for 10 minutes to remove organic residues and create a hydrophilic surface.

4. Immediately immerse the substrate in a 10 mM solution of octadecyltrichlorosilane (OTS) in anhydrous toluene for 30 minutes to form a hydrophobic self-assembled monolayer (SAM). This SAM improves the molecular ordering of the subsequently deposited organic layer.<sup>[8]</sup>

5. Rinse with fresh toluene and IPA to remove excess OTS, then dry with N<sub>2</sub>.

- Active Layer Deposition:

- For Solution-Processable Materials (e.g., P3HT, BTBT derivatives):

1. Prepare a solution of the organic semiconductor (e.g., 5 mg/mL in chloroform).

2. Spin-coat the solution onto the OTS-treated substrate at 2000 rpm for 60 seconds.

- For Vacuum-Deposited Materials (e.g., Pentacene):

1. Place the substrate in a high-vacuum thermal evaporator (<10<sup>-6</sup> Torr).

2. Deposit a 30-50 nm thick film of pentacene at a rate of 0.1-0.2 Å/s.

- Thermal Annealing: Anneal the substrate at a temperature just below the material's melting or glass transition point (e.g., 120 °C for P3HT) for 30 minutes in a nitrogen-filled glovebox. This improves the crystallinity and molecular ordering of the film.

- Source-Drain Electrode Deposition: Using a shadow mask to define the channel, thermally evaporate 50 nm of Gold (Au) to form the source and drain contacts. The channel length (L) and width (W) are defined by the mask, typically L = 50 μm and W = 1000 μm.

## Electrical Characterization Protocol

Characterization should be performed in an inert environment (N<sub>2</sub> or vacuum) using a semiconductor parameter analyzer connected to a probe station.<sup>[9]</sup>

- Gate Leakage Test:

- Purpose: To ensure the integrity of the gate dielectric.

- Procedure: With the source and drain contacts floating, sweep the gate voltage (VGS) from 0 V to the maximum intended operating voltage (e.g., -60 V) and measure the gate current (IG). IG should be at least two orders of magnitude lower than the expected Ioff of the transistor.

- Output Characteristics (IDS vs. VDS):

- Purpose: To observe the linear and saturation regimes of transistor operation.

- Procedure:

1. Set VGS to a constant value (e.g., 0 V, -10 V, -20 V, -30 V, -40 V).

2. For each VGS, sweep the drain-source voltage (VDS) from 0 V to -60 V and measure the drain-source current (IDS).

- Transfer Characteristics (IDS vs. VGS):

- Purpose: To extract the key performance metrics (mobility, on/off ratio, threshold voltage).

- Procedure:

1. Set VDS to a constant value in the saturation regime (e.g., -60 V).

2. Sweep VGS from a positive voltage (e.g., +20 V) to a negative voltage (e.g., -60 V) and measure IDS. Plot IDS on a logarithmic scale and  $|IDS|^{1/2}$  on a linear scale.

#### Data Extraction:

- On/Off Ratio: The ratio of the maximum IDS to the minimum IDS from the logarithmic transfer curve.

- Threshold Voltage (Vth): Extrapolate the linear portion of the  $|IDS|^{1/2}$  vs. VGS plot to the x-axis (where  $|IDS|^{1/2} = 0$ ). The x-intercept is Vth.

- Field-Effect Mobility ( $\mu$ ): Calculated from the slope of the linear portion of the  $|IDS|^{1/2}$  vs. VGS plot using the saturation region equation:

$$IDS = (\mu * Ci * W) / (2L) * (VGS - Vth)^2$$

where  $Ci$  is the capacitance per unit area of the gate dielectric, and  $W$  and  $L$  are the channel width and length, respectively.

## Conclusion and Outlook

The performance of thiophene-based organic transistors is a direct function of sophisticated molecular engineering. By moving from simple substituted thiophenes to complex, extended, and symmetrically functionalized  $\pi$ -cores, researchers have developed materials that rival and even exceed the performance of traditional organic electronic standards. The remarkable mobility of materials like C8-BTBT, coupled with their solution processability, opens the door for high-speed, low-cost flexible circuits, sensors, and displays. The provided protocols offer a standardized framework for fabricating and reliably characterizing these next-generation devices, ensuring that comparative data is both accurate and meaningful for advancing the field.

### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Ultrahigh mobility and efficient charge injection in monolayer organic thin-film transistors on boron nitride - PMC [pmc.ncbi.nlm.nih.gov]

- 2. [pubs.aip.org](https://pubs.aip.org) [pubs.aip.org]

- 3. [pubs.aip.org](https://pubs.aip.org) [pubs.aip.org]

- 4. [pubs.aip.org](https://pubs.aip.org) [pubs.aip.org]

- 5. Poly(3-hexylthiophene)-Based Organic Thin-Film Transistors with Virgin Graphene Oxide as an Interfacial Layer [mdpi.com]

- 6. [pdfs.semanticscholar.org](https://pdfs.semanticscholar.org) [pdfs.semanticscholar.org]

- 7. web.pkusz.edu.cn [web.pkusz.edu.cn]

- 8. Self-Assembly in Organic Thin Film Transistors for Flexible Electronic Devices [sigmaaldrich.com]

- 9. sunfest.seas.upenn.edu [sunfest.seas.upenn.edu]

- To cite this document: BenchChem. [benchmarking the performance of 2-tert-butylthiophene transistors against industry standards]. BenchChem, [2026]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1664577#benchmarking-the-performance-of-2-tert-butylthiophene-transistors-against-industry-standards]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)