# Technical Support Center: Minimizing Contact Resistance in Benzo[a]pentacene Transistors

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Benzo[a]pentacene

Cat. No.: B1618297

[Get Quote](#)

Disclaimer: Scientific literature directly addressing contact resistance in **Benzo[a]pentacene** transistors is limited. The following troubleshooting guides and frequently asked questions (FAQs) are based on extensive research into pentacene, a closely related and well-studied organic semiconductor. The principles and techniques described are expected to be highly applicable to **Benzo[a]pentacene**-based devices.

## Frequently Asked Questions (FAQs)

**Q1:** What is contact resistance and why is it a critical issue in **Benzo[a]pentacene** transistors?

Contact resistance ( $R_c$ ) is the parasitic resistance at the interface between the source/drain electrodes and the organic semiconductor layer. It impedes the efficient injection of charge carriers from the electrodes into the transistor channel.<sup>[1]</sup> High contact resistance can lead to a significant voltage drop at the contacts, resulting in underestimation of the intrinsic charge carrier mobility, large threshold voltage shifts, and overall poor device performance.<sup>[2]</sup> In organic thin-film transistors (OTFTs), this issue is particularly critical as it can dominate the total device resistance, especially in short-channel devices.

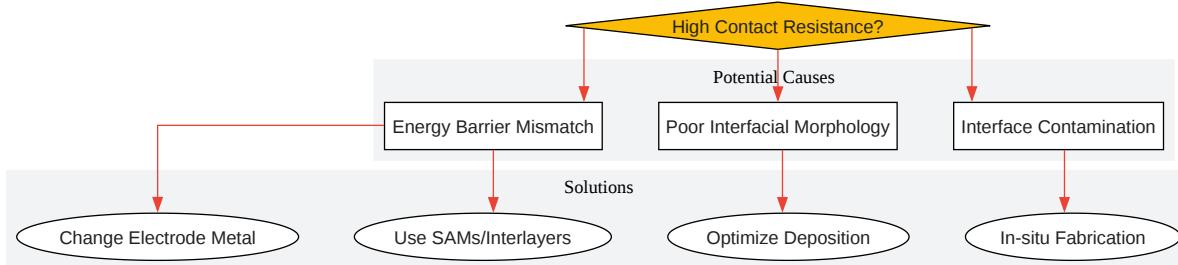

**Q2:** What are the primary causes of high contact resistance in organic transistors?

High contact resistance in organic transistors like those based on **Benzo[a]pentacene** stems from several factors:

- Energy Barrier: A significant energy barrier for charge injection often exists due to a mismatch between the work function of the electrode metal and the highest occupied molecular orbital (HOMO) of the p-type organic semiconductor.

- Poor Interfacial Morphology: Roughness at the electrode surface or poor ordering of the organic semiconductor molecules at the interface can lead to inefficient charge injection.[3]

- Interfacial Traps: Chemical impurities or structural defects at the metal-organic interface can trap charge carriers, increasing the resistance.

- Device Architecture: The geometry of the device, such as top-contact vs. bottom-contact, can influence the contact resistance.[4]

Q3: What are the common methods to measure contact resistance in our lab?

Several methods are commonly used to extract contact resistance values:

- Transmission Line Method (TLM): This is a widely used technique that requires fabricating a series of transistors with identical widths but varying channel lengths. The total resistance is plotted against the channel length, and the contact resistance is determined from the y-intercept.[3]

- Gated Four-Probe Method: This method involves placing additional voltage-sensing probes within the channel to directly measure the potential drop at the contacts.[4]

- Y-Function Method: This is a single-transistor method that can be used to extract contact resistance from the device's transfer characteristics.

## Troubleshooting Guides

### Issue 1: High Contact Resistance Observed in Top-Contact Benzo[a]pentacene Transistors

Symptoms:

- Non-linear output characteristics at low drain-source voltages.

- Calculated field-effect mobility is significantly lower than expected.

- Large and unstable threshold voltage.

#### Possible Causes & Solutions:

| Possible Cause              | Troubleshooting Steps & Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy Barrier Mismatch     | <p>1. Electrode Material Selection: Use high work function metals like Gold (Au) or Platinum (Pt) for p-type semiconductors like Benzo[a]pentacene to reduce the hole injection barrier.</p> <p>2. Self-Assembled Monolayers (SAMs): Treat the electrode surface with a SAM to modify its work function and improve the interface with the organic semiconductor. For Au electrodes, thiol-based SAMs can be effective.</p> <p>3. Interlayer Deposition: Introduce a thin charge injection layer, such as Molybdenum Oxide (<math>\text{MoO}_3</math>), between the electrode and the organic semiconductor to facilitate charge injection.</p> |

| Poor Interfacial Morphology | <p>1. Optimized Deposition Rate: During thermal evaporation of the top electrodes, use a slow deposition rate to minimize damage to the underlying organic layer and promote better contact.</p> <p>2. Substrate Temperature Control: Optimize the substrate temperature during the deposition of the Benzo[a]pentacene layer to improve its crystallinity and ordering at the interface.</p>                                                                                                                                                                                                                                                   |

| Contaminated Interface      | <p>1. In-situ Fabrication: Whenever possible, deposit the organic semiconductor and the top electrodes in the same vacuum chamber without breaking vacuum to prevent atmospheric contamination.</p> <p>2. Glovebox Environment: If in-situ fabrication is not possible, perform the device fabrication in an inert glovebox environment to minimize exposure to moisture and oxygen, which can create trap states.</p>                                                                                                                                                                                                                          |

## Issue 2: Inconsistent Contact Resistance Across Different Batches of Bottom-Contact Devices

Symptoms:

- Large variability in device performance from one fabrication run to another.

- Poor reproducibility of contact resistance measurements.

Possible Causes & Solutions:

| Possible Cause                    | Troubleshooting Steps & Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inconsistent Surface Treatment    | <p>1. Standardize Substrate Cleaning: Implement a rigorous and consistent substrate and electrode cleaning protocol before depositing the organic semiconductor. This may include ultrasonication in a series of solvents followed by UV-ozone or plasma treatment.</p> <p>2. Reproducible SAM Deposition: If using SAMs, ensure precise control over the immersion time, solution concentration, and rinsing process to achieve a uniform monolayer.</p>                                              |

| Variations in Organic Film Growth | <p>1. Monitor Deposition Conditions: Closely monitor and control the deposition rate and substrate temperature during the growth of the Benzo[a]pentacene film, as these parameters significantly influence the film morphology and grain size.</p> <p>2. Surface Energy of the Dielectric: The surface energy of the gate dielectric can affect the growth of the organic semiconductor. Consider treating the dielectric surface to promote a more ordered growth of the Benzo[a]pentacene film.</p> |

| Electrode Contamination           | <p>1. Pre-deposition Cleaning: Ensure that the pre-patterned source/drain electrodes are thoroughly cleaned immediately before loading into the deposition chamber to remove any organic residues or oxides that may have formed.</p>                                                                                                                                                                                                                                                                  |

## Quantitative Data Summary

Table 1: Effect of Doped Interlayer on Contact Resistance in Pentacene Transistors

| Interlayer (F <sub>4</sub> TCNQ:pentacene ratio) | Contact Resistance (kΩ·cm) at V <sub>g</sub> = -30V |

|--------------------------------------------------|-----------------------------------------------------|

| No Interlayer                                    | ~1250                                               |

| 1:10                                             | ~750                                                |

| 1:3                                              | ~500                                                |

| 1:1                                              | ~250                                                |

Data adapted from studies on pentacene, which is expected to show similar trends for **Benzo[a]pentacene**.<sup>[3]</sup>

Table 2: Impact of Dielectric Layer on Contact Resistance in Pentacene Transistors

| Dielectric Material          | Contact Resistance (kΩ) at V <sub>g</sub> = -100V |

|------------------------------|---------------------------------------------------|

| Poly(4-hydroxystyrene) (PHS) | ~12                                               |

| Glassy Rubber (GR)           | ~120                                              |

Data suggests that the choice of dielectric can significantly influence contact resistance.<sup>[1]</sup>

## Experimental Protocols

### Protocol 1: Fabrication of a Top-Contact Benzo[a]pentacene Transistor with a Doped Interlayer

This protocol describes the fabrication of a top-contact, bottom-gate **Benzo[a]pentacene** transistor with an F<sub>4</sub>TCNQ-doped pentacene interlayer to reduce contact resistance.

#### 1. Substrate Preparation:

- Start with a heavily n-doped Si wafer with a 300 nm thermally grown SiO<sub>2</sub> layer, which will serve as the gate electrode and gate dielectric, respectively.

- Clean the substrate by ultrasonication in acetone, and isopropanol for 15 minutes each, followed by drying with a nitrogen gun.

- Treat the SiO<sub>2</sub> surface with an oxygen plasma or UV-ozone for 5-10 minutes to improve the surface energy for pentacene growth.

## 2. Benzo[a]pentacene Deposition:

- Transfer the cleaned substrate to a high-vacuum thermal evaporator.

- Deposit a 50 nm thick film of **Benzo[a]pentacene** at a rate of 0.1-0.2 Å/s. Maintain the substrate at a constant temperature (e.g., 60 °C) during deposition to promote ordered film growth.

### 3. Doped Interlayer Deposition:

- Without breaking vacuum, co-evaporate  $F_4TCNQ$  and pentacene to form a thin (e.g., 5-10 nm) doped interlayer.

- Control the deposition rates of the two materials to achieve the desired doping ratio (e.g., 1:1). For example, maintain the  $F_4TCNQ$  rate at  $0.1 \text{ \AA/s}$  and the pentacene rate at  $0.1 \text{ \AA/s}$ .[3]

#### 4. Electrode Deposition:

- Through a shadow mask, deposit 50 nm of Gold (Au) for the source and drain electrodes at a rate of 0.5-1 Å/s. The channel length and width are defined by the shadow mask dimensions.

## 5. Device Characterization:

- Transfer the fabricated device to a probe station for electrical characterization.

- Measure the output and transfer characteristics to determine device parameters such as mobility, threshold voltage, and on/off ratio.

- Use the Transmission Line Method (TLM) by fabricating devices with varying channel lengths to extract the contact resistance.

## Diagrams

Click to download full resolution via product page

Caption: Experimental workflow for fabricating a top-contact **Benzo[a]pentacene** transistor.

[Click to download full resolution via product page](#)

Caption: Troubleshooting logic for high contact resistance in **Benzo[a]pentacene** transistors.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. rogersgroup.northwestern.edu [rogersgroup.northwestern.edu]

- 2. mdpi.com [mdpi.com]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Minimizing Contact Resistance in Benzo[a]pentacene Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1618297#minimizing-contact-resistance-in-benzo-a-pentacene-transistors]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)