# Enhancing charge injection and transport in Benzo[a]pentacene devices

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Benzo[a]pentacene

Cat. No.: B1618297

[Get Quote](#)

## Technical Support Center: Benzo[a]pentacene Devices

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **Benzo[a]pentacene**-based organic field-effect transistors (OFETs). Our goal is to help you enhance charge injection and transport in your devices.

## Frequently Asked Questions (FAQs) & Troubleshooting

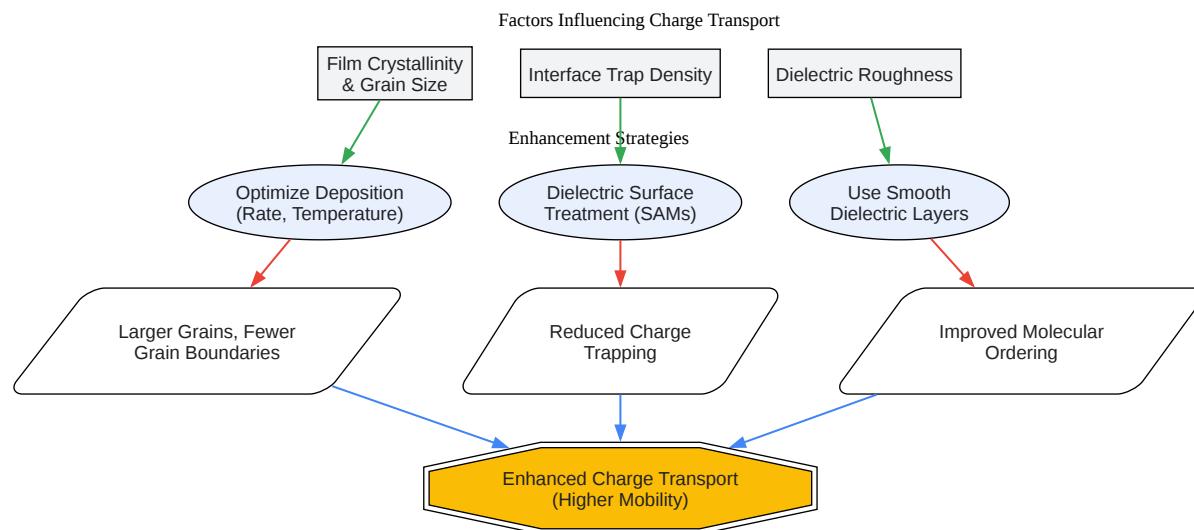

### Issue 1: Low Carrier Mobility

Q: My **Benzo[a]pentacene** OFET is exhibiting low field-effect mobility. What are the potential causes and how can I improve it?

A: Low carrier mobility in pentacene-based OFETs is a common issue that can stem from several factors related to the active layer morphology, the dielectric interface, and charge trapping.

- Poor Crystalline Quality of the Pentacene Film: The degree of molecular ordering and the size of the crystalline grains in the pentacene film are critical for efficient charge transport.

Small grains and a high density of grain boundaries can act as scattering sites for charge carriers, thereby reducing mobility.[1][2]

- Troubleshooting:

- Optimize Deposition Rate: A slower deposition rate is often optimal for forming larger, more well-ordered crystals.[3] Co-evaporation with a material like p-terphenyl can also be used to dilute pentacene and improve crystal growth.[3]

- Control Substrate Temperature: Increasing the substrate temperature during deposition can enhance the crystallinity of the pentacene film and lead to larger grain sizes.[4] However, an excessively high temperature can lead to desorption.[4] The optimal temperature needs to be determined empirically for your specific setup.

- High Density of Trap States: Trap states, which can be present at the semiconductor-dielectric interface or within the bulk of the pentacene film, can immobilize charge carriers and reduce mobility.

- Troubleshooting:

- Dielectric Surface Treatment: The use of self-assembled monolayers (SAMs) like octadecyltrichlorosilane (OTS) on the dielectric surface can reduce trap states and improve molecular ordering of the pentacene film.[5]

- High-Purity Materials: Ensure the purity of the pentacene source material, as impurities can introduce trap states.

- Dielectric Roughness: A rough dielectric surface can disrupt the growth of the pentacene film, leading to smaller grains and increased charge scattering.[1] A gradual decrease in mobility has been observed with increasing dielectric roughness.[1]

- Troubleshooting:

- Use Smoother Dielectric Layers: Employ techniques to produce smoother dielectric surfaces. Sputtering SiO<sub>2</sub> on a smooth underlying metal is one approach to achieve a smoother dielectric surface.[1]

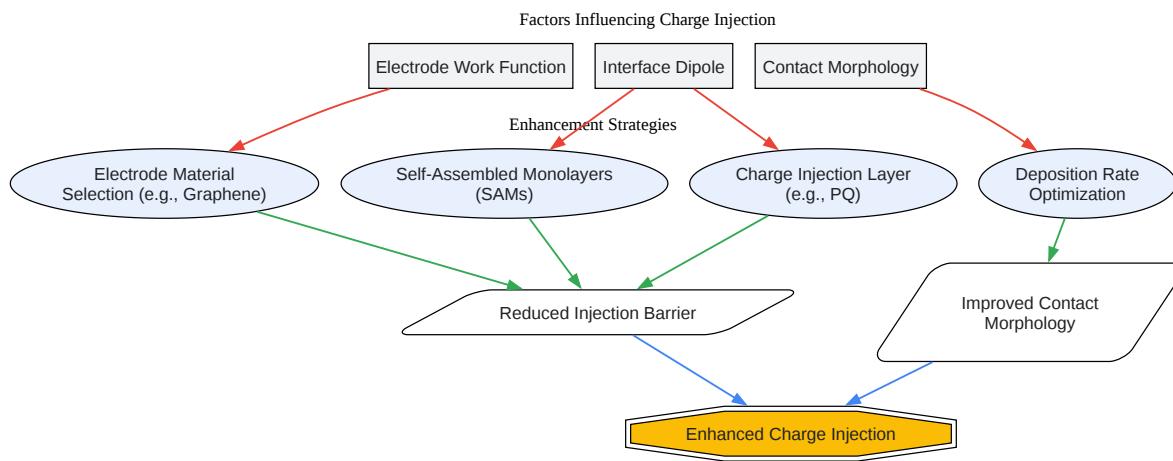

## Issue 2: High Contact Resistance

Q: I am observing a high contact resistance between the source/drain electrodes and the pentacene layer. What are the contributing factors and how can I reduce it?

A: High contact resistance is a significant barrier to efficient charge injection and can dominate the overall device resistance, leading to poor performance.

- Energy Barrier at the Electrode-Organic Interface: A large mismatch between the work function of the electrode material and the highest occupied molecular orbital (HOMO) of pentacene can create a significant energy barrier for hole injection.

- Troubleshooting:

- Electrode Material Selection: Using electrodes with a high work function, such as gold (Au), is common for p-type semiconductors like pentacene. Graphene electrodes have also been shown to exhibit lower contact resistance and a smaller charge-injection barrier compared to Au due to favorable dipole layer formation at the interface.[6]

- Interface Engineering: Inserting a charge injection layer between the electrode and the pentacene can reduce the injection barrier.[7] For instance, a thin layer of 6,13-pentacenequinone (PQ) has been shown to significantly improve performance by reducing the hole barrier height.[8] Self-assembled monolayer (SAM) treatment on the metal electrodes can also tune the work function and improve charge injection.[7]

- Poor Morphology at the Contact: The morphology of the pentacene film at the edge of the source and drain electrodes can be different from the channel region, leading to increased resistance. A high deposition rate can lead to poor morphology near the electrode edge.[4]

- Troubleshooting:

- Optimize Deposition Conditions: A lower growth rate can induce better crystalline properties of the film in the channel region and at the contacts.[4]

- Device Architecture: The choice between top-contact and bottom-contact architectures can influence the contact resistance. Soft contact lamination has been shown to yield lower parasitic resistances compared to conventional evaporated top contacts.[9]

- Gate Voltage Dependence: Contact resistance in pentacene OFETs is often dependent on the gate bias. The contact resistance tends to decrease with increasing gate voltage.[10]

#### Issue 3: Device Instability and Threshold Voltage Shift

Q: My pentacene OFETs show a significant shift in threshold voltage under prolonged gate bias stress. What causes this instability and how can it be mitigated?

A: Threshold voltage instability, often observed as a shift under continuous gate bias, is a critical issue for the long-term operational stability of OFETs.

- Charge Trapping: The primary cause of threshold voltage shift is charge trapping, which can occur at the semiconductor-dielectric interface or within the dielectric layer itself.

- Troubleshooting:

- Dielectric Material Choice: The choice of dielectric material plays a crucial role in device stability.[11] Pentacene transistors with bare or polystyrene-modified SiO<sub>2</sub> gate dielectrics have shown excellent electrical stabilities, while devices with OTS-treated SiO<sub>2</sub> exhibited worse stability.[11]

- Interface Passivation: A clean and well-passivated dielectric surface is essential. Devices with OTS treatment have shown a suppression of deep-level traps.[5]

- Influence of Grain Boundaries: Grain boundaries in the pentacene film can act as trapping sites, contributing to bias stress effects.[2] Devices with larger initial grain sizes have been found to exhibit smaller threshold voltage shifts.[2]

- Troubleshooting:

- Optimize Film Growth: As mentioned for improving mobility, optimizing deposition conditions to achieve larger grains can also enhance device stability.

## Quantitative Data Summary

The following tables summarize key performance parameters of **Benzo[a]pentacene** OFETs under various experimental conditions.

Table 1: Effect of Dielectric and Surface Treatment on Device Performance

| Dielectric         | Surface Treatment | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio     | Threshold Voltage (V) | Reference |

|--------------------|-------------------|--------------------------------|------------------|-----------------------|-----------|

| SiO <sub>2</sub>   | Bare              | -                              | ~10 <sup>4</sup> | -                     | [9]       |

| SiO <sub>2</sub>   | OTS               | 0.4                            | -                | -                     | [3]       |

| Polycarbonate (PC) | None              | 0.62                           | -                | -                     | [3]       |

| PVA/PVP Bilayer    | None              | -                              | >10 <sup>5</sup> | -                     | [12][13]  |

| PHS                | -                 | 0.31                           | -                | 5.9                   | [10]      |

Table 2: Influence of Electrode Material and Architecture on Contact Resistance

| Electrode Material | Device Architecture | Contact Resistance (Ω)             | Gate Voltage (V) | Reference |

|--------------------|---------------------|------------------------------------|------------------|-----------|

| Au                 | Top-Contact         | 10 <sup>6</sup> - 10 <sup>10</sup> | -15 to -40       |           |

| Graphene           | -                   | Lower than Au                      | -                | [6]       |

| Au (laminated)     | Top-Contact         | Lower than evaporated Au           | -                | [9]       |

Table 3: Impact of Deposition Parameters on TIPS-Pentacene OFET Mobility

| Solvent         | Annealing Temperature (°C) | Mobility (cm <sup>2</sup> /Vs) | Reference            |

|-----------------|----------------------------|--------------------------------|----------------------|

| Toluene         | No-anneal                  | $1.2 \times 10^{-3}$           | <a href="#">[14]</a> |

| Toluene         | 120                        | $1.5 \times 10^{-3}$           | <a href="#">[14]</a> |

| Toluene         | 150                        | $4.5 \times 10^{-3}$           | <a href="#">[14]</a> |

| Chlorobenzene   | 120                        | $7.1 \times 10^{-3}$           | <a href="#">[14]</a> |

| Tetrahydrofuran | 120                        | $1.43 \times 10^{-3}$          | <a href="#">[14]</a> |

## Experimental Protocols

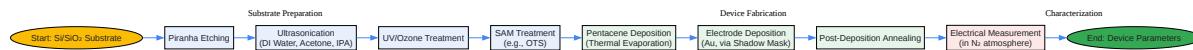

### Protocol 1: Fabrication of a Top-Contact, Bottom-Gate (TCBG) Pentacene OFET

This protocol outlines a general procedure for fabricating a TCBG pentacene OFET on a Si/SiO<sub>2</sub> substrate.

- Substrate Cleaning:

- Begin with a heavily n-doped Si wafer with a thermally grown SiO<sub>2</sub> layer (e.g., 200 nm) which will serve as the gate electrode and gate dielectric, respectively.

- Perform piranha etching (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> = 4:1) at 80°C for 2 hours to remove organic residues.[\[15\]](#)

- Subsequently, sonicate the substrate in deionized water, acetone, and isopropanol (IPA) for 10 minutes each.[\[15\]](#)

- Dry the substrate with a stream of nitrogen.

- Dielectric Surface Treatment (Optional but Recommended):

- Expose the substrate to UV/O<sub>3</sub> treatment for 1 hour to create a hydrophilic surface with -OH groups.[\[15\]](#)

- For an OTS treatment, immerse the substrate in a 0.01 M solution of n-Octyltrichlorosilane (OTS) in toluene for 16 hours in a nitrogen atmosphere.[15]

- After immersion, sonicate the substrate in toluene, acetone, and IPA for 10 minutes each to remove excess OTS.[15]

- Pentacene Deposition:

- Transfer the substrate to a high-vacuum thermal evaporation chamber.

- Deposit a thin film of pentacene (e.g., 60 nm) at a controlled rate (e.g., 0.3 Å/s) and substrate temperature (e.g., 60 °C).[15] The pressure should be maintained around  $10^{-4}$  Pa.[15]

- Source/Drain Electrode Deposition:

- Using a shadow mask to define the channel length and width, deposit the source and drain electrodes.

- Thermally evaporate a layer of gold (Au) (e.g., 40 nm) at a deposition rate of, for example, 0.7 Å/s.[15]

- Post-Deposition Annealing (Optional):

- Anneal the completed device in a nitrogen environment (e.g., at 120°C for 5 minutes) to potentially improve film morphology and device performance.[15]

- Device Characterization:

- Perform electrical measurements in an inert atmosphere (e.g., under N<sub>2</sub>) to extract parameters such as mobility, threshold voltage, and on/off ratio. The field-effect mobility ( $\mu$ ) can be determined from the transfer curves in the saturation regime.[15]

## Visualizations

[Click to download full resolution via product page](#)

Caption: Workflow for TCBG **Benzo[a]pentacene** OFET Fabrication.

[Click to download full resolution via product page](#)

Caption: Strategies to Enhance Charge Injection in OFETs.

[Click to download full resolution via product page](#)

Caption: Strategies to Enhance Charge Transport in OFETs.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [lirias.kuleuven.be](http://lirias.kuleuven.be) [[lirias.kuleuven.be](http://lirias.kuleuven.be)]

- 2. researchgate.net [researchgate.net]

- 3. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance - PMC [pmc.ncbi.nlm.nih.gov]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. pure.korea.ac.kr [pure.korea.ac.kr]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. rogersgroup.northwestern.edu [rogersgroup.northwestern.edu]

- 10. rogersgroup.northwestern.edu [rogersgroup.northwestern.edu]

- 11. Effect of dielectric layers on device stability of pentacene-based field-effect transistors - PubMed [pubmed.ncbi.nlm.nih.gov]

- 12. Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator - PMC [pmc.ncbi.nlm.nih.gov]

- 13. Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator [mdpi.com]

- 14. Optimization of 6,13Bis(triisopropylsilylithynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects [scirp.org]

- 15. Fabrication and Evaluation of Organic Field-Effect Transistors (OFETs) : Dibenzo[a,l]pentacene [D5488] | Tokyo Chemical Industry Co., Ltd.(APAC) [tcichemicals.com]

- To cite this document: BenchChem. [Enhancing charge injection and transport in Benzo[a]pentacene devices]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1618297#enhancing-charge-injection-and-transport-in-benzo-a-pentacene-devices>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)