# Technical Support Center: Troubleshooting Low Hole Mobility in OFETs

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## Compound of Interest

**Compound Name:** 4,7-Bis(5-bromothiophen-2-yl)benzo[c][1,2,5]thiadiazole

**Cat. No.:** B160511

[Get Quote](#)

This technical support center provides researchers, scientists, and drug development professionals with a comprehensive guide to troubleshooting low hole mobility in Organic Field-Effect Transistors (OFETs). The information is presented in a question-and-answer format to directly address common issues encountered during experimentation.

## Frequently Asked Questions (FAQs) & Troubleshooting Guides

### Issue 1: Consistently low or negligible hole mobility in fabricated OFETs.

Question: My OFETs are showing very low or no field-effect mobility. What are the primary factors I should investigate?

Answer: Low hole mobility in OFETs is a common issue that can stem from several factors throughout the fabrication and measurement process. The primary areas to investigate are the quality of the organic semiconductor film, the integrity of the dielectric interface, and the efficiency of charge injection from the source/drain electrodes. Start by systematically evaluating the following potential causes:

- Poor Organic Semiconductor Film Morphology: The arrangement and crystallinity of the organic semiconductor molecules are critical for efficient charge transport. Disordered films

with small grains and numerous grain boundaries will significantly impede hole mobility.[1][2][3]

- High Contact Resistance: A large energy barrier between the source/drain electrodes and the organic semiconductor can hinder the injection of holes into the active layer, leading to an underestimation of the intrinsic mobility.[4][5][6]

- Unfavorable Dielectric Interface: The interface between the gate dielectric and the organic semiconductor is where charge transport occurs. A rough or contaminated dielectric surface can introduce charge traps and scattering sites, reducing mobility.[7][8][9]

- Presence of Impurities and Traps: Contaminants from solvents, the ambient environment, or the substrate can create electronic trap states within the semiconductor or at the interfaces, which immobilize charge carriers.[10][11]

- Suboptimal Deposition Parameters: The method and parameters used to deposit the organic semiconductor (e.g., substrate temperature, deposition rate) strongly influence the film's morphology and, consequently, its charge transport properties.

- Incorrect Measurement Technique: Improper probing or flawed measurement parameters can lead to inaccurate extraction of mobility values.

To diagnose the root cause, a systematic approach involving characterization of the film morphology and electrical properties is essential.

## Issue 2: High degree of variability in hole mobility across different devices on the same substrate.

Question: I'm observing significant variations in hole mobility for OFETs fabricated on the same substrate. What could be causing this inconsistency?

Answer: High device-to-device variation is often linked to non-uniformity in the active layer or at the interfaces. Key factors to consider include:

- Non-uniform Film Thickness and Morphology: Inconsistent thickness or variations in crystallinity across the substrate can lead to different charge transport characteristics in each

device. This is particularly common in solution-based deposition techniques like spin-coating if the solution does not spread evenly.

- Inhomogeneous Dielectric Surface Treatment: If a surface treatment (e.g., with a self-assembled monolayer like OTS) is applied to the dielectric, incomplete or uneven coverage can result in regions with different surface energies, affecting the growth of the organic semiconductor and creating variations in device performance.[8]

- Shadow Masking Issues during Deposition: Misalignment or poor contact of a shadow mask during the deposition of the semiconductor or electrodes can lead to variations in channel dimensions and contact quality.

- Localized Contamination: Particulate contamination on the substrate or in the processing environment can introduce defects in some devices while not affecting others.

To mitigate this, ensure meticulous cleaning of substrates, optimize deposition processes for uniformity, and verify the quality of surface treatments across the entire substrate.

## **Issue 3: Hole mobility improves after post-fabrication treatment, but the initial mobility is still low.**

Question: Annealing my devices improves hole mobility, but the as-fabricated mobility is very poor. How can I improve the initial film quality?

Answer: While post-fabrication annealing is a powerful technique to enhance mobility, a low initial mobility suggests that the "as-deposited" film has a highly disordered morphology. To improve the initial quality of the organic semiconductor film, focus on optimizing the deposition process itself:

- Substrate Temperature Control: The temperature of the substrate during deposition is a critical parameter. For many small-molecule organic semiconductors, depositing on a heated substrate can provide the molecules with sufficient thermal energy to arrange into more ordered, crystalline structures.

- Deposition Rate: The rate at which the organic semiconductor is deposited can influence grain size and film continuity. Slower deposition rates can sometimes lead to larger crystal grains and higher mobility.

- Solvent Selection and Additives (for solution-processed films): In solution-based methods, the choice of solvent and the use of solvent additives can significantly impact film morphology. A solvent that evaporates too quickly may not allow sufficient time for molecular self-assembly.

- Surface Energy of the Dielectric: The surface energy of the dielectric layer influences the growth mode of the organic semiconductor. Modifying the dielectric surface with a self-assembled monolayer (SAM) can promote a more favorable film morphology for charge transport.<sup>[8]</sup>

By optimizing these parameters, you can achieve a higher quality as-deposited film, which can then be further improved with post-fabrication treatments like annealing.

## Troubleshooting Workflows & Signaling Pathways

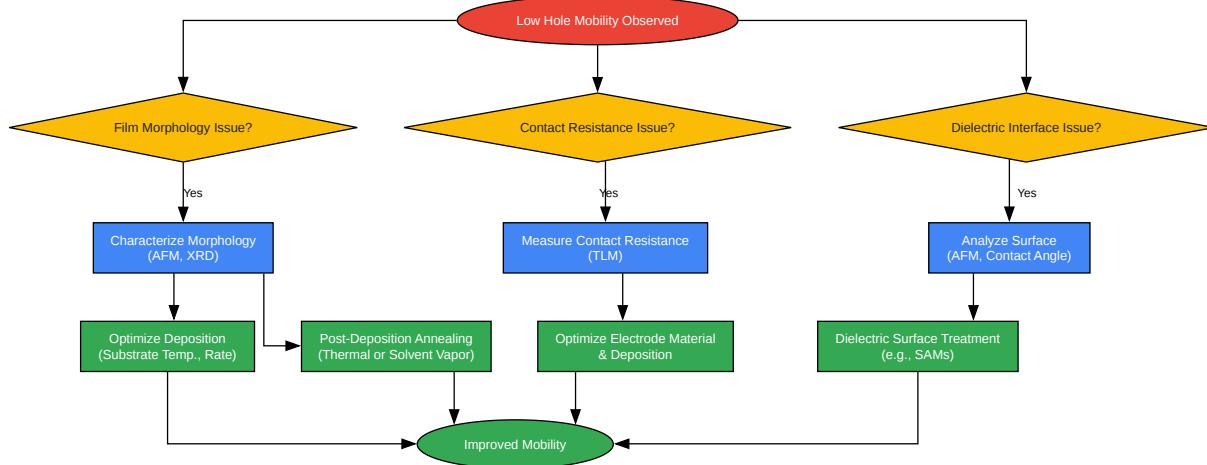

The following diagrams illustrate logical workflows for troubleshooting low hole mobility and the relationships between key experimental parameters and material properties.

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for low hole mobility in OFETs.

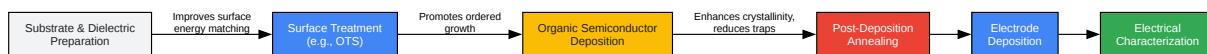

[Click to download full resolution via product page](#)

Caption: Experimental workflow for OFET fabrication with key optimization steps.

## Quantitative Data Summary

The following table summarizes typical hole mobility ranges for common p-type organic semiconductors and the impact of various processing parameters.

| Organic Semiconductor          | Deposition Method                                 | Post-Treatment  | Typical Hole Mobility (cm <sup>2</sup> /Vs)    | Key Influencing Factors                                               |

|--------------------------------|---------------------------------------------------|-----------------|------------------------------------------------|-----------------------------------------------------------------------|

| Pentacene                      | Thermal Evaporation                               | None            | 0.1 - 1.0                                      | Substrate temperature, deposition rate, dielectric surface.           |

| Thermal Evaporation            | Thermal Annealing                                 | 1.0 - 3.0       | Annealing temperature and duration.[12]        |                                                                       |

| Solution (precursor)           | Thermal Annealing                                 | ~1.0            | Annealing conditions to convert precursor.[13] |                                                                       |

| TIPS-Pentacene                 | Solution (e.g., spray coating)                    | Post-annealing  | ~0.056                                         | Solvent choice, solution concentration. [14]                          |

| Solution (e.g., spray coating) | In situ annealing (60°C)                          | ~0.191          | Substrate temperature during deposition.[14]   |                                                                       |

| C8-BTBT                        | Solution (blend with PS)                          | None (pristine) | 0.45 - 1.68                                    | Channel length dependency can indicate contact resistance issues.[15] |

| Solution (blend with PS)       | Solvent Vapor Annealing (CH <sub>3</sub> CN)      | ~1.02           | Heals shallow interfacial traps. [15]          |                                                                       |

| Solution (blend with PS)       | SVA + Doping (I <sub>2</sub> /CH <sub>3</sub> CN) | ~4.11           | Reduces deep traps and contact                 |                                                                       |

resistance.[15]

---

## Detailed Experimental Protocols

### Protocol 1: Atomic Force Microscopy (AFM) for Film Morphology Characterization

**Objective:** To visualize the surface topography of the organic semiconductor thin film to assess grain size, shape, and overall film continuity.

**Methodology:**

- **Sample Preparation:**

- Use a freshly prepared organic semiconductor film on the desired substrate (e.g., Si/SiO<sub>2</sub> with dielectric).

- Ensure the sample is free of dust and contaminants by gently blowing with dry nitrogen.

- Mount the sample on the AFM stage using double-sided tape or a magnetic holder.

- **AFM Setup and Cantilever Selection:**

- Use a high-quality silicon cantilever suitable for tapping mode (also known as intermittent-contact mode) to minimize damage to the soft organic film. A typical resonant frequency for such cantilevers is around 300 kHz.[16]

- Install the cantilever and align the laser onto the back of the cantilever, ensuring the reflected spot is centered on the photodiode detector.

- **Tuning and Approach:**

- Perform a frequency sweep to determine the resonant frequency of the cantilever.

- Set the drive frequency slightly below the resonant peak.

- Engage the cantilever with the sample surface automatically. The system will approach the tip to the surface until a predefined setpoint amplitude is reached.

- Image Acquisition:

- Start with a large scan area (e.g., 10  $\mu\text{m}$  x 10  $\mu\text{m}$ ) to get an overview of the film morphology.

- Optimize the scan parameters:

- Scan Rate: Typically between 0.5 and 1 Hz. Slower rates generally produce higher quality images.

- Setpoint: Adjust the amplitude setpoint to control the tip-sample interaction force. A higher setpoint (closer to the free air amplitude) corresponds to a gentler tapping.

- Gains (Proportional and Integral): Adjust the feedback gains to accurately track the surface topography. Poorly tuned gains can result in imaging artifacts.

- Acquire both height and phase images. The height image provides topographical information, while the phase image can reveal variations in material properties.

- Zoom in on areas of interest for higher-resolution scans (e.g., 1  $\mu\text{m}$  x 1  $\mu\text{m}$ ) to resolve individual grains.

- Data Analysis:

- Use the AFM software to flatten the images and remove any bowing or tilt artifacts.

- Perform a grain size analysis to quantify the average grain size and distribution.

- Measure the root-mean-square (RMS) roughness of the film.

## Protocol 2: X-ray Diffraction (XRD) for Crystallinity Analysis

Objective: To determine the crystalline structure, molecular orientation, and degree of crystallinity of the organic semiconductor thin film.

Methodology:

- Sample Preparation and Mounting:

- Use a thin film sample of sufficient area for the X-ray beam spot.

- Mount the sample on the XRD stage, ensuring it is flat and at the correct height (z-axis).

- Instrument Setup:

- Use a diffractometer with a Cu K $\alpha$  X-ray source ( $\lambda = 1.54 \text{ \AA}$ ), which is standard for many materials.

- Configure the instrument for a Bragg-Brentano ( $\theta$ - $2\theta$ ) scan, which is suitable for analyzing the out-of-plane crystal orientation in thin films.

- Scan Parameter Selection:

- $2\theta$  Range: Select a range that covers the expected diffraction peaks for your material. For many organic semiconductors, a range of  $2^\circ$  to  $40^\circ$  is appropriate.

- Step Size: A smaller step size (e.g.,  $0.02^\circ$ ) will provide higher resolution.

- Dwell Time (or Scan Speed): A longer dwell time per step will improve the signal-to-noise ratio, which is important for thin films that may have weak diffraction signals.

- Data Acquisition:

- Perform the  $2\theta/\omega$  scan. The instrument will rotate the X-ray source and detector in a coupled manner to measure the intensity of diffracted X-rays at different angles.

- Data Analysis:

- Identify the positions of the diffraction peaks in the resulting diffractogram.

- Use Bragg's Law ( $n\lambda = 2d \sin\theta$ ) to calculate the d-spacing (interplanar spacing) for each peak.

- Compare the observed d-spacings with known values from literature or databases to identify the crystal phases and orientations present in your film. For layered organic

semiconductor structures, a series of (00l) peaks is often observed, indicating a preferential edge-on or face-on molecular orientation.

- Apply the Scherrer equation to the full width at half maximum (FWHM) of a prominent diffraction peak to estimate the crystallite size perpendicular to the substrate.[17] This provides a measure of the crystalline domain size.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [mdpi.com](http://mdpi.com) [mdpi.com]

- 2. Morphology control for high performance organic thin film transistors (2011) | Wei Shao | 113 Citations [scispace.com]

- 3. [researchgate.net](http://researchgate.net) [researchgate.net]

- 4. [pubs.acs.org](http://pubs.acs.org) [pubs.acs.org]

- 5. [researchgate.net](http://researchgate.net) [researchgate.net]

- 6. [pubs.aip.org](http://pubs.aip.org) [pubs.aip.org]

- 7. [tandfonline.com](http://tandfonline.com) [tandfonline.com]

- 8. Engineering of the dielectric–semiconductor interface in organic field-effect transistors - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 9. [pubs.acs.org](http://pubs.acs.org) [pubs.acs.org]

- 10. [researchgate.net](http://researchgate.net) [researchgate.net]

- 11. [pubs.acs.org](http://pubs.acs.org) [pubs.acs.org]

- 12. [PDF] Effect of annealing on the mobility and morphology of thermally activated pentacene thin film transistors | Semantic Scholar [semanticscholar.org]

- 13. Organic semiconductors for organic field-effect transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 14. Effect of In Situ Annealing Treatment on the Mobility and Morphology of TIPS-Pentacene-Based Organic Field-Effect Transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 15. [pubs.acs.org](https://pubs.acs.org) [pubs.acs.org]

- 16. [pubs.acs.org](https://pubs.acs.org) [pubs.acs.org]

- 17. [astro1.panet.utoledo.edu](https://astro1.panet.utoledo.edu) [astro1.panet.utoledo.edu]

- To cite this document: BenchChem. [Technical Support Center: Troubleshooting Low Hole Mobility in OFETs]. BenchChem, [2026]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b160511#troubleshooting-low-hole-mobility-in-ofets\]](https://www.benchchem.com/product/b160511#troubleshooting-low-hole-mobility-in-ofets)

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)