# Technical Support Center: Optimizing AlAs/GaAs Heterostructures for High Performance

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Aluminum arsenide

Cat. No.: B1584279

[Get Quote](#)

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing AlAs/GaAs heterostructures for high-performance applications.

## Troubleshooting Guides & FAQs

This section addresses specific issues that may be encountered during the experimental process of growing and characterizing AlAs/GaAs heterostructures.

### Crystal Growth & Material Quality

**Q1:** What are the common causes of oval defects on the surface of my MBE-grown AlAs/GaAs heterostructures, and how can I eliminate them?

**A:** Oval defects are one of the most common morphological issues in the molecular beam epitaxy (MBE) growth of GaAs films.<sup>[1]</sup> They typically appear as hillocks, are elongated along the  $<110>$  direction, and can range in size from 1-20  $\mu\text{m}$  in length.<sup>[1]</sup> These defects can negatively impact device performance by increasing leakage currents.<sup>[1]</sup>

The primary causes of oval defects are generally associated with the gallium (Ga) effusion cell and substrate preparation.<sup>[1][2]</sup> Specific sources include:

- Ga Oxides: Oxides such as  $\text{Ga}_2\text{O}$  in the Ga melt are a major contributor.<sup>[2]</sup>

- Ga Spitting: Ejection of liquid Ga droplets from the effusion cell.[2]

- Substrate Contamination: Particulate matter or dust on the wafer surface can act as nucleation sites for defects.[1][3]

- Excessive Arsenic (As) Clusters: Can also contribute to defect formation.[1]

Solutions:

- Proper System Bakeout: Thoroughly bake the MBE system and outgas the Ga cell to reduce Ga-oxides.[3]

- Source Purity: Use high-purity source materials.

- Substrate Preparation: Implement rigorous substrate cleaning procedures to eliminate surface contaminants.

- Growth Conditions: Optimizing growth parameters, such as the Ga cell temperature, can help mitigate these defects.[4]

Q2: My AlAs/GaAs heterostructure exhibits high surface roughness. What are the potential causes and how can I achieve a smoother surface?

A: High surface roughness in AlAs/GaAs heterostructures can be attributed to several factors, primarily related to the growth kinetics of AlAs and the presence of impurities.

Potential Causes:

- Low Al Adatom Mobility: Aluminum adatoms have a lower surface migration length compared to Ga adatoms, which can lead to the formation of mounds and a rougher surface, especially at lower growth temperatures.[5]

- Impurity Segregation: Background impurities, particularly from the Al source, can segregate to the growth surface and disrupt smooth layer formation.[1][3]

- Non-optimal Growth Temperature: Growth temperature significantly impacts adatom mobility and impurity incorporation.

### Solutions:

- Increase Growth Temperature: Higher growth temperatures (>690 °C) can significantly enhance Al adatom migration, leading to smoother AlGaAs layers.[5]

- Use Misoriented Substrates: Employing substrates with a slight miscut (e.g., 2° off (100) towards <111>A) promotes step-flow growth, resulting in smoother interfaces.[3][5]

- Incorporate GaAs Monolayers: Inserting thin GaAs layers within the AlAs can help to smooth the growth front.[3]

- Utilize High-Purity Sources: Using purer Al and other source materials minimizes impurity-induced roughening.[3]

Q3: How can I achieve sharp and abrupt interfaces between AlAs and GaAs layers?

A: Achieving atomically sharp interfaces is crucial for the performance of many heterostructure devices. The "inverted" interface (GaAs grown on AlAs) is often more challenging to grow smoothly than the "normal" interface (AlAs on GaAs).

### Strategies for Sharper Interfaces:

- Growth Interruption: Pausing the growth for a short period (e.g., 10 seconds) after depositing a layer can allow adatoms to migrate to step edges, resulting in smoother and more abrupt interfaces.[2]

- Optimized Growth Temperature: As with surface roughness, a sufficiently high growth temperature is necessary to ensure adequate adatom mobility for the formation of sharp interfaces.

- High-Purity Sources: Minimizing impurities prevents segregation at the interface, which can cause roughness and grading.[1][3]

- Use of Misoriented Substrates: Promotes a step-flow growth mode, which naturally leads to sharper interfaces.[3][5]

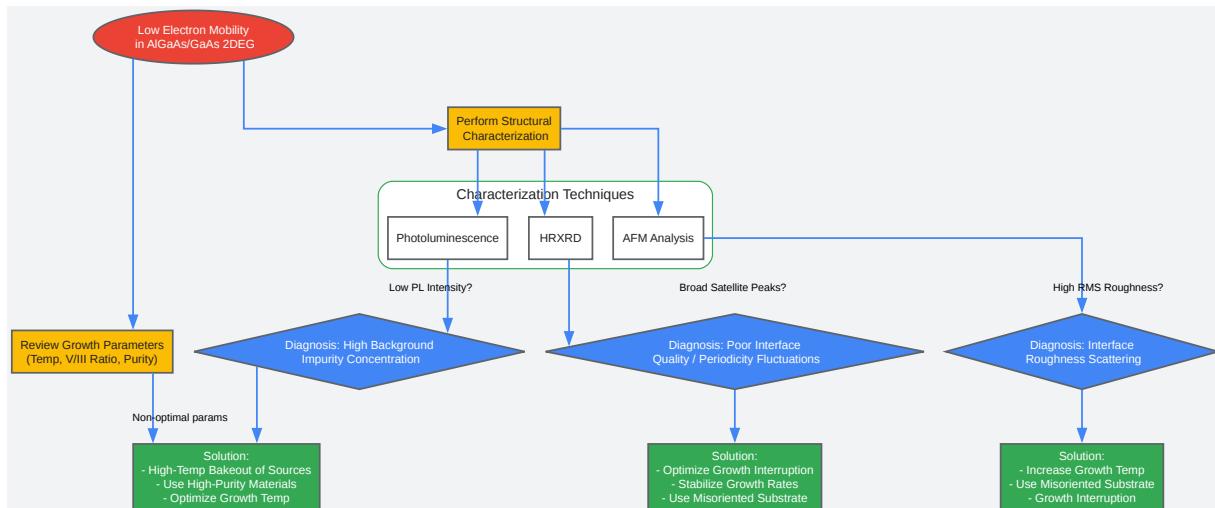

Q4: I am observing low electron mobility in my AlGaAs/GaAs 2DEG. What are the likely scattering mechanisms limiting the mobility?

A: Low electron mobility in a two-dimensional electron gas (2DEG) at low temperatures is primarily limited by scattering from impurities and interface roughness.[\[6\]](#)

Dominant Scattering Sources:

- **Background Impurities:** Unintentional impurities in the GaAs channel and AlGaAs barrier layers act as scattering centers.[\[7\]](#) Common impurities include carbon, oxygen, and sulfur.[\[7\]](#)

- **Remote Ionized Donors:** Scattering from the ionized dopants in the modulation-doped layer. The thickness of the undoped spacer layer is critical in minimizing this.[\[6\]](#)

- **Interface Roughness:** Imperfections at the AlGaAs/GaAs interface can scatter electrons, especially at high electron densities.[\[6\]](#)

- **Alloy Scattering:** In AlGaAs, the random distribution of Al and Ga atoms can cause scattering, though this is often less significant for electrons confined primarily in the GaAs well.[\[6\]](#)

Troubleshooting Steps:

- **Reduce Background Impurities:** Ensure a clean MBE system and use high-purity source materials. High-temperature outgassing of effusion cells is crucial.[\[8\]](#)

- **Optimize Spacer Layer Thickness:** Increasing the spacer layer thickness reduces scattering from remote ionized donors, but may also decrease the 2DEG density.

- **Improve Interface Quality:** Implement the strategies for achieving sharp interfaces mentioned in Q3.

- **Optimize Growth Temperature:** Higher growth temperatures generally lead to lower incorporation of background impurities and improved crystal quality.[\[1\]](#)

Device Performance

Q5: My AlAs layers are oxidizing uncontrollably during device processing. How can I control the AlAs oxidation rate?

A: The high reactivity of AlAs with water vapor, leading to the formation of aluminum oxide (AlO<sub>x</sub>), is a well-known challenge. However, this can also be a useful fabrication technique if controlled properly.

Methods for Controlling Oxidation:

- Digital Alloy Heterostructures: Using superlattices of AlAs/Al<sub>x</sub>Ga<sub>1-x</sub>As instead of bulk AlAs allows for fine-tuning of the oxidation rate by varying the composition and thickness of the Al<sub>x</sub>Ga<sub>1-x</sub>As layers.

- Wet Thermal Oxidation Parameters: The oxidation rate is highly dependent on the temperature and water vapor pressure during the process.

- Ion Implantation: Introducing silicon ions can reduce the oxidation rate and its anisotropy.

Q6: The photoluminescence (PL) intensity from my AlAs/GaAs quantum wells is weak. What could be the cause?

A: Weak PL intensity is often an indication of poor material quality and the presence of non-radiative recombination centers.

Potential Causes:

- Non-radiative Defects: Impurities and crystal defects within the quantum well or at the interfaces can act as traps for charge carriers, which then recombine non-radiatively.

- Poor Carrier Confinement: Rough interfaces can lead to fluctuations in the confinement potential, which can reduce the radiative efficiency.

- Surface Recombination: For near-surface quantum wells, recombination at the surface can be a significant factor.

Solutions:

- Improve Material Purity: Reduce background impurities through system bakeout and the use of high-purity sources.

- Optimize Growth Conditions: Fine-tune the growth temperature and V/III ratio to minimize defect formation.

- Enhance Interface Quality: Employ techniques like growth interruption to create smoother, more abrupt interfaces.

- Passivation: For near-surface structures, a suitable capping layer can passivate the surface and reduce surface recombination.

## Data Presentation

Table 1: Influence of MBE Growth Parameters on AlAs/GaAs Heterostructure Properties

| Parameter                   | Typical Range | Effect on Surface Roughness                                                                                                     | Effect on Defect Density                                                                              | Effect on Electron Mobility                                                                                                |

|-----------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Substrate Temperature (°C)  | 580 - 720     | Higher temperature generally leads to lower roughness due to increased adatom mobility. [5][9]                                  | Optimal temperature window exists; too low can lead to defects, too high can cause decomposition. [9] | Higher temperatures often result in higher mobility due to reduced impurity incorporation and improved crystal quality.[1] |

| V/III Ratio (As/Ga BEP)     | 10 - 40       | Can influence surface reconstruction and morphology; an optimal ratio is needed to avoid Ga-rich or As-rich related defects.[9] | Both very low and very high ratios can increase defect density.[10][11]                               | An optimized V/III ratio is crucial for achieving high mobility by minimizing compensating defects.                        |

| Growth Rate (μm/hr)         | 0.5 - 1.5     | Lower growth rates can sometimes improve surface smoothness by allowing more time for adatom migration.                         | Can influence impurity incorporation and defect formation.                                            | Lower growth rates are often used for high-mobility structures to achieve better control and higher purity.                |

| Spacer Layer Thickness (nm) | 5 - 80        | Not a direct effect on surface roughness.                                                                                       | Not a direct effect on crystal defects.                                                               | Increasing spacer thickness reduces remote ionized impurity scattering, generally                                          |

increasing

mobility up to a

point.[6]

Table 2: Typical Performance Metrics for High-Quality AlGaAs/GaAs 2DEGs

| Parameter                                       | Value                    | Conditions              | Reference |

|-------------------------------------------------|--------------------------|-------------------------|-----------|

| Peak Electron Mobility<br>(cm <sup>2</sup> /Vs) | > 10 x 10 <sup>6</sup>   | Low Temperature (< 4K)  | [7]       |

| Electron Density<br>(cm <sup>-2</sup> )         | 1 - 3 x 10 <sup>11</sup> | Low Temperature (< 4K)  | [7]       |

| Interface Roughness<br>(nm RMS)                 | < 0.3                    | Measured by AFM         | [12]      |

| Background Impurity Conc. (cm <sup>-3</sup> )   | < 5 x 10 <sup>13</sup>   | Estimated from mobility | [7]       |

## Experimental Protocols

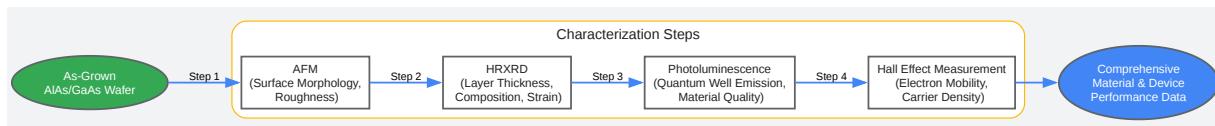

### 1. Atomic Force Microscopy (AFM) for Surface Morphology Characterization

This protocol outlines the basic steps for analyzing the surface topography of an AlAs/GaAs heterostructure.

- Sample Preparation:

- Cleave a small piece of the wafer (e.g., 5x5 mm) using a diamond scribe.

- Ensure the sample surface is free of dust and contaminants by blowing it with dry nitrogen. Avoid solvent cleaning unless necessary, as it can leave residues.

- Mount the sample on an AFM stub using double-sided adhesive tape.

- AFM Setup and Calibration:

- Install a suitable AFM cantilever (e.g., a silicon tip for tapping mode).

- Load the sample into the AFM.

- Align the laser onto the cantilever and adjust the photodetector to obtain a strong signal.

- Perform a frequency sweep to determine the cantilever's resonant frequency for tapping mode operation.

- Calibrate the scanner using a standard calibration grating.

- Image Acquisition:

- Approach the tip to the sample surface.

- Set the scan parameters:

- Scan Size: Start with a larger area (e.g., 10x10  $\mu\text{m}$ ) to get an overview, then zoom in to smaller areas (e.g., 1x1  $\mu\text{m}$ ) for high-resolution imaging.

- Scan Rate: Typically 0.5 - 1 Hz.

- Setpoint: Adjust for optimal tracking of the surface with minimal tip-sample interaction force.

- Gains (Integral and Proportional): Optimize to minimize feedback loop noise and accurately track the topography.

- Acquire the height and amplitude/phase images.

- Data Analysis:

- Use AFM analysis software to process the images.

- Perform a plane fit or flattening to remove sample tilt.

- Calculate the root-mean-square (RMS) roughness over a representative area.

- Analyze line profiles to measure the height of surface features.

- Identify and quantify any surface defects like oval defects or pits.

## 2. Photoluminescence (PL) Spectroscopy of Quantum Wells (QWs)

This protocol describes the procedure for obtaining and interpreting PL spectra from AlAs/GaAs QWs.

- Sample Preparation:

- Mount the sample on a cold finger in a cryostat for low-temperature measurements.

- Evacuate the cryostat to a high vacuum.

- Cool the sample to the desired temperature (e.g., 4K or 77K).

- PL System Setup:

- Use a laser with an energy above the bandgap of the material to be studied (e.g., a HeNe laser at 632.8 nm or an Ar-ion laser).

- Focus the laser beam onto the sample surface.

- Collect the emitted light using appropriate optics (lenses and mirrors).

- Focus the collected light onto the entrance slit of a spectrometer.

- Use a suitable detector, such as a silicon CCD or an InGaAs detector, depending on the emission wavelength.

- Data Acquisition:

- Set the spectrometer to the expected wavelength range of the QW emission.

- Acquire the PL spectrum. Adjust the integration time and laser power to obtain a good signal-to-noise ratio. Be cautious of sample heating with high laser power.

- To study recombination mechanisms, perform power-dependent PL by varying the laser intensity with neutral density filters.

- To study thermal quenching and carrier dynamics, perform temperature-dependent PL by varying the sample temperature.

- Data Analysis:

- Identify the peak emission energy, which corresponds to the recombination of excitons in the quantum well.

- The full width at half maximum (FWHM) of the PL peak provides an indication of the material quality and interface roughness. A narrower FWHM generally indicates better quality.

- The integrated PL intensity is proportional to the radiative efficiency.

- Compare the experimental peak energy with theoretical calculations based on a finite quantum well model to verify the well width.

### 3. High-Resolution X-ray Diffraction (HRXRD) of Superlattices

This protocol provides a guide for characterizing the structural parameters of an AlAs/GaAs superlattice.

- Sample Preparation:

- Mount the sample on the diffractometer stage, ensuring it is flat.

- HRXRD System Setup:

- Use a diffractometer with a high-resolution setup, typically including a monochromator (e.g., a four-crystal Ge(220)) to produce a highly collimated and monochromatic X-ray beam (usually Cu K $\alpha$ 1 radiation).

- Align the sample to the Bragg condition for a substrate reflection (e.g., the GaAs (004) reflection).

- Data Acquisition:

- Perform a  $\omega$ -2θ scan around the substrate Bragg peak. This scan will reveal the superlattice satellite peaks.

- The scan range should be wide enough to encompass several orders of satellite peaks.

- Data Analysis:

- The angular separation ( $\Delta\theta$ ) between adjacent satellite peaks is inversely related to the superlattice period (D) by the formula:  $D = \lambda / (2 * \cos(\theta_B) * \Delta\theta)$ , where  $\lambda$  is the X-ray wavelength and  $\theta_B$  is the Bragg angle of the substrate.

- The position of the zeroth-order satellite peak relative to the substrate peak gives information about the average lattice parameter (and thus the average composition) of the superlattice.

- The intensities and widths of the satellite peaks are related to the individual layer thicknesses, interface sharpness, and overall structural quality.

- For a detailed quantitative analysis, the experimental data can be compared with simulations based on dynamical diffraction theory. This allows for the precise determination of layer thicknesses, compositions, and strain.

## Visualizations

Troubleshooting Workflow for Low Electron Mobility in AlGaAs/GaAs 2DEG

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for diagnosing and addressing low electron mobility.

### Experimental Workflow for AlAs/GaAs Heterostructure Characterization

[Click to download full resolution via product page](#)

Caption: Sequential workflow for comprehensive material and electrical characterization.

**Need Custom Synthesis?**

*BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.*

*Email: [info@benchchem.com](mailto:info@benchchem.com) or Request Quote Online.*

## References

- 1. researchgate.net [researchgate.net]

- 2. coefs.charlotte.edu [coefs.charlotte.edu]

- 3. researchgate.net [researchgate.net]

- 4. redalyc.org [redalyc.org]

- 5. researchgate.net [researchgate.net]

- 6. zumbuhllab.unibas.ch [zumbuhllab.unibas.ch]

- 7. arxiv.org [arxiv.org]

- 8. weizmann.elsevierpure.com [weizmann.elsevierpure.com]

- 9. High-Quality Single-Step Growth of GaAs on C-Plane Sapphire by Molecular Beam | MDPI [mdpi.com]

- 10. researchgate.net [researchgate.net]

- 11. matec-conferences.org [matec-conferences.org]

- 12. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Optimizing AlAs/GaAs Heterostructures for High Performance]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1584279#optimizing-alas-gaas-heterostructures-for-high-performance>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)