# Improving charge carrier mobility in Vat Green 3 based transistors

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Vat Green 3

Cat. No.: B1582166

[Get Quote](#)

## Technical Support Center: Vat Green 3 Based Transistors

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers and scientists working on improving charge carrier mobility in **Vat Green 3** (VG3) based Organic Field-Effect Transistors (OFETs).

## Frequently Asked Questions (FAQs) & Troubleshooting

Q1: My fabricated **Vat Green 3** OFET shows very low or no charge carrier mobility. What are the common causes?

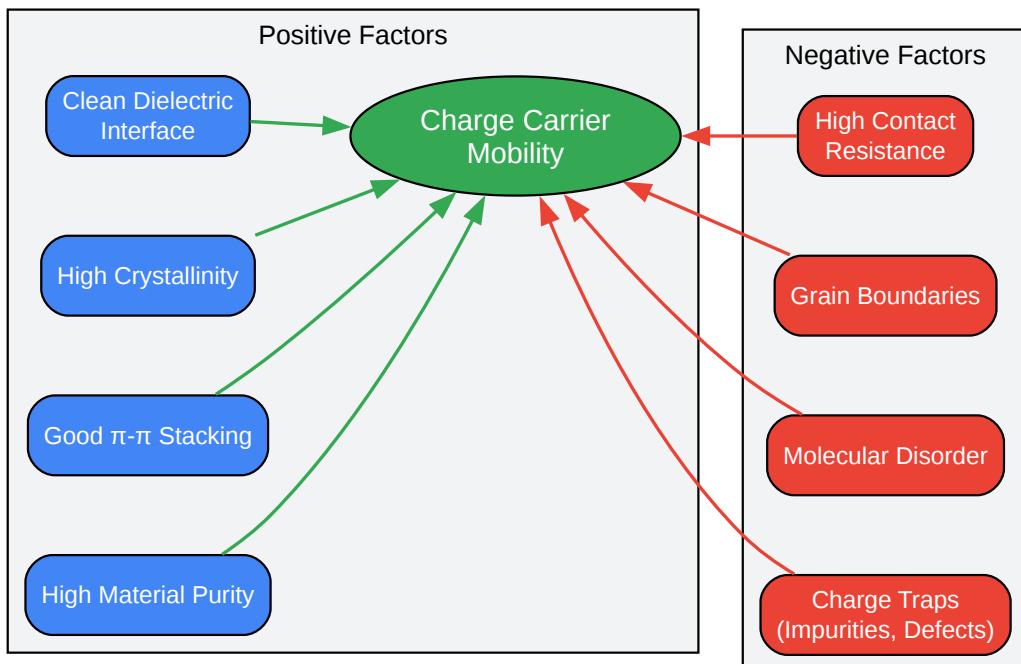

Low charge carrier mobility in VG3 transistors is a common issue and can stem from several factors:

- Poor Film Quality: The most significant factor is often the morphology and crystallinity of the VG3 thin film. Amorphous or poorly ordered films have numerous trap states and grain boundaries that hinder charge transport.[\[1\]](#)[\[2\]](#)

- Impure Material: Commercial-grade VG3 is a dye and may contain impurities that act as charge traps.[\[3\]](#) Purification is a critical first step.

- Unfavorable Dielectric Interface: The interface between the organic semiconductor and the gate dielectric is where charge transport occurs.[4][5][6] A rough or chemically incompatible surface can introduce traps and disrupt molecular packing, severely limiting mobility.[6][7]

- Poor Electrode Contacts: A significant energy barrier between the source/drain electrodes and the VG3 active layer can lead to high contact resistance, which results in an underestimation of the intrinsic mobility.[8]

- Environmental Degradation: Many organic semiconductors are sensitive to oxygen and moisture, which can act as charge traps or lead to chemical degradation of the material.[1][9]

Q2: How can I improve the crystallinity of my **Vat Green 3** thin film?

Improving the crystallinity is crucial for enhancing mobility. Consider the following methods:

- Substrate Temperature Control: During deposition (especially thermal evaporation), maintaining the substrate at an elevated temperature can provide molecules with sufficient thermal energy to arrange themselves into well-ordered crystalline domains.

- Low Deposition Rate: A slow deposition rate during thermal evaporation allows molecules more time to find their lowest energy state, promoting the growth of larger, more ordered crystals.

- Post-Deposition Annealing:

- Thermal Annealing: Heating the film after deposition can improve molecular ordering and reduce defects. The optimal temperature must be determined experimentally, as excessive heat can damage the film.[10]

- Solvent Vapor Annealing (SVA): Exposing the film to a saturated solvent vapor can induce recrystallization and improve molecular packing, often leading to higher mobility.[11]

Q3: What is the impact of the gate dielectric on device performance?

The gate dielectric plays a critical role. Its surface properties directly influence the growth and morphology of the first few semiconductor layers where the conductive channel forms.[4][5][12]

- Surface Energy: The surface energy of the dielectric affects the wetting and growth mode of the VG3 film. Modifying the dielectric surface with a Self-Assembled Monolayer (SAM), such as octadecyltrichlorosilane (OTS), can reduce surface traps and promote better molecular ordering, leading to a significant increase in mobility.[8]

- Roughness: A smoother dielectric surface is generally preferred as it minimizes disruptions to the semiconductor's crystal structure at the interface.[7]

Q4: My device performance degrades quickly when exposed to air. What can I do to improve stability?

Environmental instability is a known challenge for organic electronics.[1]

- Encapsulation: The most effective method is to encapsulate the device. This can be done using materials like glass, epoxy, or specialized thin-film encapsulation layers (e.g., alternating organic/inorganic layers). Recent work on similar organic molecules has shown success using 2D materials like hexagonal boron nitride (h-BN) for encapsulation.[13]

- Inert Atmosphere: All fabrication and measurement steps should ideally be performed in an inert atmosphere, such as a nitrogen or argon-filled glovebox, to minimize exposure to oxygen and moisture.[3]

## Quantitative Data Summary

While specific data for **Vat Green 3** OFETs is limited in the literature, the following table summarizes typical charge carrier mobility values for various organic semiconductors and highlights the impact of different optimization techniques, providing a benchmark for your experiments.

| Organic Semiconductor       | Deposition Method        | Dielectric/Interface          | Mobility (cm <sup>2</sup> /Vs) | Key Optimization          | Reference            |

|-----------------------------|--------------------------|-------------------------------|--------------------------------|---------------------------|----------------------|

| Vat Orange 3                | Physical Vapor Transport | h-BN                          | 0.14                           | 2D Material Encapsulation | <a href="#">[13]</a> |

| Pentacene (Polycrystalline) | Thermal Evaporation      | OTS-treated SiO <sub>2</sub>  | ~ 6                            | Interface Engineering     | <a href="#">[14]</a> |

| DPP-based Polymers          | Solution Shearing        | OTS-treated SiO <sub>2</sub>  | ~ 10                           | Molecular Engineering     | <a href="#">[10]</a> |

| P3HT                        | Spin Coating             | HMDS-treated SiO <sub>2</sub> | 0.01 - 0.1                     | Thermal Annealing         | <a href="#">[15]</a> |

| Organic Blends (PBT:PD)     | Spin Coating             | OTS-treated SiO <sub>2</sub>  | ~ 0.001                        | Thermal Annealing         | <a href="#">[8]</a>  |

## Experimental Protocols

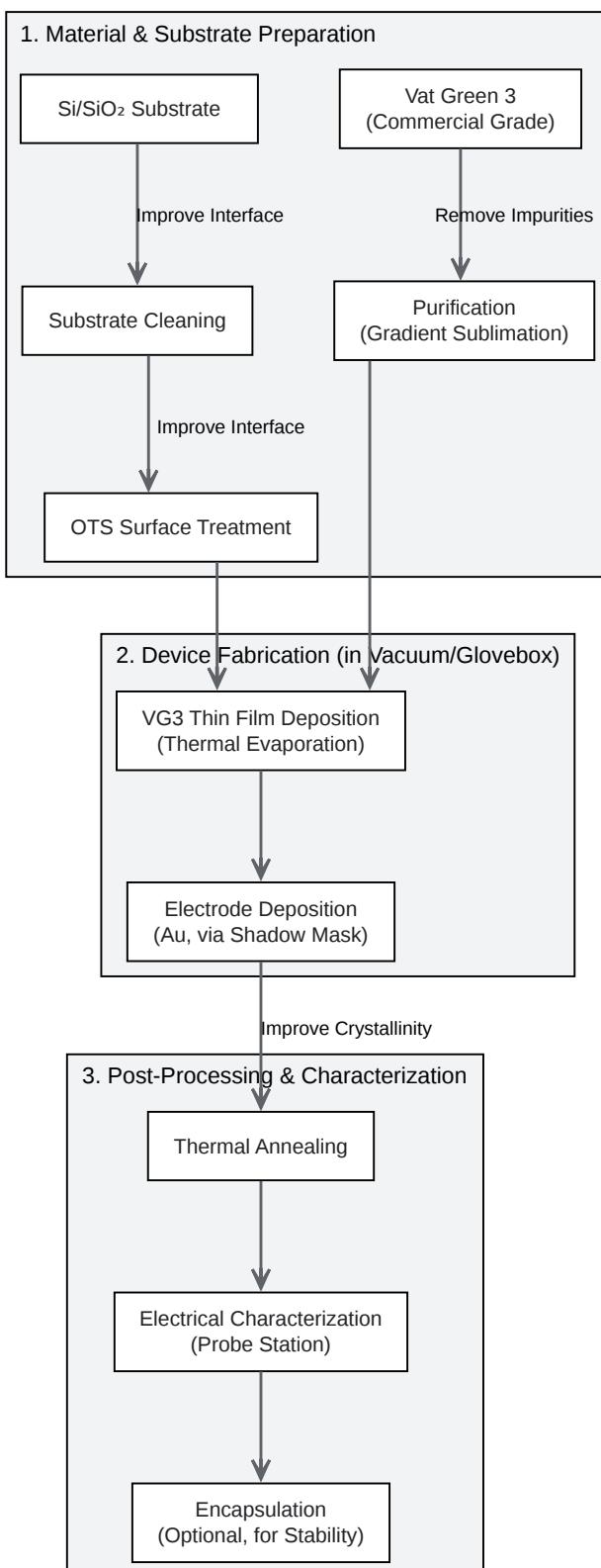

### Protocol 1: Purification of Vat Green 3

Objective: To remove impurities from commercial-grade VG3 powder that can act as charge traps.

Method: Temperature Gradient Sublimation

- Place a quartz boat containing the as-received VG3 powder inside a long quartz tube.

- Insert the quartz tube into a horizontal tube furnace with multiple heating zones.

- Evacuate the quartz tube to a high vacuum (< 10<sup>-6</sup> Torr).

- Establish a temperature gradient along the tube. Heat the zone with the VG3 source material to its sublimation temperature while keeping downstream zones at progressively lower

temperatures.

- Impurities with different sublimation points will condense in different zones. The purified VG3 will deposit as a crystalline film in a specific temperature zone.

- After cooling, carefully collect the purified VG3 crystals from the desired zone inside an inert atmosphere glovebox.

#### Protocol 2: OFET Fabrication (Bottom-Gate, Top-Contact)

Objective: To fabricate a standard OFET structure for electrical characterization.

- Substrate Cleaning:

- Use heavily n-doped silicon wafers with a thermally grown 300 nm SiO<sub>2</sub> layer (Si/SiO<sub>2</sub>). The silicon acts as the gate electrode and the SiO<sub>2</sub> as the gate dielectric.

- Sonicate the substrates sequentially in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a nitrogen gun and bake at 120°C for 20 minutes to remove residual moisture.

- Dielectric Surface Treatment (Optional but Recommended):

- Expose the substrates to an oxygen plasma to create hydroxyl groups on the SiO<sub>2</sub> surface.

- Immediately immerse the substrates in a 10 mM solution of octadecyltrichlorosilane (OTS) in anhydrous toluene for 30 minutes inside a glovebox.

- Rinse the substrates with fresh toluene and bake at 120°C for 45 minutes to form a stable monolayer.

- **Vat Green 3 Deposition:**

- Transfer the substrates and purified VG3 to a high-vacuum thermal evaporator.

- Deposit a 40-50 nm thick film of VG3 at a low rate (e.g., 0.1-0.2 Å/s). Maintain the substrate at an optimized temperature (e.g., 80-120°C) during deposition.

- Source/Drain Electrode Deposition:

- Using a shadow mask, thermally evaporate 50 nm of Gold (Au) to define the source and drain electrodes. A thin (5 nm) adhesion layer of Chromium (Cr) or Molybdenum Oxide (MoO<sub>3</sub>) may be used between the VG3 and Au.

- Post-Fabrication Annealing:

- Transfer the completed devices to a hot plate inside a glovebox.

- Anneal the devices at a predetermined optimal temperature (e.g., 100-150°C) for 30-60 minutes.

- Allow the devices to cool slowly to room temperature before characterization.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Experimental workflow for fabricating and testing **Vat Green 3** OFETs.

[Click to download full resolution via product page](#)

Caption: Key factors influencing charge carrier mobility in organic semiconductors.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [ossila.com](http://ossila.com) [ossila.com]

- 2. [quora.com](http://quora.com) [quora.com]

- 3. Industrial vat orange dyes for organic field effect transistors - Journal of Materials Chemistry C (RSC Publishing) DOI:10.1039/D3TC03919F [pubs.rsc.org]

- 4. chem.pku.edu.cn [chem.pku.edu.cn]

- 5. Engineering of the dielectric–semiconductor interface in organic field-effect transistors - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 6. crg.postech.ac.kr [crg.postech.ac.kr]

- 7. researchgate.net [researchgate.net]

- 8. pure.mpg.de [pure.mpg.de]

- 9. Organic field-effect transistor-based sensors: recent progress, challenges and future outlook - Journal of Materials Chemistry C (RSC Publishing) DOI:10.1039/D4TC04265D [pubs.rsc.org]

- 10. mdpi.com [mdpi.com]

- 11. Effects of solvent vapor annealing on the optical properties and surface adhesion of conjugated D :A thin films - Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 12. Interface engineering of organic electronics - Journal of Materials Chemistry (RSC Publishing) DOI:10.1039/C002978P [pubs.rsc.org]

- 13. High-Performance Organic Field-Effect Transistors Based on Two-Dimensional Vat Orange 3 Crystals [cpl.iphy.ac.cn]

- 14. researchgate.net [researchgate.net]

- 15. ossila.com [ossila.com]

- To cite this document: BenchChem. [Improving charge carrier mobility in Vat Green 3 based transistors]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b1582166#improving-charge-carrier-mobility-in-vat-green-3-based-transistors>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)