# Minimizing device-to-device variation in TIPS-pentacene OFETs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

6,13-

Compound Name: *Bis(triisopropylsilyl)ethynyl*pentacene

ne

Cat. No.: B153593

[Get Quote](#)

## Technical Support Center: TIPS-Pentacene OFETs

This technical support center provides troubleshooting guidance and answers to frequently asked questions to help researchers, scientists, and drug development professionals minimize device-to-device variation in 6,13-bis(triisopropylsilyl) pentacene (TIPS-pentacene) Organic Field-Effect Transistors (OFETs).

## Frequently Asked Questions (FAQs)

**Q1:** What are the primary sources of device-to-device variation in TIPS-pentacene OFETs?

Device-to-device variation in TIPS-pentacene OFETs primarily stems from the lack of control over the crystalline film morphology.<sup>[1][2]</sup> Key factors influencing this include:

- Solvent Selection: The choice of solvent significantly impacts the microstructure and phase segregation of TIPS-pentacene films.<sup>[3][4]</sup> Solvents with higher boiling points, like tetralin, can promote more desirable crystallization.<sup>[3][5]</sup>

- Substrate Surface Energy: The condition of the dielectric surface is critical. Inconsistent surface treatments can lead to dewetting and non-uniform film formation.<sup>[6][7]</sup> Surface treatments with organosilanes are often used to passivate charge trapping sites and improve charge transport.<sup>[8]</sup>

- **Deposition Technique:** Methods like spin coating, drop casting, and bar coating produce films with different morphologies and grain sizes, affecting device performance.[6] The parameters within each technique (e.g., spin speed, coating speed, substrate angle) must be precisely controlled.[9][10]

- **Solution Preparation:** The concentration of the TIPS-pentacene solution and the use of polymer additives or solvent additives can alter crystal growth and film uniformity.[9][11]

- **Annealing Conditions:** Post-deposition thermal treatment (annealing) can significantly modify film morphology, improve crystallinity, and enhance device performance and consistency.[12][13]

**Q2:** How does the choice of solvent affect the uniformity of TIPS-pentacene films?

The solvent's properties, particularly its boiling point and interaction with TIPS-pentacene, are crucial for controlling crystallization.

- **High-Boiling-Point Solvents:** Solvents with high boiling points, such as tetralin and o-xylene, allow for a slower evaporation rate.[3][14] This extended drying time provides molecules more time to self-organize into larger, more ordered crystalline domains, which can lead to higher carrier mobility and better device performance.[3][5] For instance, OFETs processed from tetralin have shown higher mobility values than those from chlorobenzene.[3][4]

- **Solvent Additives:** The use of small amounts of solvent additives, like diphenyl ether (DPE) or chloronaphthalene (CN), can induce the formation of well-ordered crystalline domains, leading to enhanced hole transport and more consistent device performance.[11]

- **Binary Solvents:** Engineering binary solvent mixtures (e.g., toluene/n-amyl acetate or anisole/decane) can precisely control the evaporation rate and intermolecular interactions, leading to enlarged grain width and highly aligned crystals.[15]

**Q3:** Why is substrate surface treatment important for reducing device variation?

The interface between the dielectric and the semiconductor is critical for charge transport. Surface treatments help ensure this interface is uniform across all devices.

- **Hydrophobicity Control:** Surface treatments can modify the surface energy of the dielectric. Treating a hydrophilic SiO<sub>2</sub> surface with organosilanes like octadecyltrichlorosilane (OTS) or trichloro(phenyl)silane (PTS) makes it more hydrophobic, which can improve the ordering of the deposited TIPS-pentacene film and enhance charge transport.[8][16][17]

- **Reducing Trap States:** Silanol groups (Si-O-H) on the surface of SiO<sub>2</sub> can act as charge trapping sites, impeding performance. Passivating these groups with a self-assembled monolayer (SAM) reduces trapping and improves mobility and consistency.[8][17]

- **Preventing Dewetting:** A properly treated surface with uniform energy prevents the solution from dewetting, which would otherwise lead to discontinuous and non-uniform films.[6][7]

**Q4: What is the role of polymer blending in improving OFET consistency?**

Blending TIPS-pentacene with an insulating polymer, such as polystyrene (PS) or poly(triarylamine) (PTAA), is an effective strategy to control morphology and enhance performance.[3][9]

- **Morphology Control:** The polymer matrix can guide the crystallization of TIPS-pentacene. For example, adding PS can tailor the crystal structure from anisotropic (needle-like) to a more favorable spherulite structure, which provides better charge transport paths.[10][17]

- **Vertical Phase Separation:** During solvent evaporation, the polymer and TIPS-pentacene can vertically phase-separate. This process, when controlled, results in a thin, uniform layer of TIPS-pentacene at the dielectric interface, which is ideal for OFET operation.[3][4]

- **Improved Film Coverage:** The polymer binder can help form continuous films with better surface coverage, reducing issues caused by the anisotropic nature of pure TIPS-pentacene crystals.[10]

## Troubleshooting Guides

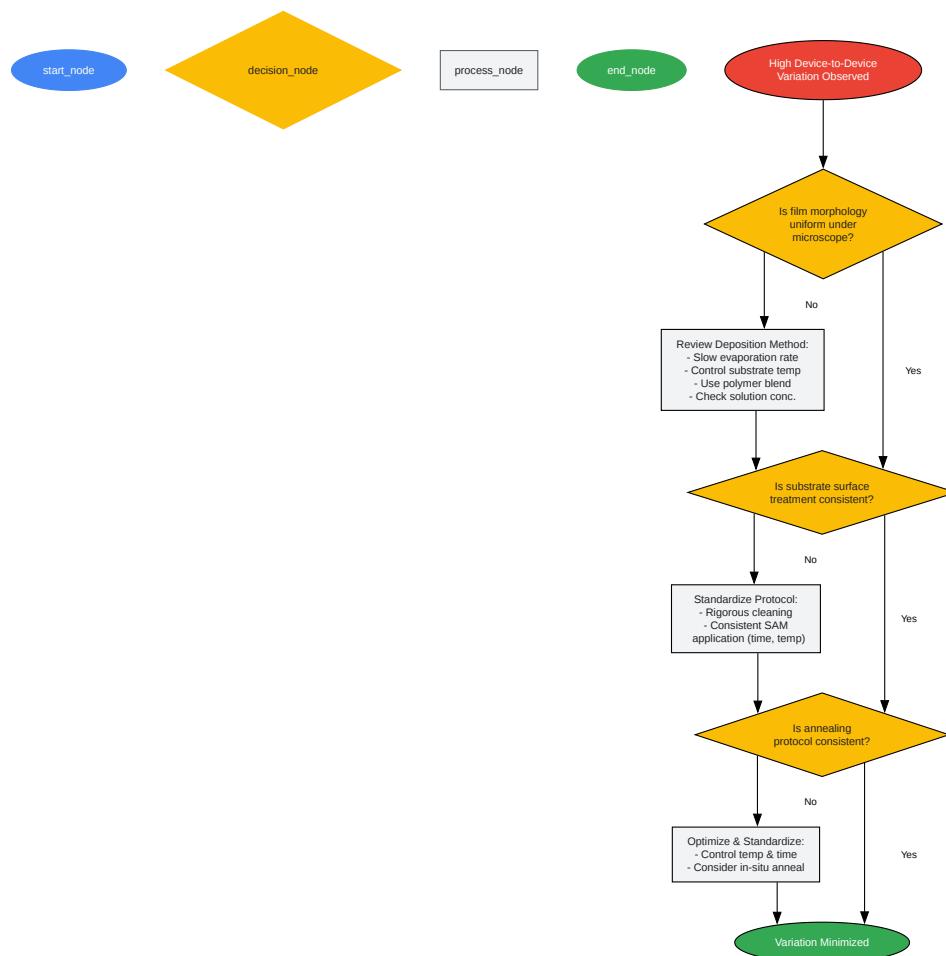

### Issue 1: High Variation in Carrier Mobility Across Devices

| Potential Cause                | Recommended Solution                                                                                                                                                                                                                                                                                                        |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inconsistent Film Morphology   | The primary reason for mobility variation is inconsistent crystal size, orientation, and connectivity. <a href="#">[1]</a> <a href="#">[2]</a>                                                                                                                                                                              |

| Non-uniform Crystallization    | Slow down the solvent evaporation rate. Use a high-boiling-point solvent (e.g., tetralin, o-xylene) or deposit the film in a solvent-saturated environment (e.g., inside a covered petri dish).<br><a href="#">[3]</a> <a href="#">[14]</a> <a href="#">[16]</a>                                                            |

| Anisotropic Crystal Growth     | Blend TIPS-pentacene with an insulating polymer like polystyrene (PS) to promote the growth of more uniform, spherulitic crystal structures instead of needle-like ones. <a href="#">[10]</a> <a href="#">[17]</a><br>Adding silica nanoparticles has also been shown to reduce crystal misorientation. <a href="#">[2]</a> |

| Inconsistent Substrate Surface | The surface energy of the dielectric must be uniform. Implement a rigorous and consistent substrate cleaning and surface treatment protocol (e.g., with PTS or OTS) for every batch.<br><a href="#">[16]</a> <a href="#">[17]</a>                                                                                           |

| Variable Deposition Conditions | Precisely control all deposition parameters. For spin coating, ensure consistent spin speed and time. <a href="#">[10]</a> For drop casting, control the drop volume, substrate temperature, and tilt angle.<br><a href="#">[16]</a> For bar coating, maintain a constant coating speed. <a href="#">[9]</a>                |

| Presence of Grain Boundaries   | Grain boundaries act as barriers to charge transport. Optimize annealing conditions (temperature and time) to promote grain growth and reduce the density of grain boundaries. An in situ annealing treatment at 60°C during deposition has been shown to improve crystallinity and mobility. <a href="#">[12]</a>          |

## Issue 2: Poor Film Quality (Dewetting, Cracks, or Discontinuous Films)

| Potential Cause                 | Recommended Solution                                                                                                                                                                                                                                              |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Surface Energy Mismatch         | The TIPS-pentacene solution is dewetting from the substrate. Ensure the substrate surface is properly treated to have a suitable surface energy. A hydrophobic surface is generally preferred.[6][8]                                                              |

| Rapid Solvent Evaporation       | Fast drying can induce stress in the film, leading to cracks.[16] Use a higher boiling point solvent or slow the evaporation by partially covering the substrate during drying.[5][16]                                                                            |

| Excessive Annealing Temperature | Annealing at too high a temperature can cause film reorganization and the formation of thermal cracks.[18] Optimize the annealing temperature; for TIPS-pentacene/PS blends, a lower in situ annealing temperature (e.g., 25°C) may yield better results.[18][19] |

| Low Solution Concentration      | If the solution concentration is too low, it may not be sufficient to form a continuous film upon solvent evaporation. Experiment with slightly higher concentrations of TIPS-pentacene.[6]                                                                       |

## Issue 3: Inconsistent Threshold Voltage (V<sub>th</sub>)

| Potential Cause                  | Recommended Solution                                                                                                                                                                                                                                                                                           |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface Trap States            | Trapped charges at the semiconductor-dielectric interface can cause $V_{th}$ shifts. Ensure a high-quality dielectric and use a surface treatment (e.g., OTS) to passivate charge-trapping silanol groups on the $\text{SiO}_2$ surface.[8]                                                                    |

| Moisture or Oxygen Contamination | TIPS-pentacene is relatively stable, but processing should be done in a controlled environment (e.g., a nitrogen-filled glove box) to prevent degradation or doping by atmospheric species, which can affect $V_{th}$ .[9][16]                                                                                 |

| Dielectric Leakage               | A high gate leakage current can make accurate $V_{th}$ extraction difficult.[8] Ensure the dielectric layer is of sufficient thickness and quality to prevent leakage.[20]                                                                                                                                     |

| Post-Annealing Effects           | Annealing can reduce trapped charges and lattice defects, leading to a shift in $V_{th}$ .[12][21] Applying a consistent and optimized annealing protocol is crucial for achieving reproducible threshold voltages. A 60°C in situ anneal has been shown to positively shift $V_{th}$ from -1.7V to -0.9V.[12] |

## Data Presentation: Impact of Fabrication Parameters on Performance

Table 1: Effect of Solvents and Additives on TIPS-Pentacene OFET Mobility

| Solvent/Additive System             | Deposition Method | Reported Mobility (cm <sup>2</sup> /Vs)                             | Key Finding                                                                             |

|-------------------------------------|-------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Chlorobenzene                       | Dual-gate OFET    | Lower than Tetralin                                                 | Solvent choice strongly influences phase segregation and performance.[3]                |

| Tetralin                            | Dual-gate OFET    | Up to 2.82                                                          | High-boiling-point solvent promotes better crystallization. [3][5]                      |

| Trichlorobenzene (in P3HT blend)    | Not Specified     | 5.0 x 10 <sup>-3</sup>                                              | Resulted in the best morphology and highest output current in the blend.[5]             |

| Toluene (Pristine)                  | FET               | 0.10                                                                | Baseline performance without additives.[11]                                             |

| Toluene with Diphenyl Ether (DPE)   | FET               | 0.73                                                                | Additives induce well-ordered domains, enhancing mobility. [11]                         |

| Toluene with Chloronaphthalene (CN) | FET               | 0.71                                                                | Similar enhancement effect to DPE.[11]                                                  |

| O-xylene                            | OTFT              | Not specified, but 58x higher sensor sensitivity than Chlorobenzene | Optimal for balancing crystallinity and grain boundaries for sensing applications. [14] |

Table 2: Effect of Annealing on TIPS-Pentacene OFET Performance

| Annealing Method             | Substrate Temp. | Mobility (cm <sup>2</sup> /Vs) | Threshold Voltage (V <sub>th</sub> ) | Key Finding                                                                                                                                           |

|------------------------------|-----------------|--------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Post-annealing               | Ambient         | 0.056                          | -1.7                                 | Conventional method used as a baseline. <a href="#">[12]</a>                                                                                          |

| In situ annealing            | 60 °C           | 0.191                          | -0.9                                 | In situ treatment at an optimal temperature significantly improves crystallinity and performance. <a href="#">[12]</a>                                |

| In situ annealing (in blend) | 25 °C           | 0.14                           | 0.14                                 | Lower temperature annealing can be optimal for polymer blends, minimizing thermal cracks and hysteresis.<br><a href="#">[18]</a> <a href="#">[19]</a> |

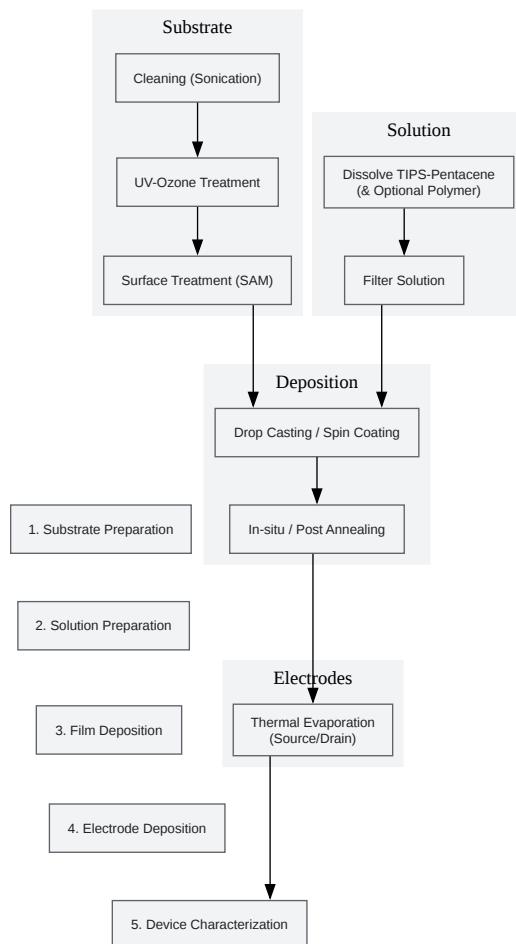

## Experimental Protocols

### Protocol 1: Substrate Cleaning and Surface Treatment

- Initial Cleaning: Sonicate substrates sequentially in a 1% Hellmanex III solution, deionized (DI) water, and isopropyl alcohol (IPA), each for 5-10 minutes in a hot water bath.[\[16\]](#)

- Rinsing: Rinse the substrates thoroughly with DI water after each sonication step.[\[16\]](#)

- Drying & Activation: Dry the substrates with a nitrogen gun and perform a UV-Ozone treatment for 5 minutes to remove organic residues and activate the surface.[\[16\]](#)

- Silane Treatment (PTS): Immediately transfer substrates to a nitrogen-filled glove box. Prepare a 3% weight solution of trichloro(phenyl)silane (PTS) in anhydrous toluene. Immerse

the substrates in the solution at 90°C for 15 hours.[16]

- Post-Treatment Rinsing: Rinse the treated substrates twice with fresh anhydrous toluene inside the glove box.[16]

- Final Bake: Dry the substrates and bake them on a hotplate at 150°C for 5 minutes to remove any residual solvent before use.[16]

## Protocol 2: TIPS-Pentacene Solution Preparation (with PS blend)

- Environment: Perform all solution preparation steps in an inert atmosphere (e.g., nitrogen glove box) to prevent material degradation.[9][16]

- Stock Solutions: Prepare individual stock solutions of TIPS-pentacene and polystyrene (PS) in anhydrous toluene (e.g., at a concentration of 10 mg/mL).[16][17]

- Dissolution: Stir each solution on a hotplate at 60°C for 30-60 minutes to ensure complete dissolution.[16][17]

- Filtering: Filter each solution while warm using a 0.2 µm PTFE syringe filter to remove any particulate impurities.[9][17]

- Blending: Combine the filtered stock solutions to achieve the desired weight percentage of TIPS-pentacene to PS (e.g., a 40 wt% TIPS-pentacene ratio has shown high mobility).[9] Mix the final blend solution thoroughly.

## Protocol 3: Film Deposition by Drop Casting

- Substrate Setup: Place the cleaned and surface-treated substrate on a hotplate inside a petri dish. To control crystal orientation, the substrate can be tilted at a slight angle (~3.5-5°).[13][16]

- Heating: Heat the substrate to the desired deposition temperature (e.g., 50-60°C).[16]

- Deposition: Using a pipette, dispense a fixed volume (e.g., 50 µL for a 2 mg/mL solution) of the TIPS-pentacene solution onto the heated substrate.[16]

- Controlled Evaporation: Immediately cover the petri dish with its lid. This traps solvent vapor, creating a solvent-saturated environment that slows down crystallization, promoting the growth of larger, more ordered crystals.[16]

- Cooling: After a few minutes (e.g., 5 minutes), switch off the hotplate and allow the substrate to cool to room temperature slowly before removing it for subsequent processing steps.[16]

## Visualizations

[Click to download full resolution via product page](#)

Caption: General experimental workflow for TIPS-pentacene OFET fabrication.

[Click to download full resolution via product page](#)

Caption: Troubleshooting flowchart for diagnosing sources of device variation.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. researchgate.net [researchgate.net]

- 2. pure.psu.edu [pure.psu.edu]

- 3. Solvent and polymer matrix effects on TIPS-pentacene/polymer blend organic field-effect transistors - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. pubs.aip.org [pubs.aip.org]

- 7. researchgate.net [researchgate.net]

- 8. pubs.aip.org [pubs.aip.org]

- 9. Engineered molecular stacking crystallinity of bar-coated TIPS-pentacene/polystyrene films for organic thin-film transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 10. researchgate.net [researchgate.net]

- 11. Improved performance in TIPS-pentacene field effect transistors using solvent additives - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 12. Effect of In Situ Annealing Treatment on the Mobility and Morphology of TIPS-Pentacene-Based Organic Field-Effect Transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 13. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance - PMC [pmc.ncbi.nlm.nih.gov]

- 14. researchgate.net [researchgate.net]

- 15. researchgate.net [researchgate.net]

- 16. ossila.com [ossila.com]

- 17. pubs.rsc.org [pubs.rsc.org]

- 18. pubs.rsc.org [pubs.rsc.org]

- 19. A no-hysteresis TIPS–pentacene:polystyrene blend-based organic field effect transistor by extruded direct ink writing and the application in a resistive load inverter circuit - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 20. researchgate.net [researchgate.net]

- 21. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Minimizing device-to-device variation in TIPS-pentacene OFETs]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b153593#minimizing-device-to-device-variation-in-tips-pentacene-ofets>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)