# Improving charge carrier mobility in acenaphthylene-based semiconductor materials

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Acenaphthyleneoctol**

Cat. No.: **B15176596**

[Get Quote](#)

## Technical Support Center: Acenaphthylene-Based Semiconductor Materials

Welcome to the technical support center for acenaphthylene-based semiconductor materials. This resource is designed to assist researchers, scientists, and drug development professionals in optimizing their experiments and troubleshooting common issues encountered when working with this promising class of organic semiconductors.

## Frequently Asked Questions (FAQs)

**Q1:** What makes acenaphthylene-based materials promising for semiconductor applications?

**A1:** Acenaphthylene possesses a unique polycyclic aromatic hydrocarbon structure with an ethylene bridge, which provides a platform for creating extended  $\pi$ -conjugated systems. This structure can impart desirable electronic and optical properties, and its non-alternant electronic nature can increase electron affinity, making these materials suitable for electron-transporting or donor-acceptor systems in devices like organic field-effect transistors (OFETs), organic photovoltaics (OPVs), and organic light-emitting diodes (OLEDs).

**Q2:** What are the typical charge carrier mobility values for acenaphthylene-based materials?

**A2:** The charge carrier mobility of acenaphthylene-based materials can vary significantly depending on the specific molecular structure, purity, thin-film morphology, and device

architecture. Reported values range from  $10^{-5}$  cm $^2$ /Vs to over 0.2 cm $^2$ /Vs. For instance, certain acenaphtho[1,2-b]quinoxaline-based copolymers have shown hole mobilities in the range of  $10^{-5}$  to  $10^{-3}$  cm $^2$ /Vs, while some naphthodithieno[3,2-b]thiophene (NDTT) derivatives have achieved mobilities as high as 0.22 cm $^2$ /Vs after thermal annealing.[\[1\]](#) An acenaphthylene imide-based copolymer, referred to as P4, has demonstrated an electron mobility of 0.08 cm $^2$ /Vs.

**Q3:** How can I improve the charge carrier mobility of my acenaphthylene-based semiconductor?

**A3:** Improving charge carrier mobility in organic semiconductors is a multi-faceted challenge that involves optimizing molecular design, controlling the thin-film morphology, and careful device engineering. Key strategies include:

- **Molecular Design:** Modifying the molecular structure by adding electron-donating or electron-withdrawing groups can tune the frontier molecular orbital energy levels (HOMO/LUMO) and influence intermolecular packing.

- **Purification:** High purity of the semiconductor material is crucial to minimize charge trapping at impurity sites.

- **Thin-Film Deposition:** The choice of deposition technique (e.g., spin-coating, vacuum evaporation) and parameters (e.g., solvent, substrate temperature, deposition rate) significantly impacts the crystallinity and molecular ordering of the film.

- **Annealing:** Post-deposition thermal or solvent vapor annealing can promote molecular rearrangement and improve crystallinity, leading to higher mobility.[\[1\]](#)

- **Interface Engineering:** Modifying the dielectric surface with self-assembled monolayers (SAMs) can reduce charge trapping and improve the interface for charge transport.

## Troubleshooting Guides

This section addresses specific issues you may encounter during your experiments with acenaphthylene-based semiconductor materials.

### Low Charge Carrier Mobility

Problem: The measured charge carrier mobility of your OFET device is significantly lower than expected.

| Possible Cause          | Troubleshooting Step                                                                                                                                                                                                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor Film Morphology    | Optimize the deposition parameters. For solution-processed films, experiment with different solvents, solution concentrations, and spin-coating speeds. For vacuum-deposited films, adjust the substrate temperature and deposition rate to promote the growth of larger, more ordered crystalline domains.            |

| Presence of Impurities  | Purify the acenaphthylene-based material using techniques like sublimation, recrystallization, or column chromatography. Ensure all solvents and reagents used in device fabrication are of high purity.                                                                                                               |

| High Density of Traps   | Anneal the device after fabrication. Thermal annealing can help to reduce the number of charge traps by improving the molecular ordering within the film. Solvent vapor annealing is another effective technique to enhance crystallinity.                                                                             |

| High Contact Resistance | Select appropriate source and drain electrode materials with work functions that align with the HOMO or LUMO level of your acenaphthylene-based semiconductor to facilitate efficient charge injection. Consider using an interlayer, such as molybdenum trioxide ( $\text{MoO}_3$ ), to reduce the injection barrier. |

## High OFF Current or Low ON/OFF Ratio

Problem: Your OFET device exhibits a high leakage current when it is supposed to be in the "off" state, resulting in a poor on/off ratio.

| Possible Cause  | Troubleshooting Step                                                                                                                                                                                                                                                                        |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bulk Conduction | Ensure that the semiconductor film is not too thick. A thicker film can lead to significant current flow through the bulk of the material, independent of the gate voltage. Optimize the deposition process to achieve a uniform, thin film.                                                |

| Gate Leakage    | Inspect the quality of your gate dielectric layer. A thin or defective dielectric can lead to a leakage current from the gate to the source/drain electrodes. Consider using a thicker dielectric or a different dielectric material with better insulating properties.                     |

| Impurity Doping | Unintentional doping from atmospheric oxygen or moisture can increase the conductivity of the organic semiconductor, leading to a higher off-current. Fabricate and test your devices in an inert atmosphere (e.g., a nitrogen-filled glovebox) to minimize exposure to ambient conditions. |

## Device Instability

Problem: The performance of your OFET device degrades over time or upon exposure to air.

| Possible Cause                 | Troubleshooting Step                                                                                                                                                                                                                                                                                         |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oxidation or Moisture Trapping | Encapsulate your device to protect the active layer from oxygen and moisture. This can be done using materials like glass, epoxy, or specialized encapsulation films. Perform all fabrication and measurement steps in an inert environment.                                                                 |

| Structural Changes in the Film | Investigate the thermal stability of your material. High operating temperatures or even prolonged storage at room temperature can sometimes lead to morphological changes in the thin film.                                                                                                                  |

| Bias Stress Effects            | The prolonged application of a gate voltage can lead to a shift in the threshold voltage and a decrease in mobility. This is often caused by charge trapping at the semiconductor-dielectric interface. Improving the quality of this interface through surface treatments can mitigate bias stress effects. |

## Quantitative Data Summary

The following table summarizes reported charge carrier mobility values for some acenaphthylene-based semiconductor materials. This data is intended for comparative purposes, and actual results may vary depending on experimental conditions.

| Material                                                         | Deposition Method   | Carrier Type | Mobility (cm <sup>2</sup> /Vs)      | On/Off Ratio | Reference           |

|------------------------------------------------------------------|---------------------|--------------|-------------------------------------|--------------|---------------------|

| Acenaphtho[1,2-b]quinoxaline - oligothiophene copolymers         | Solution Processing | Hole         | 10 <sup>-5</sup> - 10 <sup>-3</sup> | -            | <a href="#">[1]</a> |

| Naphthodithiobenzo[3,2-b]thiophene (NDTT) derivatives (annealed) | Vacuum Evaporation  | Hole         | up to 0.22                          | -            | <a href="#">[1]</a> |

| Acenaphthylene imide-bithiazole copolymer (P4)                   | Solution Processing | Electron     | 0.08                                | -            |                     |

## Experimental Protocols

### General Protocol for Solution-Processed OFET Fabrication

This protocol outlines a general procedure for fabricating a bottom-gate, top-contact (BGTC) organic field-effect transistor using a solution-processable acenaphthylene-based semiconductor.

- Substrate Cleaning:

- Begin with a heavily n-doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (typically 200-300 nm thick), which will serve as the gate electrode and gate dielectric, respectively.

- Clean the substrate sequentially in an ultrasonic bath with deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of nitrogen gas.

- Treat the substrate with an oxygen plasma or a UV-ozone cleaner for 10-15 minutes to remove any remaining organic residues and to create a hydrophilic surface.

- Dielectric Surface Modification (Optional but Recommended):

- To improve the interface between the dielectric and the organic semiconductor, treat the  $\text{SiO}_2$  surface with a self-assembled monolayer (SAM) such as octadecyltrichlorosilane (OTS).

- This can be done by immersing the substrate in a dilute solution of OTS in an anhydrous solvent like toluene or hexane for a specified time, followed by rinsing and annealing.

- Semiconductor Deposition:

- Prepare a solution of the acenaphthylene-based semiconductor in a suitable organic solvent (e.g., chloroform, chlorobenzene, or toluene) at a specific concentration (e.g., 5-10 mg/mL).

- Deposit the semiconductor solution onto the substrate using spin-coating. The spin speed and time will determine the thickness of the film and should be optimized.

- After spin-coating, anneal the film on a hotplate at a specific temperature and for a set duration to remove residual solvent and improve film morphology. The optimal annealing temperature is material-dependent and should be determined experimentally.

- Source and Drain Electrode Deposition:

- Using a shadow mask to define the channel length and width, deposit the source and drain electrodes onto the semiconductor layer via thermal evaporation.

- Gold (Au) is a common choice for p-type semiconductors due to its high work function. For n-type materials, lower work function metals like calcium (Ca) or aluminum (Al), often with a protective capping layer, are used. The thickness of the electrodes is typically 30-50 nm.

- Device Characterization:

- Characterize the electrical performance of the OFET using a semiconductor parameter analyzer in an inert atmosphere (e.g., a probe station inside a glovebox).

- Measure the output characteristics (drain current vs. drain-source voltage at different gate voltages) and transfer characteristics (drain current vs. gate voltage at a fixed drain-source voltage) to extract key parameters like charge carrier mobility, threshold voltage, and on/off ratio.

## Visualizations

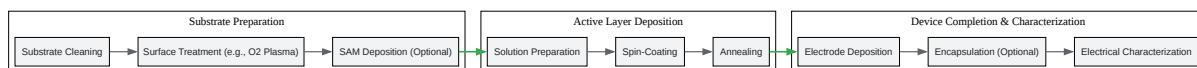

### Experimental Workflow for OFET Fabrication

[Click to download full resolution via product page](#)

Caption: A generalized workflow for the fabrication of a solution-processed organic field-effect transistor (OFET).

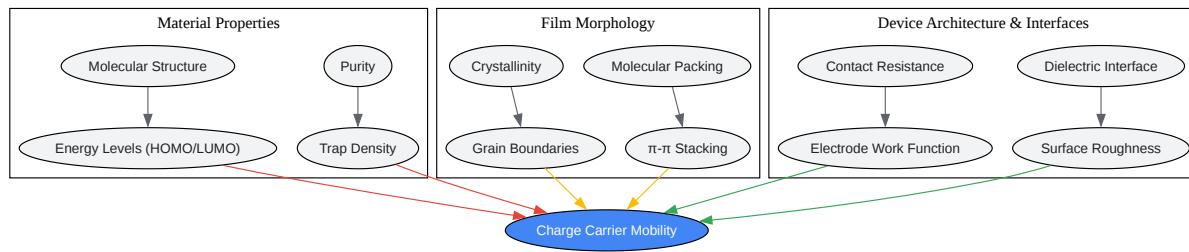

### Factors Influencing Charge Carrier Mobility

[Click to download full resolution via product page](#)

Caption: Key factors influencing charge carrier mobility in organic semiconductor materials.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Acenaphtho[1,2-b]quinoxaline based low band gap copolymers for organic thin film transistor applications - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- To cite this document: BenchChem. [Improving charge carrier mobility in acenaphthylene-based semiconductor materials]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b15176596#improving-charge-carrier-mobility-in-acenaphthylene-based-semiconductor-materials>]

#### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)