# Troubleshooting low on/off ratios in pyromellitic diimide transistors.

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Pyromellitic diimide*

Cat. No.: *B146072*

[Get Quote](#)

## Technical Support Center: Pyromellitic Diimide (PMDI) Transistors

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **pyromellitic diimide** (PMDI)-based transistors. The focus is on addressing the common issue of low on/off ratios in these devices.

## Frequently Asked Questions (FAQs) & Troubleshooting Guide

This section is designed to help you diagnose and resolve common problems encountered during the fabrication and characterization of PMDI transistors that may lead to a low on/off ratio.

**Q1:** My PMDI transistor has a very low on/off ratio. What are the most likely causes?

A low on/off ratio in PMDI transistors is typically a result of a high off-state current ( $I_{off}$ ) or a low on-state current ( $I_{on}$ ), or a combination of both. The primary factors contributing to this include:

- High Off-State Current ( $I_{off}$ ):

- Gate Leakage Current: Significant current flowing through the gate dielectric.

- Bulk Conductivity of the Semiconductor: The intrinsic conductivity of the PMDI film may be too high.

- Interfacial Doping/Traps: Unwanted charge carriers at the semiconductor-dielectric interface.

- Environmental Factors: Contamination from moisture and oxygen can increase off-current.

- Low On-State Current ( $I_{on}$ ):

- High Contact Resistance: Poor injection of charge from the source/drain electrodes into the PMDI semiconductor.

- Charge Trapping: Defects within the semiconductor bulk or at the interfaces can trap charge carriers, reducing mobility.

- Poor Film Morphology: A disordered or non-uniform PMDI thin film can impede efficient charge transport.

Q2: How can I determine if gate leakage is the cause of my high off-current?

To diagnose gate leakage, you should measure the gate current ( $I_g$ ) simultaneously with the drain current ( $I_d$ ) during a transfer characteristic measurement ( $I_d$  vs.  $V_g$ ).

- Symptom: If the gate current is comparable in magnitude to the drain current in the "off" state (i.e., at low gate voltage), then gate leakage is a significant contributor to the high off-current.

- Troubleshooting Steps:

- Inspect the Dielectric: Use atomic force microscopy (AFM) to check for pinholes or defects in the gate dielectric layer.

- Optimize Dielectric Deposition: Ensure your dielectric deposition process (e.g., thermal oxidation for SiO<sub>2</sub>, spin-coating for polymers) is optimized to produce a uniform, pinhole-free layer.

- Increase Dielectric Thickness: A thicker dielectric layer can reduce gate leakage, but this may also decrease the on-current, so a balance must be found.[1][2][3]

- Use a High-k Dielectric: Employing a high-k dielectric material can allow for a physically thicker film while maintaining a high capacitance, which can help suppress leakage current.

Q3: I suspect charge trapping is limiting my on-current and increasing my off-current. How can I confirm and mitigate this?

Charge trapping is a common issue in organic semiconductors. Traps can be present at the semiconductor-dielectric interface or within the bulk of the PMDI film.

- Diagnosis:

- Hysteresis in Transfer Characteristics: A large hysteresis between the forward and reverse sweeps of the gate voltage is a strong indicator of charge trapping.

- Temperature-Dependent I-V Measurements: The mobility of the transistor will show a strong temperature dependence if charge transport is trap-limited.

- Low-Frequency Noise Spectroscopy: This technique can be used to probe the density and energy distribution of trap states.[4][5][6]

- Mitigation Strategies:

- Dielectric Surface Treatment: Treating the dielectric surface with self-assembled monolayers (SAMs) like hexamethyldisilazane (HMDS) or octadecyltrichlorosilane (OTS) can passivate trap states and improve the interface quality.[7][8][9]

- Thermal Annealing: Annealing the PMDI thin film after deposition can improve its crystallinity and reduce the density of bulk traps. The optimal annealing temperature and time must be determined experimentally.

- Solvent Selection and Purity: For solution-processed films, the choice of solvent and the presence of impurities can significantly impact film morphology and introduce traps. Use

high-purity solvents and consider the solvent's boiling point and its interaction with the PMDI material.[\[10\]](#)

Q4: My device has a high off-current even with low gate leakage. What other factors should I investigate?

If gate leakage is ruled out, the high off-current could be due to issues with the semiconductor layer itself or the device architecture.

- Troubleshooting Steps:

- Semiconductor Purity: Ensure the purity of your PMDI material. Impurities can act as dopants, increasing the bulk conductivity.

- Active Area Patterning: In bottom-gate devices without a patterned semiconductor layer, current can flow between the source and drain electrodes outside of the intended channel region, leading to a higher off-current. Patterning the semiconductor layer can help to confine the current path.

- Environmental Control: PMDI-based n-type transistors can be sensitive to moisture and oxygen, which can create trap states or act as dopants.[\[11\]](#) Fabricate and characterize your devices in an inert atmosphere (e.g., a glovebox) to minimize these effects.

Q5: How does the choice of fabrication method (solution processing vs. vacuum deposition) affect the on/off ratio?

Both solution processing and vacuum deposition can yield high-performance PMDI transistors, but they have different considerations for achieving a high on/off ratio.

- Solution Processing (e.g., Spin-coating, Solution Shearing):

- Advantages: Low cost, high throughput, and compatibility with large-area fabrication.

- Challenges: The choice of solvent, solution concentration, and deposition parameters (e.g., spin speed, shearing speed) heavily influence the film morphology and crystallinity. [\[10\]](#)[\[12\]](#)[\[13\]](#)[\[14\]](#)[\[15\]](#) Poor film formation can lead to high trap densities and low mobility. Residual solvent in the film can also act as a source of traps.

- Vacuum Thermal Evaporation:

- Advantages: Produces highly pure and uniform thin films with good control over thickness.

- Challenges: The substrate temperature during deposition is a critical parameter.[16][17] [18] An optimized substrate temperature can promote the growth of a well-ordered film with large crystalline domains, leading to higher mobility and a better on/off ratio.[19][20]

## Quantitative Data Summary

The following tables summarize key performance parameters for PMDI-based transistors under different fabrication and treatment conditions.

Table 1: Performance of PMDI Derivatives in n-Channel OFETs

| PMDI Derivative            | Deposition Method  | Substrate Temperature (°C) | Electron Mobility (cm²/Vs)       | On/Off Ratio                     | Reference |

|----------------------------|--------------------|----------------------------|----------------------------------|----------------------------------|-----------|

| PyDI-BOCF3                 | Vacuum Evaporation | 70                         | 0.058                            | > 10 <sup>5</sup>                | [19][20]  |

| PyDI-BSCF3                 | Vacuum Evaporation | 70                         | 0.09                             | > 10 <sup>5</sup>                | [19][20]  |

| PB-PyDI                    | Spin-coating       | RT                         | Modest                           | -                                | [12][13]  |

| PB-PyDI:PCBM (1:9)         | Spin-coating       | RT                         | $3 \times 10^{-3}$               | 1000                             | [12][13]  |

| Fluorinated PyDI           | -                  | -                          | up to 0.079                      | 10 <sup>6</sup>                  | [21]      |

| Thionated/Fluorinated PyDI | -                  | -                          | Two orders of magnitude increase | Two orders of magnitude increase | [11]      |

## Experimental Protocols

This section provides detailed methodologies for key experiments relevant to troubleshooting low on/off ratios in PMDI transistors.

#### Protocol 1: Fabrication of a Top-Contact, Bottom-Gate PMDI Transistor

- Substrate Cleaning:

- Begin with a heavily n-doped silicon wafer with a 300 nm thermally grown  $\text{SiO}_2$  layer, which will serve as the gate and gate dielectric, respectively.

- Sonicate the substrate sequentially in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of nitrogen gas.

- Treat the substrate with UV-ozone for 15 minutes to remove any organic residues and to create a hydrophilic surface.

- Dielectric Surface Treatment (Optional but Recommended):

- For an HMDS treatment, place the substrate in a vacuum desiccator with a few drops of HMDS in a small container. Evacuate the desiccator and leave for 12 hours.

- For an OTS treatment, prepare a 10 mM solution of OTS in anhydrous toluene. Immerse the substrate in the solution for 30 minutes in a nitrogen-filled glovebox. Rinse with fresh toluene and anneal at 120°C for 1 hour.

- PMDI Deposition:

- By Vacuum Evaporation: Place the substrate and the PMDI source material in a thermal evaporator. Evacuate the chamber to a pressure below  $10^{-6}$  Torr. Heat the substrate to the desired temperature (e.g., 70°C). Evaporate the PMDI at a rate of 0.1-0.2 Å/s to a final thickness of 30-50 nm.

- By Spin-Coating: Prepare a solution of the PMDI-based polymer in a suitable solvent (e.g., chloroform, chlorobenzene) at a concentration of 5-10 mg/mL.[\[12\]](#)[\[13\]](#) Spin-coat the solution onto the substrate at 3000 rpm for 60 seconds.

- Thermal Annealing:

- Transfer the substrate with the deposited PMDI film to a hotplate in a nitrogen-filled glovebox.

- Anneal the film at a temperature optimized for the specific PMDI derivative (e.g., 100-150°C) for 30-60 minutes.

- Allow the film to cool down slowly to room temperature.

- Electrode Deposition:

- Using a shadow mask, thermally evaporate 50 nm of gold (or another suitable electrode material like silver or calcium) for the source and drain electrodes at a pressure below  $10^{-6}$  Torr. The channel length and width are defined by the shadow mask.

#### Protocol 2: Measurement of Transistor On/Off Ratio

- Setup: Place the fabricated transistor on the probe station of a semiconductor parameter analyzer in a dark, electrically shielded box.

- Connections: Connect the probes to the source, drain, and gate electrodes.

- Transfer Curve Measurement:

- Apply a constant drain-source voltage ( $V_{ds}$ ), typically in the saturation regime (e.g., 60 V).

- Sweep the gate-source voltage ( $V_{gs}$ ) from a negative value (e.g., -20 V) to a positive value (e.g., 80 V) and then back to the negative value to check for hysteresis.

- Record the drain current ( $I_d$ ) and the gate current ( $I_g$ ) at each  $V_{gs}$  step.

- On/Off Ratio Calculation:

- The "on" current ( $I_{on}$ ) is the maximum drain current measured at the highest positive gate voltage.

- The "off" current ( $I_{off}$ ) is the minimum drain current measured, typically at zero or a negative gate voltage.

- The on/off ratio is calculated as  $I_{on} / I_{off}$ .

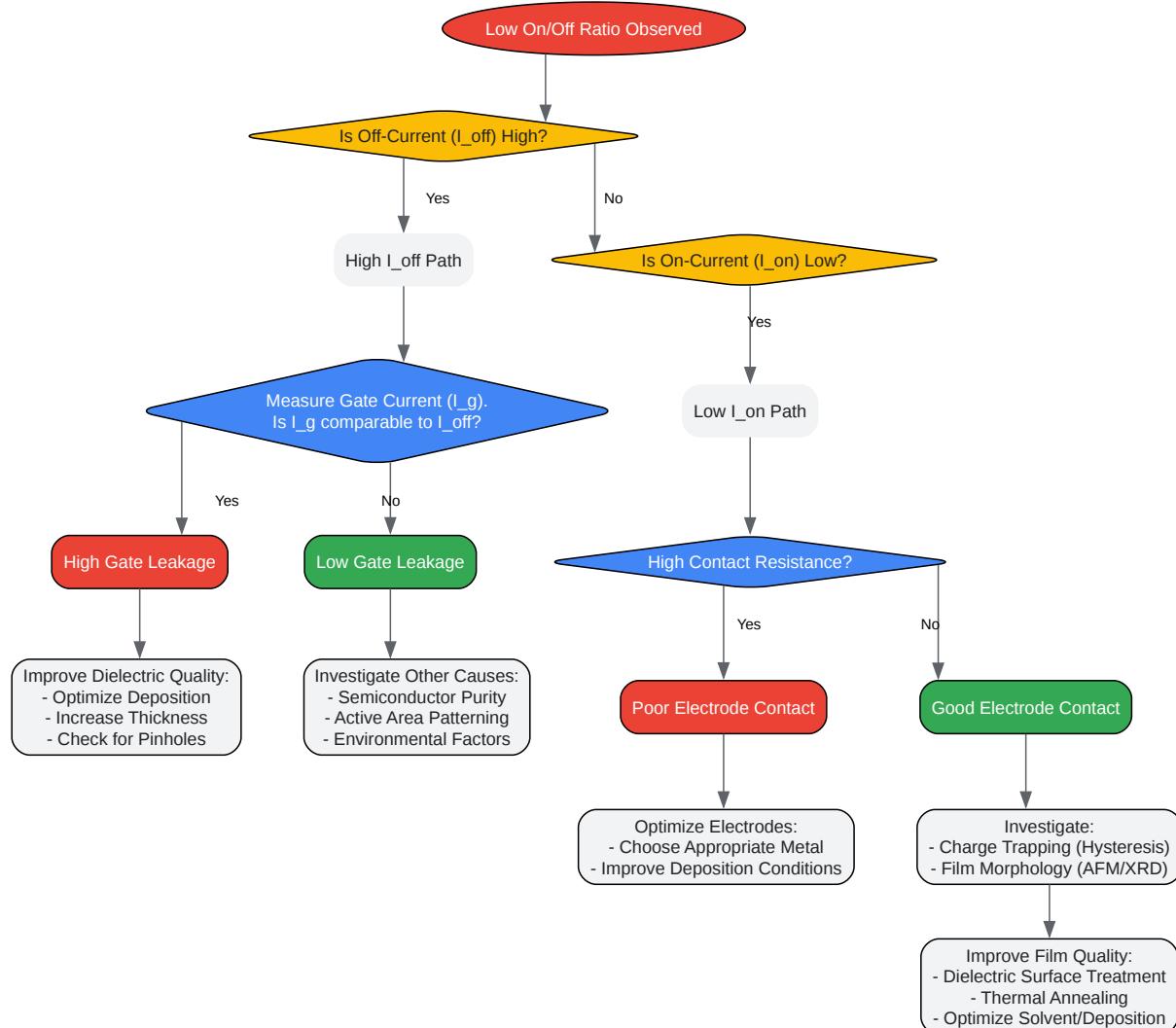

## Mandatory Visualizations

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for low on/off ratios in PMDI transistors.

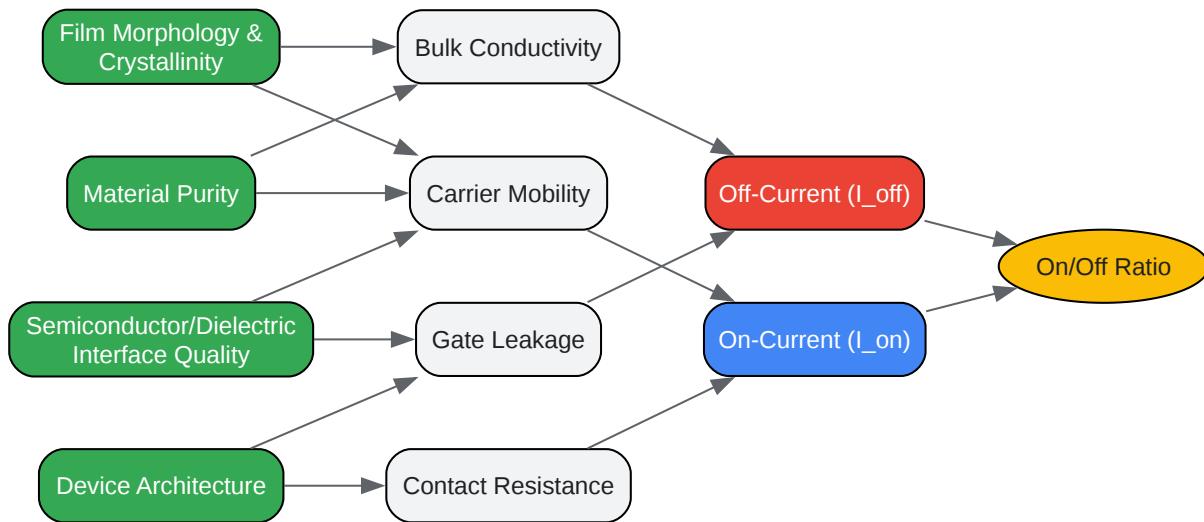

[Click to download full resolution via product page](#)

Caption: Key factors influencing the on/off ratio in PMDI transistors.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. matec-conferences.org [matec-conferences.org]

- 2. researchgate.net [researchgate.net]

- 3. web.stanford.edu [web.stanford.edu]

- 4. Low-frequency noise spectroscopy of polycrystalline silicon thin-film transistors | Semantic Scholar [semanticscholar.org]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- 11. Pyromellitic dithioimides: thionation improves air-stability and electron mobility of N-type organic field-effect transistors - Chemical Communications (RSC Publishing) [pubs.rsc.org]

- 12. Synthesis and Characterization of a Pyromellitic Diimide-Based Polymer with C- and N-Main Chain links: Matrix for Solution-Processable n-Channel Field-effect Transistors - PubMed [pubmed.ncbi.nlm.nih.gov]

- 13. Synthesis and Characterization of a Pyromellitic Diimide-Based Polymer with C- and N-Main Chain links: Matrix for Solution-Processable n-Channel Field-effect Transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 14. Interfacial effects on solution-sheared thin-film transistors - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 15. researchgate.net [researchgate.net]

- 16. chalcogen.ro [chalcogen.ro]

- 17. mdpi.com [mdpi.com]

- 18. azom.com [azom.com]

- 19. researchgate.net [researchgate.net]

- 20. Wide band gap pyromellitic diimides for photo stable n-channel thin film transistors - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 21. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Troubleshooting low on/off ratios in pyromellitic diimide transistors.]. BenchChem, [2025]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b146072#troubleshooting-low-on-off-ratios-in-pyromellitic-diimide-transistors\]](https://www.benchchem.com/product/b146072#troubleshooting-low-on-off-ratios-in-pyromellitic-diimide-transistors)

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)