# Technical Support Center: Stabilizing Acenaphthylene-Based Organic Semiconductors

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Acenaphthylene**

Cat. No.: **B141429**

[Get Quote](#)

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the synthesis, fabrication, and characterization of **acenaphthylene**-based organic semiconductors.

## Frequently Asked Questions (FAQs)

**Q1:** What are the primary advantages of using **acenaphthylene** as a building block for organic semiconductors?

**Acenaphthylene** offers a unique combination of a fused ring system and a reactive ethylene bridge, which allows for the construction of extended  $\pi$ -conjugated systems. This structure can impart desirable electronic and optical properties, including increased electron affinity, making **acenaphthylene**-based materials promising candidates for electron-transporting or ambipolar semiconductors in various organic electronic devices.<sup>[1]</sup>

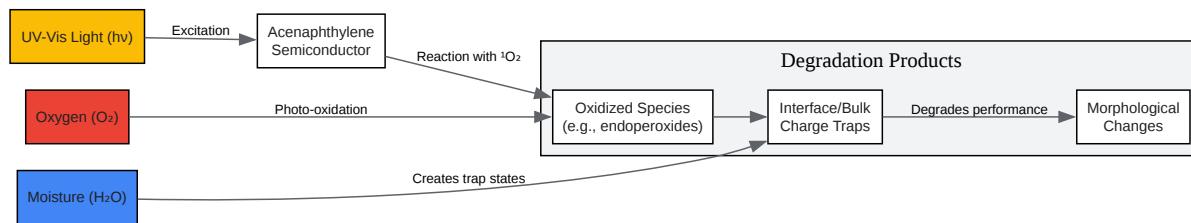

**Q2:** What are the main stability concerns for **acenaphthylene**-based organic semiconductors?

Like many organic semiconductors, **acenaphthylene** derivatives can be susceptible to degradation in the presence of oxygen, moisture, and light (photodegradation).<sup>[1]</sup> The open-shell diradical character that can be induced in some **acenaphthylene**-fused systems, while electronically interesting, can also lead to high reactivity and instability if not properly managed through molecular design.<sup>[2][3]</sup>

Q3: How can the stability of **acenaphthylene**-based semiconductors be improved through molecular design?

Strategic chemical modifications can significantly enhance stability. Fusion of **acenaphthylene** units onto larger polycyclic aromatic hydrocarbons can create stable diradicaloids with good ambient stability.<sup>[2][3]</sup> Additionally, the introduction of specific functional groups can modulate the HOMO/LUMO energy levels, which plays a critical role in air stability. For instance, lowering the LUMO energy level through fluorination has been shown to improve the air stability of n-channel organic semiconductors.<sup>[4][5]</sup>

Q4: What are common impurities in **acenaphthylene**-based semiconductors and how can they be removed?

Common impurities can include unreacted starting materials, byproducts from side reactions, and residual catalysts (e.g., palladium from cross-coupling reactions). Purification is critical for achieving optimal device performance. Standard purification techniques include column chromatography, recrystallization, and sublimation. For high-purity materials required for electronic applications, multiple purification steps are often necessary. Techniques like high-speed counter-current chromatography can also be effective for separating complex mixtures.<sup>[6][7]</sup>

## Troubleshooting Guides

This section provides solutions to common problems encountered during the experimental workflow with **acenaphthylene**-based organic semiconductors.

## Synthesis and Purification Issues

| Problem                              | Possible Causes                                                                                                                                                                                          | Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low reaction yield                   | <ul style="list-style-type: none"><li>- Incomplete reaction.</li><li>- Side reactions consuming starting materials.</li><li>- Suboptimal reaction conditions (temperature, catalyst, solvent).</li></ul> | <ul style="list-style-type: none"><li>- Monitor reaction progress using TLC or GC-MS to determine the optimal reaction time.</li><li>- Use high-purity, anhydrous solvents and reagents.</li><li>- Optimize reaction temperature, catalyst loading, and ligand choice.</li></ul>                                                                                              |

| Difficult purification               | <ul style="list-style-type: none"><li>- Presence of closely related byproducts with similar polarity.</li><li>- Contamination with residual metal catalysts.</li></ul>                                   | <ul style="list-style-type: none"><li>- Employ multi-step purification: column chromatography followed by recrystallization or sublimation.</li><li>- Use specialized chromatography techniques like preparative HPLC or HSCCC for difficult separations.<sup>[7]</sup></li><li>- Treat the crude product with a scavenger resin to remove metal catalyst residues.</li></ul> |

| Material instability after synthesis | <ul style="list-style-type: none"><li>- Residual acid or base from the workup.</li><li>- Exposure to air and light.</li></ul>                                                                            | <ul style="list-style-type: none"><li>- Ensure thorough washing and neutralization during the workup process.</li><li>- Store the purified material under an inert atmosphere (nitrogen or argon) and in the dark.</li></ul>                                                                                                                                                  |

## Thin-Film Deposition and Device Fabrication Issues

| Problem                                             | Possible Causes                                                                                                                                                                         | Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor film quality (pinholes, voids, high roughness) | <ul style="list-style-type: none"><li>- Inappropriate solvent or deposition technique.</li><li>- Contaminated substrate.</li><li>- Inconsistent deposition temperature.</li></ul>       | <ul style="list-style-type: none"><li>- Optimize the solvent system for your specific acenaphthylene derivative to control solubility and evaporation rate.</li><li>- Experiment with different deposition techniques (e.g., spin-coating, solution-shearing, vacuum deposition).</li><li>- Implement a rigorous substrate cleaning protocol (e.g., sonication in solvents, UV-ozone treatment).</li></ul> <p>[8] - For vacuum deposition, optimize the substrate temperature to enhance adatom mobility and promote denser film growth.[9]</p> |

| Poor film adhesion                                  | <ul style="list-style-type: none"><li>- Surface energy mismatch between the substrate and the organic semiconductor.</li><li>- Moisture on the substrate surface.</li></ul>             | <ul style="list-style-type: none"><li>- Treat the substrate with a self-assembled monolayer (SAM) to modify its surface energy.</li><li>- Perform an in-situ pre-deposition heating of the substrate in a vacuum to remove adsorbed moisture.</li></ul> <p>[10]</p>                                                                                                                                                                                                                                                                             |

| Inconsistent device performance                     | <ul style="list-style-type: none"><li>- Variations in thin-film morphology and molecular packing.</li><li>- High contact resistance.</li><li>- Unstable dielectric interface.</li></ul> | <ul style="list-style-type: none"><li>- Precisely control the deposition parameters (e.g., solution concentration, deposition speed, substrate temperature) to ensure reproducible film morphology.</li></ul> <p>[11] - See the "High Contact Resistance" section below for specific troubleshooting.</p> <p>- See the "Unstable Threshold</p>                                                                                                                                                                                                  |

---

Voltage / High Hysteresis" section below for specific troubleshooting.

---

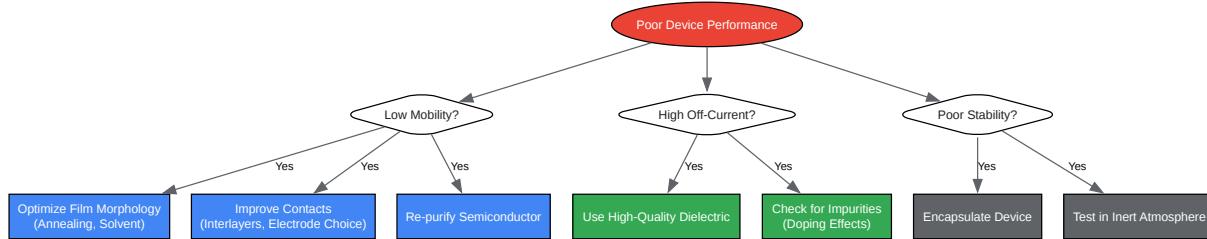

## Device Performance and Stability Issues

| Problem                                            | Possible Causes                                                                                                                                                                                                                              | Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low charge carrier mobility                        | <ul style="list-style-type: none"><li>- Disordered molecular packing in the thin film.[11][12]</li><li>- Presence of traps at the semiconductor/dielectric interface.</li><li>- High contact resistance.</li></ul>                           | <ul style="list-style-type: none"><li>- Optimize film deposition conditions (e.g., solvent, annealing temperature) to promote crystalline domains and favorable molecular packing.</li><li>- Treat the dielectric surface with a suitable SAM to reduce trap states.</li><li>- See the "High Contact Resistance" section below.</li></ul>                                                                                                    |

| High contact resistance                            | <ul style="list-style-type: none"><li>- Energy level mismatch between the semiconductor's HOMO/LUMO and the electrode work function.</li><li>- Poor physical contact at the electrode-semiconductor interface.</li></ul>                     | <ul style="list-style-type: none"><li>- Select electrode materials with appropriate work functions.</li><li>- Introduce a thin interlayer (e.g., <math>\text{MoO}_x</math> for p-type, or a low work function metal for n-type) between the electrode and the semiconductor to facilitate charge injection.[13][14]</li><li>- Optimize the deposition of the top contact electrodes to prevent penetration into the organic layer.</li></ul> |

| Unstable threshold voltage / high hysteresis       | <ul style="list-style-type: none"><li>- Charge trapping at the semiconductor/dielectric interface or within the dielectric.[15]</li><li>- Mobile ions in the dielectric layer.</li><li>- Environmental effects (moisture, oxygen).</li></ul> | <ul style="list-style-type: none"><li>- Choose a high-quality gate dielectric with a low density of trap states.</li><li>- Encapsulate the device to protect it from ambient conditions.</li><li>- Perform measurements in an inert atmosphere (glovebox) or vacuum.</li></ul>                                                                                                                                                               |

| Device degradation under operation or illumination | <ul style="list-style-type: none"><li>- Photodegradation of the acenaphthylene-based</li></ul>                                                                                                                                               | <ul style="list-style-type: none"><li>- Encapsulate the device with UV-blocking layers.</li><li>- Synthesize more</li></ul>                                                                                                                                                                                                                                                                                                                  |

material. - Electrochemical instability under bias stress. photochemically stable derivatives, for example by creating a donor-acceptor architecture or incorporating them into a polymer matrix. - Operate the device within a stable voltage window.

## Data Presentation

Table 1: Comparison of Representative **Acenaphthylene**-Based Organic Semiconductor Performance in OFETs

| Acenaphthylene Derivative                | Deposition Method | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio      | Stability Notes                                                               |

|------------------------------------------|-------------------|--------------------------------|-------------------|-------------------------------------------------------------------------------|

| Di-tert-butyl-acenaphtho[1,2-b]thiophene | Vacuum Deposition | 0.1 - 0.5                      | > 10 <sup>6</sup> | Moderate air stability, encapsulation recommended.                            |

| Acenaphtho[1,2-k]fluoranthene derivative | Solution Shearing | 0.5 - 1.2                      | > 10 <sup>7</sup> | Good solution processability, improved stability with specific side chains.   |

| Fused Acenaphthylene Diradicaloid        | Vacuum Deposition | 0.01 - 0.1                     | > 10 <sup>5</sup> | Excellent ambient and photostability. <a href="#">[2]</a> <a href="#">[3]</a> |

| Polymer with Acenaphthylene co-monomer   | Spin Coating      | 0.05 - 0.2                     | > 10 <sup>6</sup> | Good film-forming properties and enhanced operational stability.              |

Note: The values presented are representative and can vary significantly based on device architecture, processing conditions, and measurement environment.

## Experimental Protocols

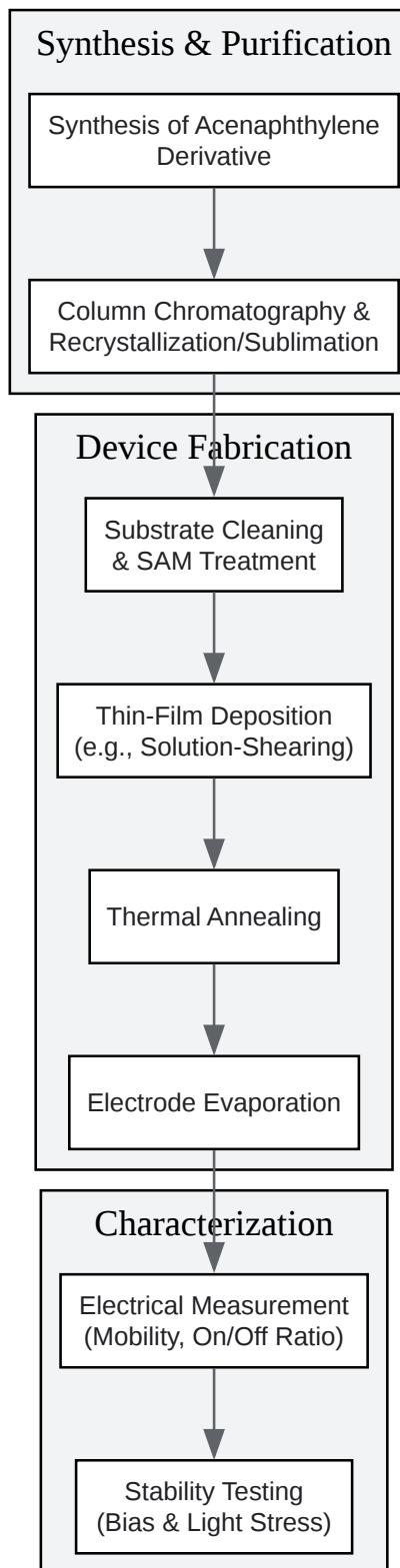

### Synthesis of an Air-Stable Acenaphthylene-Fused Heterocycle

This protocol describes a general approach for synthesizing a more stable **acenaphthylene** derivative by incorporating a thiophene ring, which can enhance molecular packing and stability.

- Starting Materials: Acenaphthenequinone, Lawesson's reagent, and a suitable aromatic coupling partner (e.g., a boronic acid derivative for Suzuki coupling).

- Thionation of Acenaphthenequinone:

- In a flame-dried flask under an inert atmosphere (Argon), dissolve acenaphthenequinone and Lawesson's reagent in anhydrous toluene.

- Reflux the mixture for 4-6 hours, monitoring the reaction by TLC.

- After completion, cool the reaction mixture and remove the solvent under reduced pressure.

- Purify the crude product by column chromatography on silica gel to obtain the thionated intermediate.

- Cross-Coupling Reaction (e.g., Suzuki Coupling):

- To a solution of the thionated intermediate and the boronic acid derivative in a 2:1 mixture of toluene and water, add a palladium catalyst (e.g.,  $\text{Pd}(\text{PPh}_3)_4$ ) and a base (e.g.,  $\text{K}_2\text{CO}_3$ ).

- Degas the mixture and heat under reflux for 12-24 hours.

- After cooling, perform a liquid-liquid extraction with an organic solvent (e.g., ethyl acetate).

- Wash the combined organic layers with brine, dry over anhydrous MgSO<sub>4</sub>, and concentrate under reduced pressure.

- Purification:

- Purify the crude product by column chromatography.

- For higher purity, perform recrystallization from a suitable solvent system or vacuum sublimation.

## Fabrication of a Bottom-Gate, Top-Contact (BGTC) OFET

- Substrate Cleaning:

- Use heavily n-doped silicon wafers with a thermally grown SiO<sub>2</sub> layer (300 nm) as the substrate (Si serves as the gate electrode, SiO<sub>2</sub> as the gate dielectric).

- Sequentially sonicate the substrates in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of nitrogen gas.

- Treat the substrates with UV-ozone for 10 minutes to remove organic residues and improve the surface hydrophilicity.

- Dielectric Surface Treatment:

- (Optional but recommended) Immerse the cleaned substrates in a solution of a self-assembled monolayer (SAM) such as octadecyltrichlorosilane (OTS) in anhydrous toluene for 1 hour to create a hydrophobic surface, which can improve the molecular ordering of the semiconductor.

- Rinse the substrates with fresh toluene and anneal at 120°C for 30 minutes.

- Semiconductor Deposition (Solution-Shearing):

- Prepare a solution of the **acenaphthylene**-based semiconductor in a high-boiling point solvent (e.g., chlorobenzene, dichlorobenzene) at a concentration of 5-10 mg/mL.

- Heat the substrate to a specific temperature (e.g., 80-120°C) on a motorized stage.

- Dispense a small volume of the semiconductor solution onto the substrate in front of a blade held at a fixed angle and gap.

- Move the stage at a constant, slow speed (e.g., 0.1-1 mm/s) to deposit a uniform thin film.

- Annealing:

- Transfer the coated substrate to a hotplate in a nitrogen-filled glovebox and anneal at a temperature just below the material's melting point for 30-60 minutes to improve crystallinity.

- Electrode Deposition:

- Define the source and drain electrodes using a shadow mask with the desired channel length and width.

- Thermally evaporate a 50 nm layer of gold (Au) through the shadow mask at a high vacuum ( $< 10^{-6}$  Torr). A thin adhesion layer of chromium (Cr) or titanium (Ti) (5 nm) may be deposited before the gold.

- Characterization:

- Perform electrical characterization of the OFETs in a nitrogen glovebox or a vacuum probe station using a semiconductor parameter analyzer.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Degradation pathway of **acenaphthylene**-based semiconductors.

[Click to download full resolution via product page](#)

Caption: Experimental workflow for OFET fabrication.

[Click to download full resolution via product page](#)

Caption: Troubleshooting logical relationships for OFETs.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. researchgate.net [researchgate.net]

- 2. chinesechemsoc.org [chinesechemsoc.org]

- 3. chinesechemsoc.org [chinesechemsoc.org]

- 4. pubs.acs.org [pubs.acs.org]

- 5. Anthracenedicarboximide-based semiconductors for air-stable, n-channel organic thin-film transistors: materials design, synthesis, and structural characterization - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 6. bibliotekanauki.pl [bibliotekanauki.pl]

- 7. researchgate.net [researchgate.net]

- 8. 5 Challenges in Thin Film Manufacturing and How to Overcome Them - Denton Vacuum [dentonvacuum.com]

- 9. Top 5 Thin Film Deposition Challenges and Expert Solutions for High-Yield Processes [xk-sputteringtarget.com]

- 10. researchgate.net [researchgate.net]

- 11. Molecular Packing: Another Key Point for the Performance of Organic and Polymeric Optoelectronic Materials - PubMed [pubmed.ncbi.nlm.nih.gov]

- 12. pubs.aip.org [pubs.aip.org]

- 13. researchgate.net [researchgate.net]

- 14. pubs.acs.org [pubs.acs.org]

- 15. Enhancement of Stability in n-Channel OFETs by Modulating Polymeric Dielectric [mdpi.com]

- To cite this document: BenchChem. [Technical Support Center: Stabilizing Acenaphthylene-Based Organic Semiconductors]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b141429#stabilizing-acenaphthylene-based-organic-semiconductors>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)