# Technical Support Center: 2,6-Diphenylanthracene (DPA) Transistors

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## Compound of Interest

Compound Name: 2,6-Diphenylanthracene

Cat. No.: B1340685

[Get Quote](#)

Welcome to the technical support center for researchers working with **2,6-Diphenylanthracene (DPA)** organic field-effect transistors (OFETs). This guide is designed to provide practical, in-depth solutions to common challenges encountered during device fabrication and characterization, with a specific focus on the critical issue of contact resistance ( $R_c$ ). High contact resistance is a primary bottleneck that can obscure the intrinsic properties of high-performance materials like DPA, leading to underestimated mobility and limited device speed.

[1][2][3]

This resource combines troubleshooting advice in a direct question-and-answer format with foundational knowledge to empower you to diagnose issues, optimize your experimental protocols, and achieve high-performance, reliable devices.

## Troubleshooting Guide: Diagnosing and Solving Common Issues

This section addresses specific problems you might be observing in your experimental results. Each answer provides a causal explanation and a step-by-step protocol for resolution.

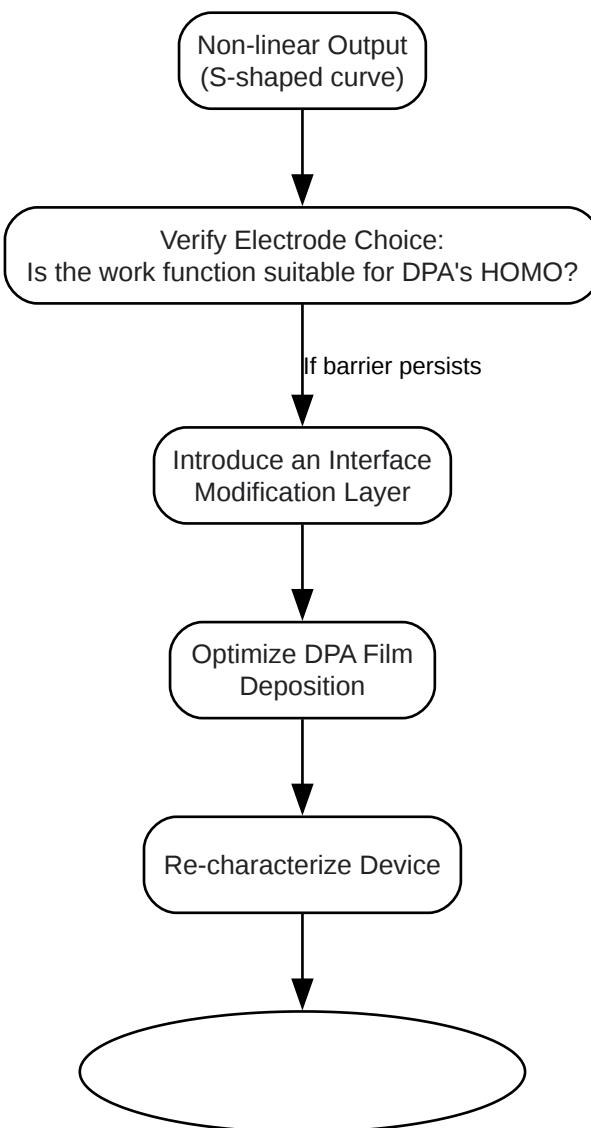

### Question 1: My output characteristics (ID vs. VD) are non-linear or "S-shaped" at low drain voltages, even at high gate voltage. What is causing this?

Answer:

This is a classic symptom of a significant charge injection barrier, often called a Schottky barrier, at the source electrode/DPA interface.<sup>[4]</sup> Instead of a smooth, "Ohmic" contact where charge injection is efficient, this barrier impedes the flow of holes from the electrode into the DPA semiconductor. This effect is most pronounced at low drain-source voltages (VD) where the electric field is not strong enough to overcome the barrier efficiently.

Causality: The primary cause is a misalignment between the work function of your source electrode metal (e.g., Gold, Au) and the Highest Occupied Molecular Orbital (HOMO) of the DPA.<sup>[4]</sup> An ideal p-type contact requires the metal's work function to be closely aligned with the semiconductor's HOMO level to minimize the energy required for hole injection. Even with a well-chosen metal like gold, interface dipoles or surface contaminants can effectively increase this injection barrier.<sup>[5]</sup>

Troubleshooting Workflow:

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for non-Ohmic contacts.

Recommended Actions:

- Introduce a Buffer Layer: This is one of the most effective strategies. A thin buffer layer with an intermediate HOMO level can create a "step" for charge injection, effectively lowering the barrier. For DPA single-crystal OFETs, introducing a thin (e.g., 6 nm) film of 2,6-bis-phenylethynyl-anthracene (BPEA) as a buffer layer has been shown to dramatically reduce contact resistance and improve mobility.[6][7]

- Contact Doping: Inserting a very thin layer of a p-dopant, such as 2,2'-(perfluoronaphthalene-2,6-diylidene)dimalononitrile (F6-TCNNQ), at the interface can reduce the injection barrier by increasing the charge carrier concentration at the contact.[8] This effectively narrows the depletion region, facilitating easier charge injection.

- Optimize Electrode Deposition: Slowly depositing the metal electrode (e.g., Au at  $< 0.1 \text{ \AA/s}$ ) can lead to the formation of larger metal grains.[2] This can create more ordered domains at the interface, promoting channels of enhanced injection and reducing contact resistance.

## Question 2: I'm using gold (Au) electrodes, which should be good for p-type DPA, but my calculated contact resistance is still very high ( $> 100 \text{ k}\Omega\text{-cm}$ ). Why?

Answer:

While gold is a standard choice due to its high work function (~5.1 eV) and chemical stability, achieving low contact resistance is not guaranteed.[9] Several factors beyond the choice of metal can contribute to unexpectedly high  $R_c$ .

Causality:

- Poor Semiconductor Morphology: The crystalline quality and morphology of the DPA film directly under and near the contact are crucial. A disordered film has more traps and grain boundaries, which impede charge injection and transport, contributing to higher  $R_c$ .[10]

- Interface Contamination: Any residual solvents, water, or other contaminants on the dielectric surface before DPA deposition can disrupt crystal growth and create trap states at the critical channel interface.

- Sub-optimal Deposition Conditions: The temperature of the substrate during DPA deposition significantly influences film growth, crystallinity, and morphology.[11][12] An incorrect temperature can lead to a disordered film with high resistance.

Recommended Actions:

- **Implement Dielectric Surface Treatment:** Modifying the gate dielectric (typically Si/SiO<sub>2</sub>) surface is a critical step to promote highly ordered DPA film growth. Treatment with a self-assembled monolayer (SAM) like octadecyltrichlorosilane (OTS) makes the surface hydrophobic and reduces surface energy, which encourages the DPA molecules to form large, well-connected crystalline domains.[13][14]

#### Protocol: OTS Treatment of Si/SiO<sub>2</sub> Substrates

1. **Substrate Cleaning:** Ultrasonically clean the Si/SiO<sub>2</sub> substrates sequentially in acetone and isopropanol (10 minutes each).

2. **Hydroxylation:** Dry the substrates with N<sub>2</sub> gas and perform an O<sub>2</sub> plasma treatment or a piranha clean (use extreme caution) to create a hydroxylated (-OH) surface, which is necessary for the silanization reaction.

3. **SAM Deposition:** Immediately immerse the cleaned, dried substrates in a freshly prepared solution of OTS in a nonpolar solvent (e.g., toluene or hexadecane) at a concentration of 1-10 mM for 15-60 minutes in a glovebox or controlled-humidity environment.

4. **Rinsing:** Remove the substrates from the solution and rinse thoroughly with fresh toluene, followed by isopropanol, to remove any physisorbed OTS molecules.

5. **Curing:** Dry the substrates with N<sub>2</sub> and bake them on a hotplate at 120 °C for 10 minutes to complete the cross-linking of the SAM. The surface should now be highly hydrophobic.

- **Optimize DPA Deposition Parameters:** For vacuum-deposited DPA films, substrate temperature is a key parameter. A substrate temperature of around 50 °C is often used to achieve good film quality.[11][12]

| Parameter             | Typical Value               | Rationale                                                                            |

|-----------------------|-----------------------------|--------------------------------------------------------------------------------------|

| DPA Deposition Rate   | 0.2 - 0.5 Å/s               | Balances deposition time with control over film growth.[11][12]                      |

| Substrate Temperature | 50 - 70 °C                  | Provides surface mobility for DPA molecules to arrange into ordered domains.[11][12] |

| Au Deposition Rate    | 0.1 - 1.0 Å/s               | Slower rates can improve grain structure and reduce $R_c$ . [2]                      |

| Base Pressure         | < 5 x 10 <sup>-6</sup> Torr | Minimizes incorporation of impurities from the vacuum chamber into the film.         |

## Frequently Asked Questions (FAQs)

This section covers fundamental concepts crucial for designing experiments to minimize contact resistance from the outset.

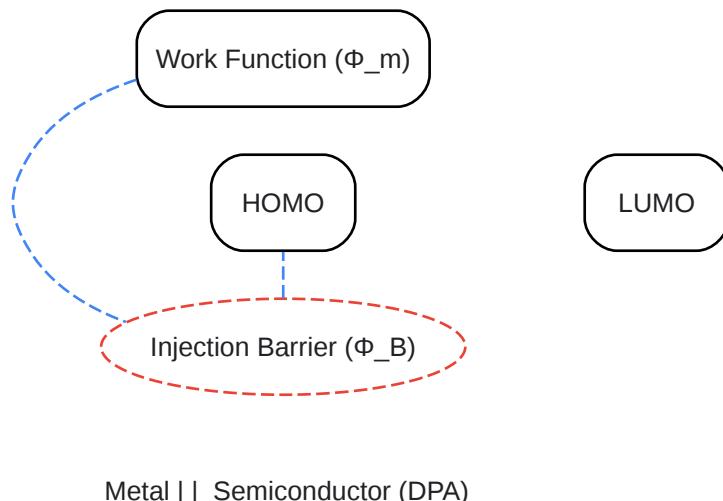

## What is the fundamental origin of contact resistance in DPA transistors?

Contact resistance ( $R_c$ ) in an OFET is not a single value but a combination of two primary components:

- **Injection Resistance ( $R_{inj}$ ):** This arises from the energy barrier between the electrode's Fermi level and the DPA's HOMO level. It is the dominant factor and is highly dependent on the work function of the metal and any interface modifications.[4]

- **Bulk Resistance ( $R_{bulk}$ ):** This is the resistance of the organic semiconductor material in the region between the contact and the transistor channel. It is influenced by the morphology, thickness, and any disorder in the DPA film under the electrode.[8]

[Click to download full resolution via product page](#)

Caption: Energy level diagram showing the hole injection barrier.

## How can I accurately measure the contact resistance in my DPA devices?

The most common and reliable method is the Transmission Line Method (TLM).<sup>[3]</sup> This involves fabricating multiple transistors on the same substrate with identical channel widths (W) but varying channel lengths (L).

Methodology:

- Fabricate a series of transistors with varying channel lengths (e.g., 50  $\mu\text{m}$ , 100  $\mu\text{m}$ , 150  $\mu\text{m}$ , 200  $\mu\text{m}$ ).

- Measure the transfer characteristics for each device and operate them in the linear regime (low VD).

- Calculate the total resistance ( $R_{\text{total}}$ ) for each device at a fixed high gate voltage (VG).

- Plot  $R_{\text{total}}$  as a function of channel length (L).

- The data should form a straight line. The y-intercept of this line is equal to  $2R_c$  (since there are two contacts, source and drain). The contact resistance is then normalized by the

channel width (W) to report it in units of  $\Omega \cdot \text{cm}$ .<sup>[3]</sup>

## Besides Gold (Au), are there other effective electrode materials for DPA?

While Au is common, other high work function metals can be effective. Platinum (Pt) has an even higher work function (~5.6 eV) and can lead to very low contact resistance, sometimes through catalytic effects at the interface that reduce the metal-semiconductor gap.<sup>[9][15]</sup> Palladium (Pd) is another option. However, fabrication with these metals can be more complex than with gold. For experimental purposes, comparing Au to another high work function metal like Pt can be a valuable exercise to probe the limits of your device performance.

## Does the device architecture (e.g., Top-Contact vs. Bottom-Contact) affect contact resistance?

Yes, significantly.

- Bottom-Contact (BC): The DPA is deposited on top of pre-patterned source/drain electrodes. This can sometimes lead to disordered DPA growth at the electrode edges, which can increase  $R_c$ . However, it allows for easy treatment of the contacts with SAMs.

- Top-Contact (TC): The electrodes are deposited on top of the DPA film. This generally results in a better interface and lower contact resistance because the DPA film is continuous.<sup>[4]</sup> The most common high-performance configuration for DPA is the Top-Contact, Bottom-Gate (TCBG) structure, as it combines the benefits of a clean, continuous semiconductor channel with a pre-fabricated gate.<sup>[11][12]</sup>

By systematically addressing these common issues and understanding the underlying principles, you can significantly reduce contact resistance and unlock the true high-performance potential of your **2,6-diphenylanthracene** transistors.

### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Contact resistance in organic field-effect transistors: conquering the barrier | NIST [nist.gov]

- 2. [communities.springernature.com](http://communities.springernature.com) [communities.springernature.com]

- 3. [researchgate.net](http://researchgate.net) [researchgate.net]

- 4. [pubs.aip.org](http://pubs.aip.org) [pubs.aip.org]

- 5. Impact of semiconductor/metal interfaces on contact resistance and operating speed of organic thin film transistors | Semantic Scholar [semanticscholar.org]

- 6. [researchgate.net](http://researchgate.net) [researchgate.net]

- 7. Low Contact Resistance Organic Single-Crystal Transistors with Band-Like Transport Based on 2,6-Bis-Phenylethynyl-Anthracene - PMC [[pmc.ncbi.nlm.nih.gov](http://pmc.ncbi.nlm.nih.gov)]

- 8. [researchgate.net](http://researchgate.net) [researchgate.net]

- 9. Electrodes for Semiconductor Gas Sensors | MDPI [[mdpi.com](http://mdpi.com)]

- 10. [researchgate.net](http://researchgate.net) [researchgate.net]

- 11. Fabrication and Evaluation of Organic Field-Effect Transistors (OFET) : 2,6-Diphenylanthracene | TCI EUROPE N.V. [[tcichemicals.com](http://tcichemicals.com)]

- 12. Fabrication and Evaluation of Organic Field-Effect Transistors (OFET) : 2,6-Diphenylanthracene | Tokyo Chemical Industry Co., Ltd.(APAC) [[tcichemicals.com](http://tcichemicals.com)]

- 13. High Mobility Organic Semiconductor: 2,6-Diphenylanthracene | TCI EUROPE N.V. [[tcichemicals.com](http://tcichemicals.com)]

- 14. [researchgate.net](http://researchgate.net) [researchgate.net]

- 15. [g.ruc.edu.cn](http://g.ruc.edu.cn) [g.ruc.edu.cn]

- To cite this document: BenchChem. [Technical Support Center: 2,6-Diphenylanthracene (DPA) Transistors]. BenchChem, [2026]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1340685#reducing-contact-resistance-in-2-6-diphenylanthracene-transistors>]

---

### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)