# Troubleshooting device fabrication with Thieno[3,2-b]thiophene-2,5-dicarbaldehyde materials

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Thieno[3,2-b]thiophene-2,5-dicarbaldehyde**

Cat. No.: **B1297048**

[Get Quote](#)

## Technical Support Center: Thieno[3,2-b]thiophene-2,5-dicarbaldehyde

Welcome to the technical support center for device fabrication using **Thieno[3,2-b]thiophene-2,5-dicarbaldehyde** and its derivatives. This resource provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in overcoming common experimental challenges.

## Frequently Asked Questions (FAQs)

Q1: What is the primary application of **Thieno[3,2-b]thiophene-2,5-dicarbaldehyde** in device fabrication?

**Thieno[3,2-b]thiophene-2,5-dicarbaldehyde** is a key building block for synthesizing larger conjugated small molecules and polymers.<sup>[1][2]</sup> Its rigid, electron-rich thienothiophene core is desirable for creating organic semiconductor (OSC) materials used in applications like Organic Field-Effect Transistors (OFETs), Organic Photovoltaics (OPVs), and Organic Light-Emitting Diodes (OLEDs).<sup>[1][2]</sup> The aldehyde functional groups provide reactive sites for further chemical synthesis, allowing for the extension of the conjugated system.

Q2: My synthesized material shows poor performance in devices. What is the most likely cause?

The purity of the organic semiconductor is a critical factor determining device performance.[\[3\]](#) [\[4\]](#) Impurities, even in small amounts, can introduce trap states that hinder charge transport, leading to low charge carrier mobility and overall poor device efficiency.[\[5\]](#)[\[6\]](#)[\[7\]](#) It is highly recommended to rigorously purify the synthesized material, for instance, by using temperature gradient sublimation.[\[3\]](#)[\[4\]](#)

Q3: The material has poor solubility in common organic solvents. How can I improve this?

Poor solubility is a common issue with rigid, planar molecules. To improve solubility for solution-based processing (e.g., spin-coating), long, flexible alkyl chains (like octyl or dodecyl groups) are often incorporated into the final molecular structure during synthesis.[\[8\]](#) If you are working with the base dicarbaldehyde, you may need to use higher boiling point solvents like dichlorobenzene or chlorobenzene and process at elevated temperatures.

Q4: What are the key device architectures for OFETs made with these materials?

OFETs are typically fabricated in one of four main architectures: Bottom-Gate, Bottom-Contact (BGBC); Bottom-Gate, Top-Contact (BGTC); Top-Gate, Bottom-Contact (TGBC); and Top-Gate, Top-Contact (TGTC).[\[9\]](#) The BGTC structure is very common, where the organic semiconductor is deposited onto the dielectric layer before the source and drain electrodes are evaporated on top.[\[10\]](#)[\[11\]](#)

Q5: Why is the charge carrier mobility of my OFET device lower than expected?

Low mobility can stem from several factors:

- Material Purity: As mentioned, impurities are a primary cause of poor performance.[\[3\]](#)[\[6\]](#)

- Thin-Film Morphology: The ordering and crystallinity of the molecules in the thin film are crucial. A disordered film will have poor charge transport pathways. Deposition conditions (e.g., substrate temperature, solvent choice, deposition rate) must be optimized.[\[8\]](#)

- Dielectric Interface: The interface between the semiconductor and the dielectric layer is where charge transport occurs. A rough or contaminated interface can trap charges. Surface

treatments, such as using a self-assembled monolayer (SAM) of octyltrichlorosilane (OTS), can dramatically improve mobility.[12]

- Environmental Factors: Exposure to oxygen and moisture can create charge traps and degrade the semiconductor material, especially for p-type materials.[9][11]

## Troubleshooting Guides

This section provides structured guidance for common problems encountered during the fabrication workflow.

### Guide 1: Material Synthesis and Purification Issues

| Problem                               | Possible Cause(s)                                                   | Suggested Solution(s)                                                                                                                                                                                                                                                            |

|---------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low reaction yield                    | Incomplete reaction; impure reagents; catalyst deactivation.        | Ensure all reagents and solvents are pure and anhydrous, especially for cross-coupling reactions (e.g., Stille, Suzuki). <sup>[13]</sup> Use fresh, high-quality catalyst. Degas the reaction mixture thoroughly to remove oxygen. Monitor reaction progress using TLC or GC-MS. |

| Product is difficult to purify        | Presence of side-products with similar polarity; residual catalyst. | Use multiple purification techniques. Start with column chromatography to separate major impurities. Follow with recrystallization or temperature gradient sublimation for final purification to achieve high-purity material suitable for electronic devices. <sup>[3][4]</sup> |

| Material degrades during purification | Thermal instability at sublimation/distillation temperatures.       | Lower the sublimation temperature and increase the vacuum to reduce the required temperature. If the material is inherently unstable, consider alternative purification methods like repeated recrystallization from different solvent systems.                                  |

## Guide 2: Thin-Film Deposition and Morphology Problems

| Problem                               | Possible Cause(s)                                                              | Suggested Solution(s)                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor film quality (cracks, dewetting) | Poor substrate wetting; incorrect solvent evaporation rate; unclean substrate. | Treat the substrate with an appropriate surface modifier (e.g., HMDS or OTS for $\text{SiO}_2$ ) to improve wetting and promote ordered molecular growth. <sup>[12]</sup> Optimize the spin-coating speed or substrate temperature to control the evaporation rate. Ensure substrates are meticulously cleaned (e.g., sonication in solvents, $\text{O}_2$ plasma treatment). |

| Inconsistent film thickness           | Non-uniform solution spreading; unstable spin-coater speed.                    | Ensure the substrate is centered on the spin-coater chuck. Use a sufficient volume of solution to cover the entire substrate before starting the spin. Verify the spin-coater's speed and acceleration profile.                                                                                                                                                               |

| Amorphous or poorly ordered films     | Sub-optimal deposition conditions; lack of thermal annealing.                  | Optimize the substrate temperature during deposition (for both solution and vacuum methods). <sup>[8]</sup> Perform post-deposition thermal annealing at a temperature between the material's glass transition and melting points to promote molecular ordering and increase crystal grain size.                                                                              |

## Guide 3: Poor OFET Device Performance

| Problem                          | Possible Cause(s)                                                                                     | Suggested Solution(s)                                                                                                                                                                                                                                                                                   |

|----------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low On/Off Current Ratio         | High off-current due to impurities or gate leakage; low on-current.                                   | Improve material purity to reduce bulk conductivity. <a href="#">[3]</a><br>Check the quality of the gate dielectric for pinholes or defects. Optimize the thin-film morphology to improve the on-current. <a href="#">[12]</a>                                                                         |

| High Contact Resistance          | Mismatch between electrode work function and semiconductor energy levels; poor interface at contacts. | Choose an electrode material with a work function that aligns with the HOMO (for p-type) or LUMO (for n-type) level of the semiconductor. Use a bottom-contact architecture with OTS treatment, which can improve injection. Ensure a clean interface between the semiconductor and the metal contacts. |

| Device instability / degradation | Sensitivity to air (oxygen) and moisture; trapped charges in the dielectric.                          | Fabricate and test devices in an inert atmosphere (e.g., a glovebox). <a href="#">[9]</a> Use a top-gate architecture where the dielectric can also serve as an encapsulation layer. <a href="#">[14]</a> Apply gate bias stress tests to check for charge trapping issues.                             |

## Quantitative Data Summary

The performance of devices based on thieno[3,2-b]thiophene derivatives is highly dependent on molecular structure and processing conditions. The tables below summarize representative performance data.

Table 1: OFET Performance of a PBTTT Polymer on Different Dielectric Surfaces

Data extracted from a study on Poly(2,5-bis(3-alkylthiophen-2-yl)thieno[3,2-b]thiophene) (PBTTT-C14).

| Substrate Surface            | Annealing Temp. | Field-Effect Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio      |

|------------------------------|-----------------|---------------------------------------------|-------------------|

| Bare SiO <sub>2</sub>        | 180 °C          | 0.002                                       | > 10 <sup>4</sup> |

| OTS-treated SiO <sub>2</sub> | 180 °C          | 0.18                                        | > 10 <sup>6</sup> |

Reference: Data adapted from J. Am. Chem. Soc. 2006, 128, 49, 15582–15583.[12]

Table 2: Performance of Solution-Sheared Dithieno[3,2-b:2',3'-d]thiophene (DTT) Derivatives

| Compound Side Group           | Avg. Charge Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio      |

|-------------------------------|--------------------------------------------|-------------------|

| 5-octylthiophen-2-yl          | 0.067                                      | > 10 <sup>6</sup> |

| 5-(2-ethylhexyl)thiophen-2-yl | 0.10                                       | > 10 <sup>7</sup> |

| Octyl                         | 0.000028                                   | > 10 <sup>5</sup> |

Reference: Data adapted from Molecules 2018, 23(10), 2459. [8][15]

## Experimental Protocols

### Protocol 1: Representative Synthesis of a Thieno[3,2-b]thiophene Derivative

This protocol describes a typical Stille coupling reaction to synthesize a derivative, which is a common method for polymers and small molecules based on the core structure.

Objective: Synthesize 2,5-di(thiophen-2-yl)thieno[3,2-b]thiophene.

Materials:

- 2,5-dibromothieno[3,2-b]thiophene

- Tributyl(thiophen-2-yl)stannane

- Tetrakis(triphenylphosphine)palladium(0)  $[\text{Pd}(\text{PPh}_3)_4]$

- Anhydrous N,N-Dimethylformamide (DMF)

Procedure:

- In a nitrogen-purged flask, dissolve 2,5-dibromothieno[3,2-b]thiophene (1 equivalent) in anhydrous DMF.

- Add tributyl(thiophen-2-yl)stannane (approx. 2.2 equivalents).

- Add the catalyst,  $\text{Pd}(\text{PPh}_3)_4$  (approx. 0.05 equivalents).

- Heat the mixture under a nitrogen atmosphere at 90 °C overnight.<sup>[13]</sup>

- After cooling to room temperature, quench the reaction by adding water.

- Extract the product into an organic solvent like dichloromethane ( $\text{CH}_2\text{Cl}_2$ ).

- Wash the organic layer with water and brine, then dry over anhydrous  $\text{MgSO}_4$ .

- Remove the solvent under reduced pressure.

- Purify the crude product by column chromatography on silica gel, followed by recrystallization or sublimation to obtain the final product.

## Protocol 2: Fabrication of a Bottom-Gate, Top-Contact (BGTC) OFET

Objective: Fabricate and characterize an OFET using a solution-processable thieno[3,2-b]thiophene derivative.

Materials:

- Heavily n-doped Si wafer with a 200-300 nm layer of thermal SiO<sub>2</sub> (serves as gate and dielectric).

- Purified organic semiconductor (OSC) material.

- High-purity organic solvent (e.g., chloroform, toluene, or dichlorobenzene).

- Gold (Au) for source-drain electrodes.

- (Optional) Octyltrichlorosilane (OTS) for surface treatment.

Procedure:

- Substrate Cleaning: Clean the Si/SiO<sub>2</sub> substrate by sonicating sequentially in deionized water, acetone, and isopropanol for 15 minutes each. Dry the substrate with a stream of nitrogen.

- (Optional) Surface Treatment: Expose the substrate to an O<sub>2</sub> plasma for 5 minutes to create hydroxyl groups. Then, immerse the substrate in a dilute solution of OTS in toluene for 30 minutes to form a self-assembled monolayer. Rinse with fresh toluene and bake at 120 °C for 20 minutes to remove residual solvent.[\[12\]](#)

- Semiconductor Deposition: Prepare a dilute solution (e.g., 5-10 mg/mL) of the OSC in the chosen solvent. Deposit the OSC thin film onto the substrate via spin-coating. Typical parameters are 2000-4000 rpm for 60 seconds.

- Annealing: Transfer the coated substrate to a hotplate in a nitrogen-filled glovebox and anneal at an optimized temperature (e.g., 100-180 °C) for 30-60 minutes to improve film crystallinity.

- Electrode Deposition: Using a shadow mask, thermally evaporate 50 nm of Au for the source and drain electrodes on top of the semiconductor film. The channel length and width are

defined by the mask.

- Characterization: Transfer the completed device to a probe station (preferably in an inert atmosphere) and measure the output and transfer characteristics using a semiconductor parameter analyzer.

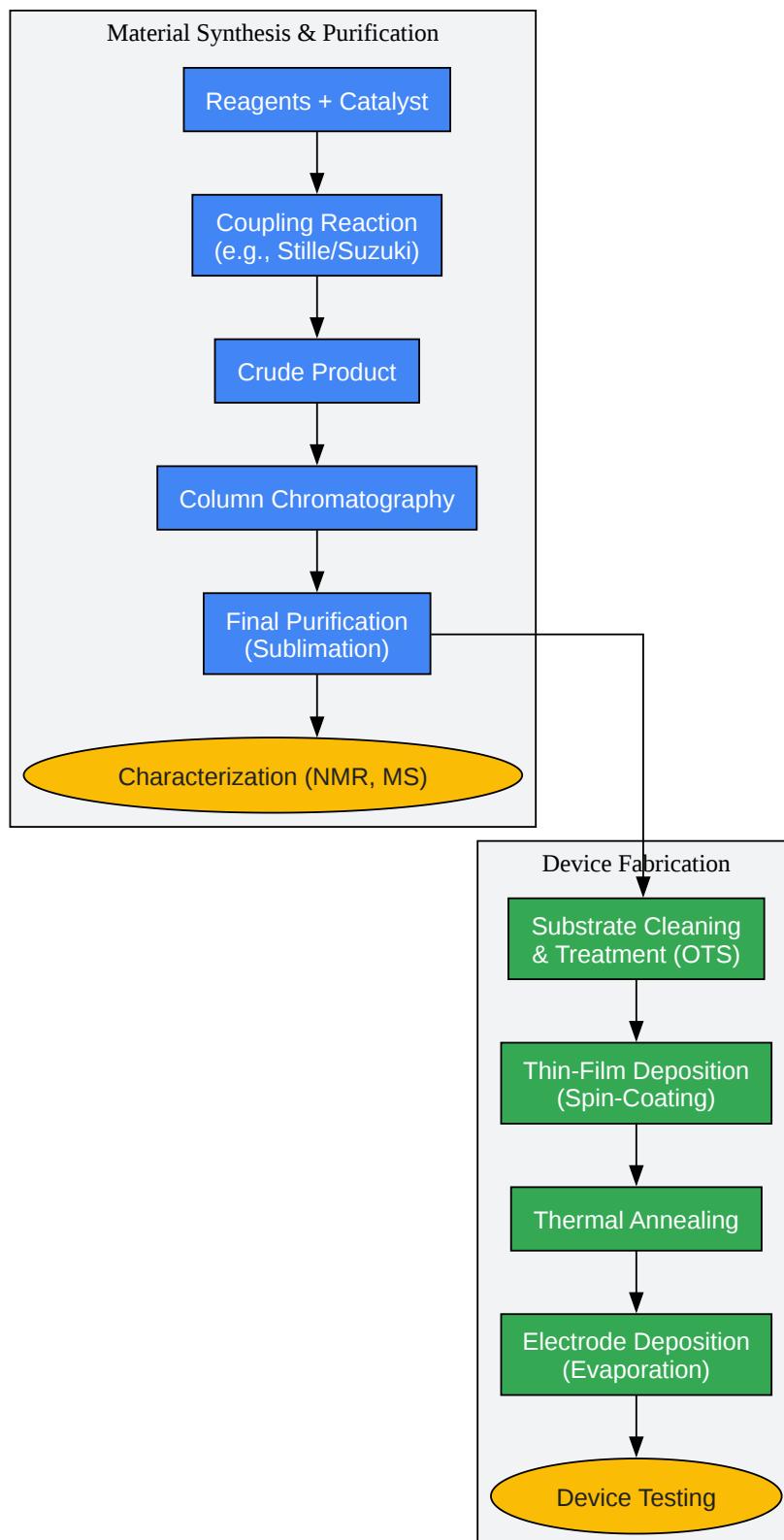

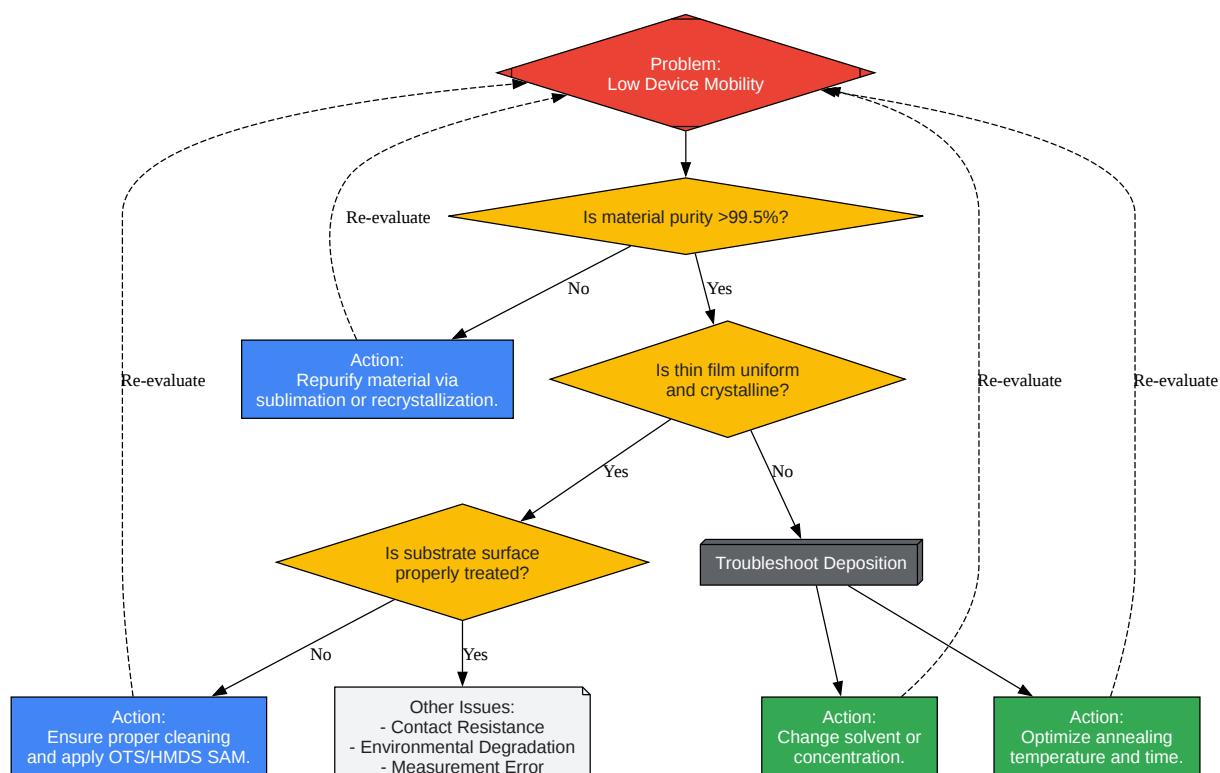

## Visualized Workflows and Logic

Below are diagrams illustrating key processes and troubleshooting logic using the Graphviz DOT language.

[Click to download full resolution via product page](#)

Caption: General workflow from material synthesis to device testing.

[Click to download full resolution via product page](#)

Caption: Troubleshooting flowchart for low charge carrier mobility.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [chemicalbook.com](http://chemicalbook.com) [chemicalbook.com]

- 2. [nbinno.com](http://nbinno.com) [nbinno.com]

- 3. Purity of organic semiconductors as a key factor for the performance of organic electronic devices - Materials Chemistry Frontiers (RSC Publishing) DOI:10.1039/D0QM00690D [pubs.rsc.org]

- 4. [researchgate.net](http://researchgate.net) [researchgate.net]

- 5. [chinesechemsoc.org](http://chinesechemsoc.org) [chinesechemsoc.org]

- 6. [anirban.people.iitgn.ac.in](http://anirban.people.iitgn.ac.in) [anirban.people.iitgn.ac.in]

- 7. [1908.11854] The influence of impurities on the charge carrier mobility of small molecule organic semiconductors [arxiv.org]

- 8. Development of Dithieno[3,2-b:2',3'-d]thiophene (DTT) Derivatives as Solution-Processable Small Molecular Semiconductors for Organic Thin Film Transistors [mdpi.com]

- 9. [ossila.com](http://ossila.com) [ossila.com]

- 10. [rfwireless-world.com](http://rfwireless-world.com) [rfwireless-world.com]

- 11. Organic field-effect transistor - Wikipedia [en.wikipedia.org]

- 12. [pubs.acs.org](http://pubs.acs.org) [pubs.acs.org]

- 13. Synthesis and Characterization of New Thieno[3,2-b]thiophene Derivatives - PMC [pmc.ncbi.nlm.nih.gov]

- 14. [pubs.aip.org](http://pubs.aip.org) [pubs.aip.org]

- 15. [researchgate.net](http://researchgate.net) [researchgate.net]

- To cite this document: BenchChem. [Troubleshooting device fabrication with Thieno[3,2-b]thiophene-2,5-dicarbaldehyde materials]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1297048#troubleshooting-device-fabrication-with-thieno-3-2-b-thiophene-2-5-dicarbaldehyde-materials>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)