# enhancing the performance of 3-Bromothieno[3,2-b]thiophene-based OFETs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## *Compound of Interest*

Compound Name: 3-Bromothieno[3,2-b]thiophene

Cat. No.: B1286399

[Get Quote](#)

## Technical Support Center: 3-Bromothieno[3,2-b]thiophene-Based OFETs

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **3-Bromothieno[3,2-b]thiophene** and its derivatives in Organic Field-Effect Transistors (OFETs).

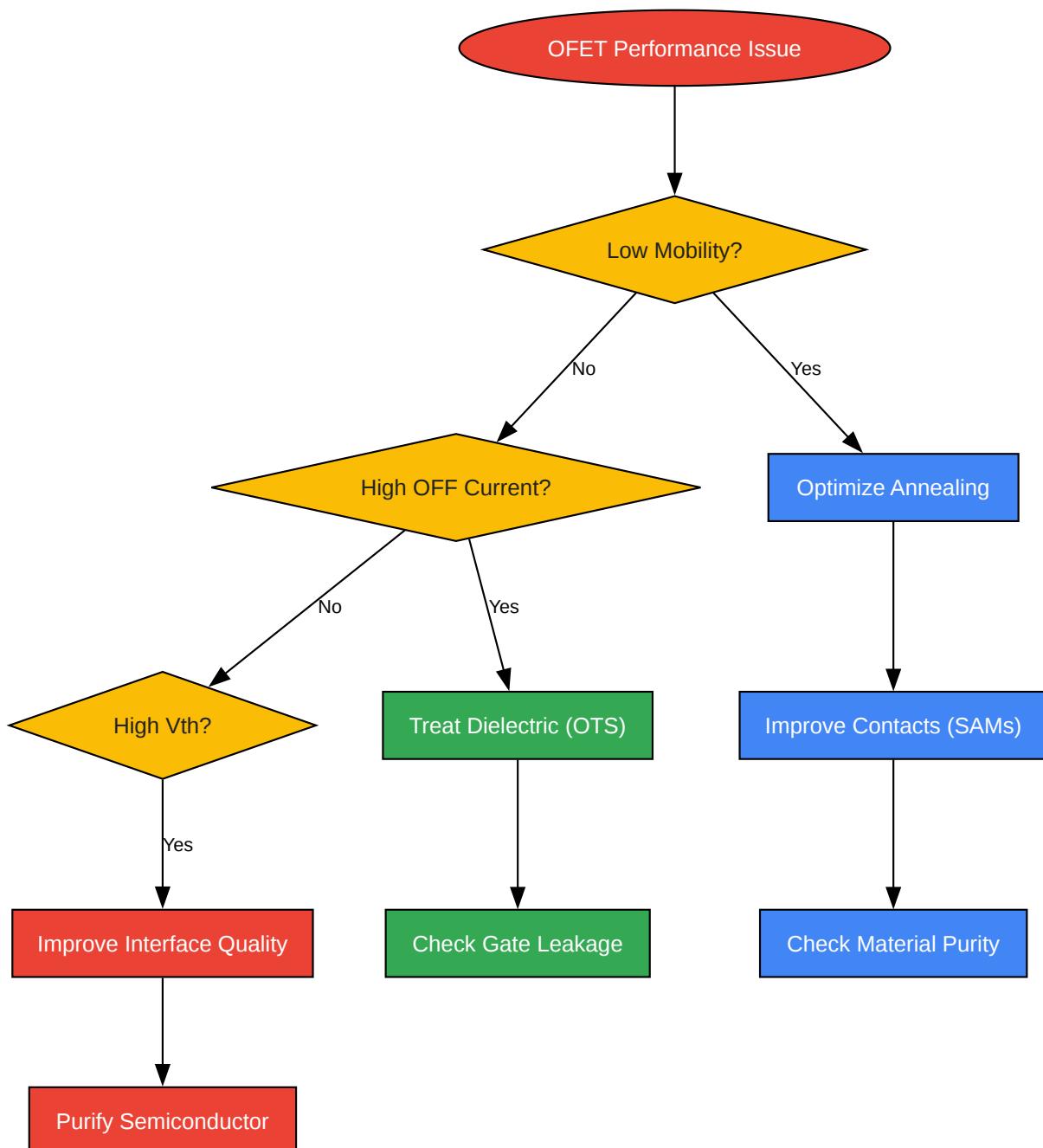

## Troubleshooting Guide

This guide addresses common issues encountered during the fabrication and characterization of **3-Bromothieno[3,2-b]thiophene**-based OFETs.

| Issue                                                                              | Potential Cause                                                                                                                                                                                                                                                                                                                                                                             | Troubleshooting Steps                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Hole Mobility                                                                  | Poor crystallinity of the semiconductor film.                                                                                                                                                                                                                                                                                                                                               | <ul style="list-style-type: none"><li>- Optimize the annealing temperature and time for the active layer.</li><li>- Experiment with different solvent systems for solution processing to control film morphology.</li><li>- Consider using solvent vapor annealing to improve molecular ordering.</li></ul> |

| High contact resistance between the semiconductor and the source/drain electrodes. | <ul style="list-style-type: none"><li>- Treat electrodes with a self-assembled monolayer (SAM) like OTS to reduce the injection barrier.</li><li>- Consider using a different electrode material with a work function better matched to the HOMO level of the semiconductor.</li><li>- Oxygen plasma treatment of the contacts may improve device performance.<a href="#">[1]</a></li></ul> |                                                                                                                                                                                                                                                                                                             |

| Impurities in the semiconductor material.                                          | <ul style="list-style-type: none"><li>- Ensure high purity of the 3-Bromothieno[3,2-b]thiophene derivative, as impurities can act as charge traps.<a href="#">[2]</a></li></ul>                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                             |

| High OFF Current / Low ON/OFF Ratio                                                | Presence of trap states at the semiconductor-dielectric interface.                                                                                                                                                                                                                                                                                                                          | <ul style="list-style-type: none"><li>- Optimize the dielectric surface by using a surface treatment like Octadecyltrichlorosilane (OTS).<a href="#">[3]</a></li><li>- Ensure a clean fabrication environment to minimize contamination that can create trap states.</li></ul>                              |

| Gate leakage current.                                                              | <ul style="list-style-type: none"><li>- Verify the integrity and thickness of the gate dielectric</li></ul>                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                             |

|                                                                                      |                                                                                                                                                                    |                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                      | layer. - Check for pinholes or defects in the dielectric.                                                                                                          |                                                                                                                                                                                                                                    |

| Large Threshold Voltage ( $V_{th}$ )                                                 | Trapped charges at the semiconductor-dielectric interface or within the semiconductor bulk.                                                                        | - This may be indicative of interface trap states between the semiconductor and the dielectric. <sup>[4]</sup> - Improve the quality of the dielectric layer and the interface through optimized deposition and surface treatment. |

| Impurities or defects in the semiconductor.                                          | - Purification of the organic semiconductor is crucial.                                                                                                            |                                                                                                                                                                                                                                    |

| Device Instability / Hysteresis                                                      | Mobile ions in the gate dielectric.                                                                                                                                | - Use high-purity dielectric materials. - Consider annealing the dielectric layer before semiconductor deposition.                                                                                                                 |

| Exposure to ambient air and moisture.                                                | - Characterize the devices in an inert atmosphere (e.g., nitrogen or argon glovebox). - Encapsulate the final device to protect it from environmental degradation. |                                                                                                                                                                                                                                    |

| Poor Film Morphology (e.g., dewetting, pinholes)                                     | Incompatible solvent and substrate surface energies.                                                                                                               | - Modify the substrate surface energy using treatments like UV-ozone or SAMs. - Choose a solvent that has good wettability on the substrate.                                                                                       |

| Sub-optimal deposition parameters (e.g., spin coating speed, substrate temperature). | - Systematically vary the deposition parameters to achieve a uniform and continuous film.                                                                          |                                                                                                                                                                                                                                    |

## Frequently Asked Questions (FAQs)

Q1: What is the typical role of **3-Bromothieno[3,2-b]thiophene** in high-performance OFETs?

A1: **3-Bromothieno[3,2-b]thiophene** is a crucial building block for synthesizing more complex, high-performance organic semiconductors.<sup>[5]</sup> Its rigid, planar structure and extended  $\pi$ -electron system contribute to efficient charge transport.<sup>[2][6]</sup> The bromine atom allows for further chemical modifications through cross-coupling reactions, enabling the creation of conjugated polymers and small molecules with tailored electronic properties.<sup>[6][7]</sup>

Q2: How does the purity of thieno[3,2-b]thiophene derivatives impact OFET performance?

A2: The purity of the organic semiconductor is paramount for optimal OFET performance. Impurities can introduce trap states that scatter or trap charge carriers, leading to a significant reduction in charge carrier mobility and a lower on/off ratio.<sup>[2]</sup> Therefore, using high-purity (typically >99%) materials is a critical step.

Q3: What are the key factors in molecular design for enhancing the performance of thieno[3,2-b]thiophene-based semiconductors?

A3: Several molecular design strategies can enhance performance:

- Extended Conjugation: Extending the  $\pi$ -conjugation of the molecule, for instance by creating dimers or polymers, generally leads to higher charge carrier mobility.<sup>[1][4][8]</sup>

- Planarity: A planar molecular structure promotes strong  $\pi$ - $\pi$  stacking in the solid state, creating efficient pathways for charge transport.<sup>[6]</sup>

- Side Chains: The choice of side chains can influence solubility, molecular packing, and film morphology. Linear alkyl chains, for example, can facilitate better molecular packing and enhance charge transport compared to branched chains.<sup>[4][9]</sup>

Q4: What is the effect of annealing on the performance of thieno[3,2-b]thiophene-based OFETs?

A4: Thermal annealing is a critical processing step that can significantly improve device performance. Annealing the semiconductor film can enhance its crystallinity and improve the molecular ordering, leading to higher charge carrier mobility.<sup>[3][10]</sup> The optimal annealing temperature and duration need to be determined experimentally for each specific material.

Q5: How can I improve the interface between the dielectric and the semiconductor layer?

A5: A high-quality semiconductor-dielectric interface is crucial for good device performance.

Treating the dielectric surface with a self-assembled monolayer (SAM) such as octadecyltrichlorosilane (OTS) is a common and effective method.<sup>[3]</sup> This treatment can reduce surface traps, improve molecular ordering of the semiconductor, and lower the threshold voltage.

## Quantitative Data

Table 1: Performance of Various Thieno[3,2-b]thiophene-Based OFETs

| Semiconductor Derivative                                       | Device Configuration        | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio                      | Reference                                 |

|----------------------------------------------------------------|-----------------------------|--------------------------------|-----------------------------------|-------------------------------------------|

| Naphthodithieno[3,2-b]thiophene (NDTT-10)                      | BGBC                        | 0.22                           | -                                 | <a href="#">[3]</a>                       |

| Naphthodithieno[3,2-b]thiophene (NDTT-12)                      | BGBC                        | 0.13                           | -                                 | <a href="#">[3]</a>                       |

| Dithieno[3,2-b:2',3'-d]thiophene (DTT) derivative (compound 2) | Top-contact, Bottom-gate    | 0.10                           | > 10 <sup>7</sup>                 | <a href="#">[4]</a> <a href="#">[9]</a>   |

| Dithieno[3,2-b:2',3'-d]thiophene (DTT) derivative (compound 3) | Top-contact, Bottom-gate    | 0.0091                         | > 10 <sup>7</sup>                 | <a href="#">[4]</a>                       |

| Benzothieno[3,2-b]thiophene (BTT) derivative (BBTT)            | Bottom-contact, Bottom-gate | 0.22                           | 1 x 10 <sup>7</sup>               | <a href="#">[8]</a>                       |

| diketopyrrolopyrrole-thieno[3,2-b]thiophene (DPPT-TT)          | -                           | 0.49 ± 0.03                    | -                                 | <a href="#">[11]</a>                      |

| 2,6-DADTT Single Crystal                                       | -                           | up to 1.26                     | 10 <sup>6</sup> - 10 <sup>8</sup> | <a href="#">[12]</a>                      |

| TT-BT with nonyl side chain                                    | BGTC                        | 0.1                            | 3.5 x 10 <sup>3</sup>             | <a href="#">[13]</a> <a href="#">[14]</a> |

| Benzo[b]thieno[2,3-d]thiophene                                 | Bottom-gate, Top-contact    | 0.005                          | > 10 <sup>6</sup>                 | <a href="#">[15]</a> <a href="#">[16]</a> |

(BTT) derivative

(compound 3)

---

BGBC: Bottom-Gate, Bottom-Contact; BGTC: Bottom-Gate, Top-Contact

## Experimental Protocols

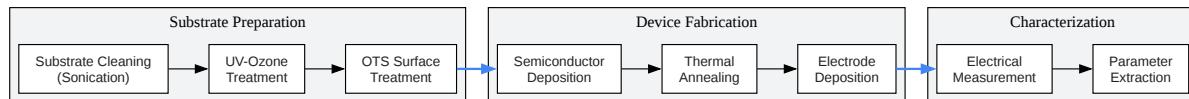

### Protocol 1: Fabrication of a Bottom-Gate, Top-Contact (BGTC) OFET

- Substrate Cleaning:

- Sequentially sonicate the Si/SiO<sub>2</sub> substrates in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of nitrogen.

- Treat the substrates with UV-ozone for 10 minutes to remove organic residues and improve the surface hydrophilicity.

- Dielectric Surface Treatment (Optional but Recommended):

- For an OTS treatment, place the cleaned substrates in a vacuum oven with a vial containing OTS at 120°C for 3 hours.[3]

- Semiconductor Deposition (Solution Shearing):

- Prepare a solution of the thieno[3,2-b]thiophene derivative in a suitable organic solvent (e.g., chloroform, toluene).

- Deposit the semiconductor film using a solution-shearing method on the treated SiO<sub>2</sub>/Si substrate.[4]

- Annealing:

- Anneal the semiconductor film at a predetermined temperature (e.g., 100°C) for a specific duration (e.g., 10 minutes) to improve crystallinity.[10]

- Electrode Deposition:

- Deposit the source and drain electrodes (e.g., Gold) through a shadow mask via thermal evaporation in a high-vacuum chamber.

#### Protocol 2: OFET Characterization

- Device Measurement Setup:

- Place the fabricated OFETs in a probe station, preferably under an inert atmosphere to minimize environmental effects.

- Use a semiconductor parameter analyzer or source-measure units to apply voltages and measure currents.

- Output Characteristics:

- Measure the drain current ( $I_d$ ) as a function of the drain-source voltage ( $V_{ds}$ ) at various constant gate-source voltages ( $V_{gs}$ ).

- Transfer Characteristics:

- Measure the drain current ( $I_d$ ) as a function of the gate-source voltage ( $V_{gs}$ ) at a constant, high drain-source voltage ( $V_{ds}$ ) (saturation regime).

- Parameter Extraction:

- Calculate the field-effect mobility ( $\mu$ ) from the slope of the  $(I_d)^{1/2}$  vs.  $V_{gs}$  plot in the saturation regime.

- Determine the threshold voltage ( $V_{th}$ ) from the x-intercept of the linear fit to the  $(I_d)^{1/2}$  vs.  $V_{gs}$  plot.

- Calculate the on/off ratio from the ratio of the maximum to the minimum drain current in the transfer curve.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Workflow for the fabrication and characterization of OFETs.

[Click to download full resolution via product page](#)

Caption: Troubleshooting logic for common OFET performance issues.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [pubs.acs.org](https://pubs.acs.org) [pubs.acs.org]

- 2. [nbinno.com](https://nbinno.com) [nbinno.com]

- 3. [researchgate.net](https://researchgate.net) [researchgate.net]

- 4. [mdpi.com](https://mdpi.com) [mdpi.com]

- 5. [scbt.com](https://scbt.com) [scbt.com]

- 6. [nbinno.com](https://nbinno.com) [nbinno.com]

- 7. Synthesis and Characterization of New Thieno[3,2-b]thiophene Derivatives - PMC [pmc.ncbi.nlm.nih.gov]

- 8. Enhanced performance of benzothieno[3,2-b]thiophene (BTT)-based bottom-contact thin-film transistors - PubMed [pubmed.ncbi.nlm.nih.gov]

- 9. [researchgate.net](https://researchgate.net) [researchgate.net]

- 10. Effects of Side-Chain Engineering with the S Atom in Thieno[3,2-b]thiophene-porphyrin to Obtain Small-Molecule Donor Materials for Organic Solar Cells - PMC [pmc.ncbi.nlm.nih.gov]

- 11. [researchgate.net](https://researchgate.net) [researchgate.net]

- 12. A new dithieno[3,2-b:2',3'-d]thiophene derivative for high performance single crystal organic field-effect transistors and UV-sensitive phototransistors - PMC [pmc.ncbi.nlm.nih.gov]

- 13. High-performance, low-voltage organic field-effect transistors using thieno[3,2-b]thiophene and benzothiadiazole co-polymers - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 14. [research.manchester.ac.uk](https://research.manchester.ac.uk) [research.manchester.ac.uk]

- 15. [mdpi.com](https://mdpi.com) [mdpi.com]

- 16. [researchgate.net](https://researchgate.net) [researchgate.net]

- To cite this document: BenchChem. [enhancing the performance of 3-Bromothieno[3,2-b]thiophene-based OFETs]. BenchChem, [2025]. [Online PDF]. Available at:

[<https://www.benchchem.com/product/b1286399#enhancing-the-performance-of-3-bromothieno-3-2-b-thiophene-based-ofets>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)