# Troubleshooting device failure in 2,5-Bis(4-biphenyl)thiophene-based OFETs

**Author:** BenchChem Technical Support Team. **Date:** January 2026

## Compound of Interest

Compound Name: 2,5-Bis(4-biphenyl)thiophene

Cat. No.: B1274985

[Get Quote](#)

## Technical Support Center: 2,5-Bis(4-biphenyl)thiophene (BP2T) OFETs

Welcome to the technical support center for researchers and scientists working with **2,5-Bis(4-biphenyl)thiophene** (BP2T)-based Organic Field-Effect Transistors (OFETs). BP2T is a high-performance, p-type organic semiconductor known for its excellent charge transport properties and stability. However, the fabrication and characterization of high-quality BP2T-based devices require careful control over various experimental parameters.

This guide provides in-depth, question-and-answer-based troubleshooting for common issues encountered during the fabrication and measurement of BP2T OFETs. Each section explains the underlying causes of device failure and offers field-proven solutions and protocols to help you achieve optimal performance.

## Troubleshooting Guide: Common Device Failures

This section addresses specific, performance-related problems. Each question is designed to reflect a real-world experimental challenge.

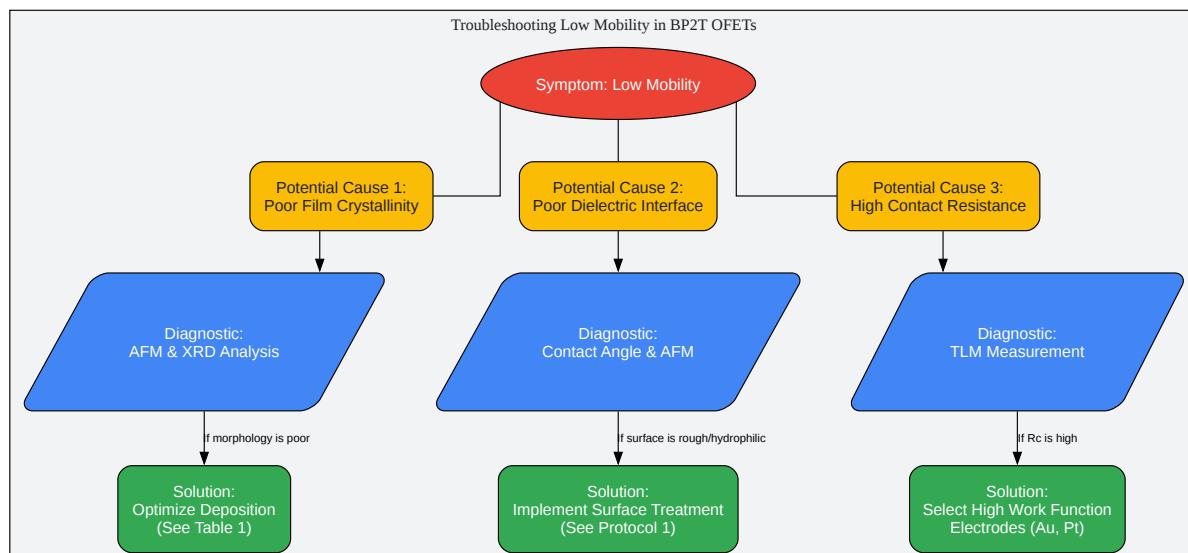

**Q1: My BP2T OFET shows very low or no charge carrier mobility. What are the likely causes and how can I fix this?**

Low charge carrier mobility is one of the most common issues and typically points to problems in the active layer's quality, the dielectric interface, or charge injection efficiency.

#### Root Cause Analysis:

- Poor Crystalline Quality of the BP2T Film: Charge transport in organic semiconductors is highly dependent on molecular ordering. Grain boundaries, amorphous regions, and other defects in the polycrystalline film act as traps and scattering sites for charge carriers, severely limiting mobility.

- Sub-optimal Dielectric Interface: The charge accumulation and transport in an OFET occur within the first few molecular layers of the semiconductor at the dielectric interface.[1][2] A contaminated, rough, or high-energy surface can disrupt the molecular packing of BP2T and introduce a high density of trap states, which immobilize charge carriers.[3]

- High Contact Resistance (R<sub>c</sub>): A significant energy barrier between the source/drain electrodes and the BP2T highest occupied molecular orbital (HOMO) can impede the injection of holes. This parasitic resistance can dominate the total device resistance, especially in short-channel devices, leading to a substantial underestimation of the intrinsic material mobility.[4][5]

#### Troubleshooting Workflow:

Below is a systematic workflow to diagnose and resolve low mobility issues.

[Click to download full resolution via product page](#)

Caption: Systematic workflow for diagnosing low mobility.

Solutions & Protocols:

- Optimize BP2T Deposition Parameters: The substrate temperature during thermal evaporation is a critical parameter that governs the surface diffusion of BP2T molecules and,

consequently, the film's morphology.

| Parameter             | Recommended Range           | Rationale                                                                                                              |

|-----------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Substrate Temperature | 120 - 180 °C                | Balances surface mobility for large grain growth against re-evaporation.                                               |

| Deposition Rate       | 0.1 - 0.5 Å/s               | A slow rate allows molecules sufficient time to arrange into ordered structures. <a href="#">[6]</a>                   |

| Base Pressure         | < 5 x 10 <sup>-6</sup> Torr | Minimizes incorporation of impurities from the vacuum chamber into the growing film.                                   |

| Film Thickness        | 30 - 50 nm                  | Ensures complete film coverage while avoiding performance issues associated with very thick films. <a href="#">[5]</a> |

- Implement Dielectric Surface Treatment: Modifying the SiO<sub>2</sub> surface with a Self-Assembled Monolayer (SAM) is crucial. A hydrophobic, low-energy surface promotes the desirable 2D layer-by-layer growth of BP2T. Octadecyltrichlorosilane (OTS) is a commonly used and effective SAM.[\[3\]](#)[\[7\]](#)

## Protocol 1: OTS Treatment of Si/SiO<sub>2</sub> Substrates

- Substrate Cleaning:

- Sequentially sonicate heavily doped Si wafers with a 300 nm thermal oxide layer in detergent, deionized (DI) water, acetone, and isopropyl alcohol (IPA) for 15 minutes each.

- Dry the substrates under a stream of high-purity nitrogen gas.

- Perform an oxygen plasma or UV-Ozone treatment for 10-15 minutes to remove organic residues and create a hydrophilic surface with -OH groups for silanization.

- OTS Solution Preparation:

- In a nitrogen-filled glovebox, prepare a dilute solution (0.1-1% by volume) of OTS in a dry, anhydrous solvent like toluene or hexadecane.

- SAM Formation:

- Immerse the cleaned, activated substrates in the OTS solution for 30-60 minutes at room temperature. The trichlorosilane headgroup will react with the surface hydroxyl groups.

- After immersion, rinse the substrates thoroughly with fresh toluene, followed by IPA, to remove any unreacted OTS physisorbed on the surface.

- Annealing & Verification:

- Anneal the substrates at 120 °C for 10 minutes to promote cross-linking and stabilize the monolayer.

- Validation: A successful OTS treatment should yield a water contact angle >100°. Use a goniometer to verify. The surface should also be exceptionally smooth, which can be confirmed with Atomic Force Microscopy (AFM).

- Minimize Contact Resistance:

- Electrode Choice: Use high work function metals like Gold (Au) or Platinum (Pt) for source/drain contacts to better align with the HOMO level of BP2T, thereby reducing the hole injection barrier.[\[8\]](#)[\[9\]](#)

- Device Architecture: For experimental devices, a top-contact, bottom-gate architecture often yields lower contact resistance compared to a bottom-contact configuration. This is because deposition of the metal onto the organic film can lead to better interfacial contact.[\[10\]](#)

## Q2: I'm observing a high OFF-current and a low ON/OFF ratio in my devices. What's wrong?

A high OFF-current suggests that the gate is unable to effectively deplete the channel of charge carriers, or there are significant leakage pathways.

#### Root Cause Analysis:

- Gate Dielectric Leakage: Pinholes, cracks, or contaminants in the  $\text{SiO}_2$  dielectric can create a conductive path between the gate electrode and the semiconductor channel.

- Semiconductor Impurities: Unintentional doping of the BP2T film, either from impure source material or contaminants during deposition, can increase the background carrier concentration, making it difficult to turn the device off.

- Surface Conduction: A hydrophilic or contaminated dielectric surface can adsorb water or other polar molecules, creating a conductive layer at the interface that is not modulated by the gate voltage.[11]

#### Solutions:

- Verify Dielectric Integrity: Before fabricating OFETs, test the dielectric by fabricating Metal-Insulator-Metal (MIM) capacitor structures (e.g., Si/ $\text{SiO}_2$ /Au). Measure the current-voltage characteristics to ensure low leakage current density ( $< 10^{-7} \text{ A/cm}^2$  at typical operating fields).

- Purify Semiconductor Material: Use BP2T that has been purified by temperature gradient sublimation. TCI Chemicals, for example, offers high-purity grades of organic semiconductors specifically for OFET applications.[12]

- Ensure Proper Surface Passivation: A high-quality OTS treatment, as described in Protocol 1, is critical. The hydrophobic monolayer displaces water from the dielectric surface, minimizing surface-related leakage currents.[3]

## Q3: The threshold voltage ( $V_{th}$ ) of my devices is unstable and shifts during measurement. Why is this happening?

Threshold voltage instability, often observed as a continuous shift during prolonged application of a gate bias, is a classic sign of charge trapping. This is also known as the "bias stress effect."[\[13\]](#)

#### Root Cause Analysis:

- Charge Trapping at the Dielectric Interface: The most common cause is the presence of trap states at the semiconductor-dielectric interface.[\[13\]](#) During device operation, charge carriers can become immobilized in these traps. The trapped charge creates an internal electric field that opposes the applied gate field, requiring a larger gate voltage to turn the device on, thus shifting  $V_{th}$ .

- Mobile Ions in the Dielectric: Impurities like sodium ions within the  $\text{SiO}_2$  can drift under the influence of the gate electric field, leading to  $V_{th}$  instability.

- Environmental Factors: The interaction of the BP2T channel with atmospheric components like oxygen and water can create trap states or lead to reversible doping effects, causing instability.[\[14\]](#)[\[15\]](#)

#### Solutions:

- Improve Interface Quality: The most effective solution is a high-quality dielectric surface passivation, such as the OTS treatment in Protocol 1. A well-formed SAM reduces the density of trap states (like silanol groups) at the  $\text{SiO}_2$  surface.[\[3\]](#)[\[16\]](#)

- Use High-Quality Substrates: Source pre-cleaned, electronics-grade Si/ $\text{SiO}_2$  wafers from reputable suppliers to minimize mobile ion contamination.

- Encapsulation: For ultimate stability, encapsulate the finished device with a material like CYTOP or parylene-C. This provides a barrier against oxygen and moisture, significantly reducing environmental degradation and bias stress effects.[\[14\]](#)

- Measurement Environment: Whenever possible, perform electrical characterization in an inert environment (e.g., a nitrogen-filled glovebox) to isolate device performance from atmospheric effects.

## Frequently Asked Questions (FAQs)

Q: What is the best device architecture for BP2T OFETs: top-contact or bottom-contact?

A: For research and performance optimization, the Top-Contact, Bottom-Gate (TCBG) architecture is generally preferred. In this configuration, the source and drain electrodes are deposited on top of the organic semiconductor. This often results in a cleaner semiconductor-dielectric interface and can lead to lower contact resistance compared to the Bottom-Contact (BCBG) geometry.[\[10\]](#) However, BCBG is often more relevant for certain high-resolution printing and industrial fabrication processes.

Caption: Comparison of TCBG and BCBG device architectures.

Q: How does air exposure affect BP2T device performance?

A: BP2T is relatively stable compared to many other organic semiconductors. However, prolonged exposure to ambient air, particularly under illumination and electrical bias, can lead to degradation. The primary mechanisms are:

- Oxygen: Oxygen can act as a p-dopant, increasing the OFF-current and causing a positive shift in the threshold voltage.

- Moisture: Water molecules can get trapped at the dielectric interface, leading to  $V_{th}$  instability and hysteresis in the transfer characteristics.[\[11\]](#)[\[14\]](#) For consistent and reliable measurements, testing in an inert atmosphere is strongly recommended.

Q: Can I use a solution-based method to deposit BP2T?

A: BP2T has low solubility in common organic solvents, making it unsuitable for typical solution-processing techniques like spin-coating. Thermal vapor deposition (evaporation) in a high-vacuum chamber is the standard and most reliable method for depositing high-quality, crystalline thin films of BP2T for OFET applications.[\[17\]](#)[\[18\]](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. mdpi.com [mdpi.com]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. fkf.mpg.de [fkf.mpg.de]

- 6. corial.plasmatherm.com [corial.plasmatherm.com]

- 7. Engineering gate dielectric surface properties for enhanced polymer field-effect transistor performance - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 8. researchgate.net [researchgate.net]

- 9. g.ruc.edu.cn [g.ruc.edu.cn]

- 10. fkf.mpg.de [fkf.mpg.de]

- 11. researchgate.net [researchgate.net]

- 12. tcichemicals.com [tcichemicals.com]

- 13. researchgate.net [researchgate.net]

- 14. Role of time-dependent foreign molecules bonding in the degradation mechanism of polymer field-effect transistors in ambient conditions - PMC [pmc.ncbi.nlm.nih.gov]

- 15. researchgate.net [researchgate.net]

- 16. researchgate.net [researchgate.net]

- 17. ossila.com [ossila.com]

- 18. Thin Film Deposition Techniques: A Comprehensive Review [article.innovationforever.com]

- To cite this document: BenchChem. [Troubleshooting device failure in 2,5-Bis(4-biphenyl)thiophene-based OFETs]. BenchChem, [2026]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1274985#troubleshooting-device-failure-in-2-5-bis-4-biphenyl-thiophene-based-ofets>]

---

### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)