# Troubleshooting poor performance in Thieno[2,3-b]thiophene OFETs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Thieno[2,3-b]thiophene*

Cat. No.: *B1266192*

[Get Quote](#)

## Technical Support Center: Thieno[2,3-b]thiophene OFETs

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **thieno[2,3-b]thiophene**-based Organic Field-Effect Transistors (OFETs).

## Frequently Asked Questions (FAQs)

**Q1:** What are typical performance benchmarks for **thieno[2,3-b]thiophene**-based OFETs?

**A1:** The performance of **thieno[2,3-b]thiophene** OFETs can vary significantly based on the specific derivative, device architecture, and fabrication conditions. However, high-performance devices typically exhibit hole mobilities in the range of 0.1 to over 1.0 cm<sup>2</sup>/Vs and ON/OFF current ratios exceeding 10<sup>6</sup>. For instance, some derivatives have shown hole mobilities as high as 0.42 cm<sup>2</sup>/Vs with ON/OFF ratios greater than 10<sup>8</sup>.<sup>[1]</sup> The table below summarizes the performance of some recently reported **thieno[2,3-b]thiophene** derivatives.

**Q2:** What are the most critical factors influencing the performance of **thieno[2,3-b]thiophene** OFETs?

**A2:** Several factors critically impact device performance:

- Molecular Structure: The choice of side-chains and substituents on the **thieno[2,3-b]thiophene** core significantly affects molecular packing, crystallinity, and, consequently, charge transport.[\[1\]](#)

- Thin Film Morphology: The ordering and connectivity of the crystalline domains in the semiconductor thin film are paramount for efficient charge transport.[\[2\]](#)[\[3\]](#)[\[4\]](#)[\[5\]](#)

- Dielectric Interface: The quality of the semiconductor-dielectric interface is crucial, as charge transport occurs in the first few molecular layers. Traps and defects at this interface can severely limit device performance.[\[6\]](#)

- Contact Resistance: High contact resistance at the source/drain electrodes can impede charge injection and extraction, leading to underestimated device performance.[\[7\]](#)[\[8\]](#)[\[9\]](#)[\[10\]](#)[\[11\]](#)

Q3: What are the common device architectures for **thieno[2,3-b]thiophene** OFETs?

A3: The most common device architectures are Bottom-Gate Top-Contact (BGTC) and Bottom-Gate Bottom-Contact (BGBC).[\[12\]](#)[\[13\]](#) In a BGTC architecture, the source and drain electrodes are deposited on top of the semiconductor layer, which can lead to better contact. In a BGBC architecture, the semiconductor is deposited on top of the pre-patterned source and drain electrodes. The choice of architecture can influence factors like contact resistance and is often determined by the fabrication facilities available.

## Troubleshooting Guides

### Issue 1: Low Carrier Mobility (< 0.01 cm<sup>2</sup>/Vs)

Possible Causes and Solutions

| Cause                                             | Recommended Action                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor Film Morphology                              | Optimize the deposition parameters. For solution-processed films, this includes the choice of solvent, solution concentration, deposition speed (for techniques like solution shearing or dip-coating), and substrate temperature. <a href="#">[2]</a> <a href="#">[3]</a> <a href="#">[4]</a> <a href="#">[5]</a> Consider post-deposition annealing to improve crystallinity. |

| Sub-optimal Molecular Packing                     | If possible, explore different thieno[2,3-b]thiophene derivatives with varying side chains. Linear alkyl chains, for example, can promote better $\pi$ - $\pi$ stacking compared to bulky or branched chains. <a href="#">[1]</a>                                                                                                                                               |

| High Density of Traps at the Dielectric Interface | Treat the dielectric surface with a self-assembled monolayer (SAM) such as octadecyltrichlorosilane (OTS) or hexamethyldisilazane (HMDS) to reduce surface energy and passivate trap states. <a href="#">[6]</a>                                                                                                                                                                |

| Impure Semiconductor Material                     | Purify the thieno[2,3-b]thiophene material using techniques like temperature gradient sublimation to remove impurities that can act as charge traps.                                                                                                                                                                                                                            |

## Issue 2: High OFF-Current (Low ON/OFF Ratio $< 10^4$ )

### Possible Causes and Solutions

| Cause                         | Recommended Action                                                                                                                                                                                     |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bulk Conduction               | Optimize the thickness of the semiconductor film. Thicker films can lead to increased bulk conduction and a higher OFF-current.                                                                        |

| Gate Leakage Current          | Inspect the gate dielectric for pinholes or defects. Ensure the dielectric layer is of sufficient thickness and quality to prevent significant current leakage from the gate electrode.                |

| Doping by Atmospheric Species | Perform device fabrication and characterization in an inert atmosphere (e.g., a nitrogen-filled glovebox) to minimize unintentional doping by oxygen and moisture, which can increase the OFF-current. |

| Impurity-related Conduction   | Ensure high purity of the semiconductor material and solvents used during fabrication.                                                                                                                 |

## Issue 3: High Contact Resistance

### Possible Causes and Solutions

| Cause                        | Recommended Action                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy Level Mismatch        | Select source/drain electrode materials with work functions that align well with the HOMO level of the p-type thieno[2,3-b]thiophene semiconductor to facilitate efficient hole injection.                                                                                                                                                                                    |

| Poor Metal-Organic Interface | Optimize the deposition of the source/drain electrodes. For evaporated metals, a slower deposition rate can lead to larger grain sizes and improved contact. <sup>[7]</sup> Consider using a contact doping layer, such as a thin layer of molybdenum oxide (MoO <sub>x</sub> ), between the electrode and the semiconductor to reduce the injection barrier. <sup>[14]</sup> |

| Device Geometry              | In bottom-contact devices, ensure the surface of the electrodes is clean and properly treated before semiconductor deposition. In top-contact devices, be mindful of potential damage to the organic layer during electrode deposition.                                                                                                                                       |

## Data Presentation

Table 1: Performance of Selected **Thieno[2,3-b]thiophene**-based OFETs

| Thieno[2,3-b]thiophene Derivative                            | Deposition Method | Mobility (cm <sup>2</sup> /Vs) | ON/OFF Ratio      | Reference |

|--------------------------------------------------------------|-------------------|--------------------------------|-------------------|-----------|

| 2,5-bis((5-octylthiophen-2-yl)ethynyl)thieno[2,3-b]thiophene | Solution Shearing | 0.42                           | > 10 <sup>8</sup> |           |

| 2,5-bis(phenylethynyl)thieno[2,3-b]thiophene                 | Solution Shearing | ~0.075                         | > 10 <sup>6</sup> | [15]      |

| 2,5-bis(thiophen-2-ylethynyl)thieno[2,3-b]thiophene          | Solution Shearing | ~0.075                         | > 10 <sup>6</sup> | [15]      |

| Benzo[b]thieno[2,3-d]thiophene Derivative                    | Solution Shearing | 0.005                          | > 10 <sup>6</sup> | [16]      |

## Experimental Protocols

### 1. Dielectric Surface Treatment with Octadecyltrichlorosilane (OTS)

- Substrate Cleaning: Sequentially sonicate the Si/SiO<sub>2</sub> substrates in deionized water, acetone, and isopropyl alcohol for 15 minutes each.

- Drying: Dry the substrates under a stream of nitrogen and then bake on a hotplate at 120°C for 30 minutes to remove any residual moisture.

- UV-Ozone Treatment: Treat the substrates with UV-ozone for 15 minutes to create a hydrophilic surface with hydroxyl groups.

- OTS Solution Preparation: Prepare a 10 mM solution of OTS in anhydrous toluene or hexane inside a nitrogen-filled glovebox.

- SAM Deposition: Immerse the cleaned substrates in the OTS solution for 30 minutes at room temperature.

- Rinsing: Rinse the substrates sequentially with fresh toluene (or hexane) and isopropyl alcohol to remove any physisorbed OTS molecules.

- Annealing: Anneal the substrates at 120°C for 20 minutes to promote the formation of a dense, cross-linked monolayer.

## 2. Solution Shearing of **Thieno[2,3-b]thiophene** Thin Films

- Solution Preparation: Dissolve the **thieno[2,3-b]thiophene** derivative in a high-boiling point solvent (e.g., chlorobenzene, dichlorobenzene) at a concentration of 5-10 mg/mL. Gently heat and stir the solution to ensure complete dissolution.

- Substrate Preparation: Place the OTS-treated Si/SiO<sub>2</sub> substrate on a temperature-controlled stage set to the desired deposition temperature (e.g., 80-120°C).

- Deposition: Dispense a small volume of the semiconductor solution (e.g., 100 µL) at the edge of a clean, flat blade (e.g., a glass slide or another silicon wafer) held at a slight angle to the substrate.

- Shearing: Move the blade across the substrate at a constant, slow speed (e.g., 0.1-1 mm/s). The solvent will evaporate as the blade moves, leaving behind a crystalline thin film.

- Annealing: Post-deposition, anneal the film at a temperature slightly below the material's melting point for 30-60 minutes to further improve crystallinity.

## Visualizations

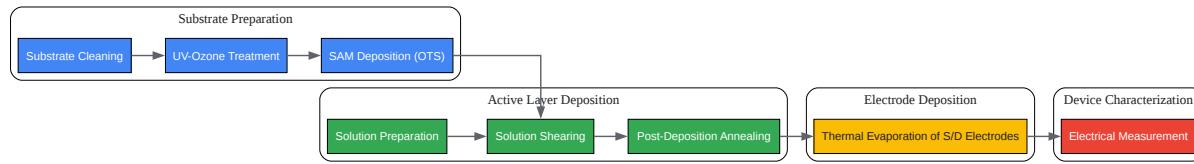

[Click to download full resolution via product page](#)

Caption: Workflow for the fabrication of a bottom-gate, top-contact **thiophene[2,3-b]thiophene** OFET.

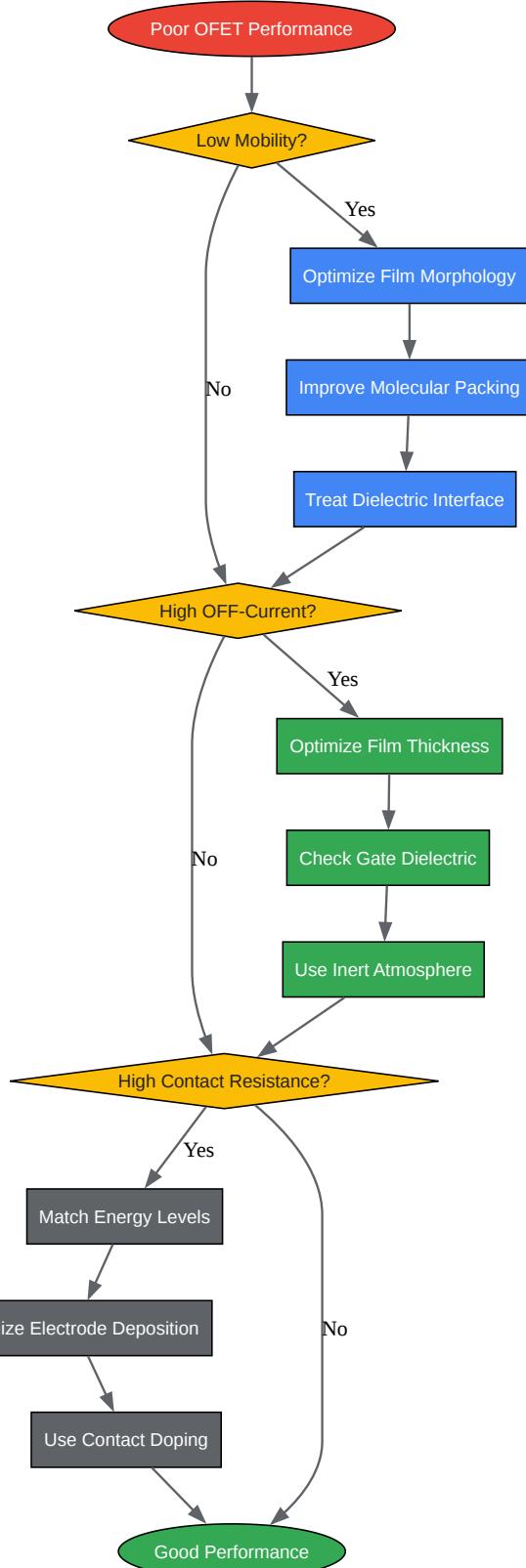

[Click to download full resolution via product page](#)

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Performance enhancement of air-stable thieno[2,3-b]thiophene organic field-effect transistors via alkyl chain engineering - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 2. researchgate.net [researchgate.net]

- 3. [PDF] Morphology control strategies for solution-processed organic semiconductor thin films | Semantic Scholar [semanticscholar.org]

- 4. Morphology control strategies for solution-processed organic semiconductor thin films - Energy & Environmental Science (RSC Publishing) DOI:10.1039/C4EE00688G [pubs.rsc.org]

- 5. Morphology control strategies for solution-processed organic semiconductor thin films - Energy & Environmental Science (RSC Publishing) [pubs.rsc.org]

- 6. mdpi.com [mdpi.com]

- 7. communities.springernature.com [communities.springernature.com]

- 8. pubs.acs.org [pubs.acs.org]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- 11. pubs.aip.org [pubs.aip.org]

- 12. researchgate.net [researchgate.net]

- 13. academic.oup.com [academic.oup.com]

- 14. researchgate.net [researchgate.net]

- 15. scholars.ncu.edu.tw [scholars.ncu.edu.tw]

- 16. mdpi.com [mdpi.com]

- To cite this document: BenchChem. [Troubleshooting poor performance in Thieno[2,3-b]thiophene OFETs]. BenchChem, [2025]. [Online PDF]. Available at:

[<https://www.benchchem.com/product/b1266192#troubleshooting-poor-performance-in-thieno-2-3-b-thiophene-ofets>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

**Contact**

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)