# Technical Support Center: Enhancing Circumcoronene Electronic Device Performance

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Circumcoronene**

Cat. No.: **B1264081**

[Get Quote](#)

This technical support center provides troubleshooting guides, frequently asked questions (FAQs), and experimental protocols for researchers, scientists, and drug development professionals working with **circumcoronene**-based electronic devices. The information is presented in a question-and-answer format to directly address common challenges encountered during experimentation.

## Frequently Asked Questions (FAQs)

**Q1:** What are the typical performance benchmarks for **circumcoronene**-based field-effect transistors (FETs)?

**A1:** While extensive data on unsubstituted **circumcoronene** FETs is still emerging, research on derivatives provides valuable insights. For instance, solution-processed field-effect transistors using cyano- and chloro-substituted coronene diimides have demonstrated promising n-type semiconductor performance with electron mobilities reaching up to  $0.16 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  in air.<sup>[1]</sup> Performance is highly dependent on factors such as the purity of the material, the deposition method, the choice of dielectric, and the quality of the source-drain contacts.

**Q2:** What are the key challenges in fabricating high-performance **circumcoronene** electronic devices?

**A2:** The primary challenges include:

- Solubility: **Circumcoronene**'s planar and extended aromatic structure leads to strong intermolecular  $\pi$ - $\pi$  stacking, resulting in poor solubility in common organic solvents. This makes solution-based processing difficult.

- Film Morphology: Achieving large, well-ordered crystalline domains in thin films is crucial for efficient charge transport. Controlling the morphology during vacuum deposition or solution-based methods is a significant hurdle.

- Contact Resistance: High contact resistance between the metallic source/drain electrodes and the **circumcoronene** active layer can severely limit device performance.[\[2\]](#)[\[3\]](#)[\[4\]](#)

- Stability: Like many organic semiconductors, **circumcoronene** devices can be susceptible to degradation upon exposure to oxygen, moisture, and ambient light.[\[5\]](#)

Q3: How does the choice of gate dielectric affect device performance?

A3: The gate dielectric plays a critical role in the performance of **circumcoronene** FETs. Its properties influence carrier mobility, threshold voltage, and device stability. A high-quality dielectric with a smooth surface can promote better ordering of the **circumcoronene** molecules at the interface, leading to improved charge transport. Furthermore, the dielectric constant of the material impacts the gate capacitance and, consequently, the charge carrier density induced in the channel for a given gate voltage.[\[6\]](#)[\[7\]](#)[\[8\]](#)

## Troubleshooting Guides

This section provides solutions to common problems encountered during the fabrication and characterization of **circumcoronene** electronic devices.

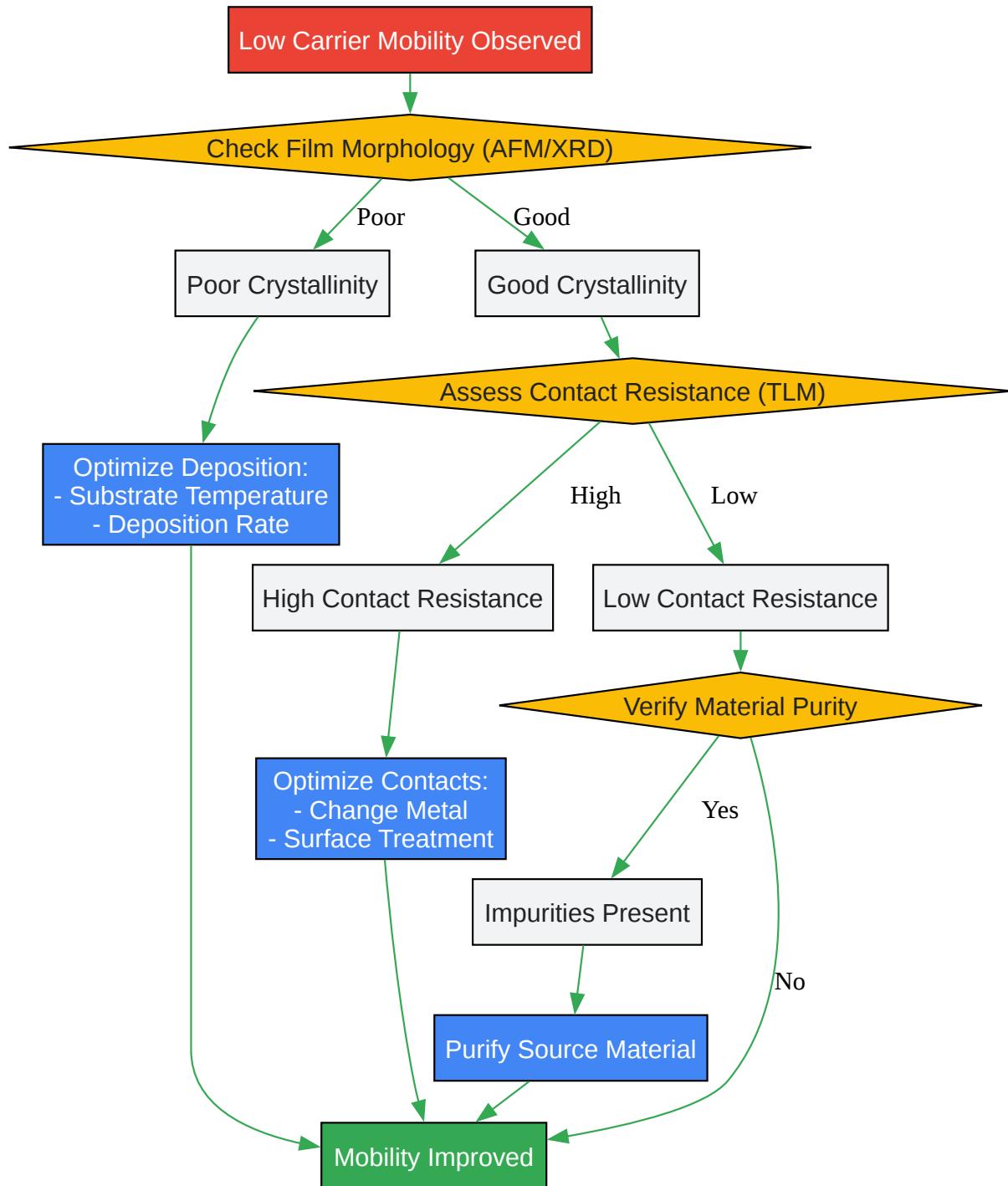

### Issue 1: Low Carrier Mobility

Symptoms:

- The calculated field-effect mobility is significantly lower than expected values for polycyclic aromatic hydrocarbons.

- The device shows weak current modulation with the gate voltage.

Possible Causes and Solutions:

| Cause                        | Solution                                                                                                                                                                                                                                          |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor Film Crystallinity      | Optimize the deposition parameters. For thermal evaporation, adjust the substrate temperature and deposition rate. A slower deposition rate and an elevated, optimized substrate temperature can promote the growth of larger crystalline grains. |

| Impurities in Circumcoronene | Purify the circumcoronene source material using techniques like sublimation or chromatography to remove impurities that can act as charge traps.                                                                                                  |

| Rough Dielectric Surface     | Use an ultra-smooth gate dielectric or treat the dielectric surface with a self-assembled monolayer (SAM) to promote better molecular ordering.                                                                                                   |

| High Contact Resistance      | See the "High Contact Resistance" troubleshooting section below.                                                                                                                                                                                  |

## Issue 2: High "Off" Current and Low On/Off Ratio

### Symptoms:

- The transistor does not switch off completely, showing a significant drain current even at zero gate voltage.

- The ratio of the "on" current to the "off" current is low (e.g.,  $< 10^3$ ).

### Possible Causes and Solutions:

| Cause                | Solution                                                                                                                                                                                                                    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unintentional Doping | Impurities or atmospheric dopants (like oxygen or water) can increase the off-current. Handle and process the device in an inert atmosphere (e.g., a glovebox). Anneal the device in a vacuum to desorb adsorbates.         |

| Gate Leakage Current | A thin or defective gate dielectric can lead to a leakage current from the gate to the channel, contributing to the off-current. Ensure the integrity and thickness of the dielectric layer.                                |

| Bulk Conduction      | If the circumcoronene film is too thick, conduction may occur through the bulk of the film, which is not effectively modulated by the gate field. Optimize the film thickness to be in the range of a few molecular layers. |

## Issue 3: High Contact Resistance

Symptoms:

- Non-linear output characteristics ( $I_d$ - $V_d$ ) at low drain voltages.

- Underestimation of carrier mobility.

- Device performance is limited by charge injection rather than charge transport in the channel.

Possible Causes and Solutions:

| Cause                         | Solution                                                                                                                                                                                                                         |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy Barrier at the Contact | The work function of the source/drain metal is not well-matched with the HOMO/LUMO levels of circumcoronene. Select metals with appropriate work functions (e.g., gold for p-type, low work function metals for n-type).         |

| Poor Interfacial Morphology   | Roughness or contamination at the metal-semiconductor interface can impede charge injection. Ensure a clean interface by fabricating devices in a high-vacuum environment.                                                       |

| Contact Geometry              | Optimize the contact geometry. For bottom-gate, top-contact devices, ensure good adhesion of the metal to the circumcoronene layer. For top-gate, bottom-contact devices, treat the contact surface to improve charge injection. |

## Issue 4: Device Instability

Symptoms:

- Device performance degrades over time when exposed to air.

- Hysteresis is observed in the transfer characteristics.

Possible Causes and Solutions:

| Cause                                       | Solution                                                                                                                                                                                                               |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oxidation and Moisture Effects              | Oxygen and water molecules can act as traps or dopants. Encapsulate the device with a suitable barrier layer (e.g., CYTOP, Al <sub>2</sub> O <sub>3</sub> ) to protect it from the ambient environment. <sup>[5]</sup> |

| Charge Trapping at the Dielectric Interface | Defects at the semiconductor-dielectric interface can trap charge carriers, leading to hysteresis. Use high-quality dielectrics and consider surface treatments to passivate trap states.                              |

| Photodegradation                            | Exposure to UV light can cause chemical degradation of the circumcoronene molecules. Store and handle devices in the dark or under filtered light.                                                                     |

## Quantitative Data

Due to the limited availability of extensive experimental data on unsubstituted **circumcoronene** electronic devices, the following table includes performance metrics for a functionalized coronene derivative and typical ranges for high-performance polycyclic aromatic hydrocarbon (PAH) FETs to provide a benchmark.

| Parameter                                                           | Cyano- & Chloro-Substituted Coronene Diimide (n-type) <sup>[1]</sup> | Typical High-Performance PAH FETs (p-type) |

|---------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------|

| Carrier Mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | up to 0.16                                                           | 1 - 10                                     |

| On/Off Current Ratio                                                | Not Reported                                                         | > 10 <sup>6</sup>                          |

| Contact Resistance (Ω·cm)                                           | Not Reported                                                         | 10 <sup>3</sup> - 10 <sup>5</sup>          |

| Processing Method                                                   | Solution-Processed                                                   | Vacuum-Deposited or Solution-Processed     |

## Experimental Protocols

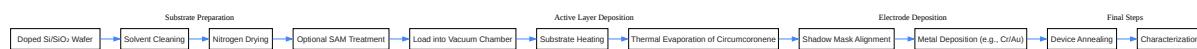

# Protocol 1: Fabrication of a Bottom-Gate, Top-Contact Circumcoronene FET

This protocol describes a general procedure for fabricating a **circumcoronene** field-effect transistor using thermal evaporation.

## 1. Substrate Preparation:

- Start with a heavily doped silicon wafer (acting as the gate electrode) with a thermally grown silicon dioxide ( $\text{SiO}_2$ ) layer (typically 100-300 nm) as the gate dielectric.

- Clean the substrate sequentially in ultrasonic baths of deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of dry nitrogen.

- Optional: Treat the  $\text{SiO}_2$  surface with a self-assembled monolayer (SAM) like octadecyltrichlorosilane (OTS) to improve the ordering of the **circumcoronene** film and reduce charge trapping.

## 2. **Circumcoronene** Deposition:

- Place the prepared substrate in a high-vacuum thermal evaporation system (base pressure  $< 10^{-6}$  Torr).

- Place high-purity **circumcoronene** powder in a Knudsen cell or a baffled boat.

- Heat the substrate to an optimized temperature (e.g., 80-150 °C) to promote crystalline film growth.

- Deposit a thin film of **circumcoronene** (typically 20-50 nm) at a low deposition rate (e.g., 0.1-0.5 Å/s).

## 3. Electrode Deposition:

- Without breaking the vacuum, deposit the source and drain electrodes through a shadow mask.

- For p-type behavior, use a high work function metal like gold (Au).

- Deposit a thin adhesion layer of chromium (Cr) or titanium (Ti) (2-5 nm) followed by a thicker layer of Au (30-50 nm).

- The channel length and width are defined by the shadow mask.

## 4. Device Annealing and Characterization:

- Post-deposition annealing in a vacuum or inert atmosphere can be performed to improve film crystallinity and device performance.

- Characterize the device in an inert environment using a semiconductor parameter analyzer to obtain the output and transfer characteristics.

## Visualizations

### Experimental Workflow for Circumcoronene FET Fabrication

[Click to download full resolution via product page](#)

Caption: Workflow for fabricating a bottom-gate, top-contact **circumcoronene** FET.

### Troubleshooting Logic for Low Carrier Mobility

[Click to download full resolution via product page](#)

Caption: A logical flow for troubleshooting low carrier mobility in **circumcoronene** devices.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Cyano- and chloro-substituted coronene diimides as solution-processable electron-transporting semiconductors - Chemical Communications (RSC Publishing) [pubs.rsc.org]

- 2. researchoutput.ncku.edu.tw [researchoutput.ncku.edu.tw]

- 3. graphenea.com [graphenea.com]

- 4. mdpi.com [mdpi.com]

- 5. researchgate.net [researchgate.net]

- 6. nfml.yonsei.ac.kr [nfml.yonsei.ac.kr]

- 7. Optimization of NS-GAAFET technology through low- $\kappa$  dielectrics for spacer fabrication - Webthesis [webthesis.biblio.polito.it]

- 8. Low-Temperature-Processed High-Performance Pentacene OTFTs with Optimal Nd-Ti Oxynitride Mixture as Gate Dielectric - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Technical Support Center: Enhancing Circumcoronene Electronic Device Performance]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b1264081#enhancing-the-performance-of-circumcoronene-electronic-devices>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)