# how to reduce impurities during silicene synthesis

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## *Compound of Interest*

Compound Name: *Silicene*

Cat. No.: *B1259896*

[Get Quote](#)

## Silicene Synthesis Technical Support Center

Welcome to the technical support center for silicene synthesis. This resource is designed for researchers, scientists, and professionals in drug development who are working with silicene and wish to minimize impurities and structural defects during their experiments. Here you will find troubleshooting guides, frequently asked questions (FAQs), detailed experimental protocols, and data to help you achieve high-quality silicene growth.

## Troubleshooting Guide

This guide addresses common issues encountered during silicene synthesis via Molecular Beam Epitaxy (MBE).

| Problem                                                                                                                        | Possible Cause(s)                                                                                                                                                                                             | Suggested Solution(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LEED pattern shows a mix of silicene phases (e.g., (4x4), ( $\sqrt{13} \times \sqrt{13}$ ), ( $2\sqrt{3} \times 2\sqrt{3}$ )). | <ul style="list-style-type: none"><li>- Sub-optimal substrate temperature during deposition.</li><li>- Incorrect silicon deposition rate.</li><li>- Surface contamination on the Ag(111) substrate.</li></ul> | <ul style="list-style-type: none"><li>- Adjust the substrate temperature. Different phases are stable at different temperatures. For instance, the (4x4) phase is often favored at lower temperatures (around 200-225°C), while other phases may appear at higher temperatures.<sup>[1][2]</sup></li><li>- Optimize the silicon deposition rate. A very low deposition rate (e.g., ~0.04 ML/min) is often preferred for controlled growth.</li><li>[1]- Ensure the Ag(111) substrate is meticulously cleaned before growth using multiple cycles of Ar+ sputtering and annealing.<sup>[1]</sup></li></ul> |

| STM images reveal a high density of point defects (vacancies).                                                                 | <ul style="list-style-type: none"><li>- The grown silicene superstructure is prone to defect formation.</li><li>- Non-optimal growth temperature or annealing procedure.</li></ul>                            | <ul style="list-style-type: none"><li>- Aim for the synthesis of the (4x4) silicene superstructure, which has been shown to have a lower concentration of point defects compared to the (<math>\sqrt{13} \times \sqrt{13}</math>) and (<math>2\sqrt{3} \times 2\sqrt{3}</math>) phases.<sup>[3][4][5][6]</sup></li><li>- Post-growth annealing can help to reduce defect density. The specific annealing temperature will depend on the silicene phase and substrate, but it should be high enough to promote atomic rearrangement without causing the silicene to decompose.</li></ul>                   |

---

|                                                                               |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Silicene layer appears disordered or forms 3D clusters instead of a 2D sheet. | <ul style="list-style-type: none"><li>- Substrate temperature is too low or too high.</li><li>- High residual gas pressure in the MBE chamber.</li><li>- Silicon coverage exceeding one monolayer.</li></ul>                                                  | <ul style="list-style-type: none"><li>- Maintain a precise substrate temperature during growth. Temperatures that are too low may not provide enough energy for Si atoms to form an ordered structure, while excessively high temperatures can lead to the desorption or clustering of Si atoms.<sup>[2]</sup></li><li>- Ensure ultra-high vacuum (UHV) conditions are maintained throughout the growth process to minimize contamination from residual gases like water, which can react with the growing silicene layer.<sup>[7]</sup></li><li>- Carefully control the silicon deposition to achieve monolayer coverage, as growth beyond one monolayer can favor the formation of 3D silicon structures.<sup>[8]</sup></li></ul> |

| Unexpected surface alloy formation is detected (e.g., with XPS).              | <ul style="list-style-type: none"><li>- A Si-Ag surface alloy is known to form at the interface and can act as a scaffold for silicene growth. This is not necessarily an impurity but a feature of the growth process on Ag(111).<sup>[8][9]</sup></li></ul> | <ul style="list-style-type: none"><li>- Characterize the interfacial alloy to understand its impact on the electronic properties of your silicene layer.</li><li>- Consider using an alternative substrate if the interaction with Ag is detrimental to your application.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

---

## Frequently Asked Questions (FAQs)

**Q1:** What are the most common types of impurities in silicene synthesis?

**A1:** Impurities in silicene synthesis can be broadly categorized into two types:

- Elemental Impurities: These are foreign atoms that contaminate the silicene lattice. Common sources include residual gases in the MBE chamber (like water or carbon monoxide) and contaminants from the silicon source or the substrate.[7]

- Structural Defects/Impurities: These are imperfections in the silicene honeycomb lattice. They include:

- Point Defects: Such as single or multiple atom vacancies.[3][4][5][6]

- Topological Defects: Like Stone-Wales defects, which involve the rotation of a Si-Si bond.

- Grain Boundaries: The interfaces between different domains of silicene.

- Mixed Superstructures (Phases): The coexistence of different silicene reconstructions (e.g., (4x4), ( $\sqrt{13}\times\sqrt{13}$ )) on the substrate, which can be considered a form of structural impurity.[10][11]

Q2: How critical is the substrate preparation for reducing impurities?

A2: Substrate preparation is one of the most critical steps in synthesizing high-quality silicene with low impurity levels. The Ag(111) substrate must be atomically clean and well-ordered. The standard procedure involves multiple cycles of Ar+ sputtering to remove surface contaminants, followed by annealing at high temperatures (e.g., 550°C) to restore a smooth, crystalline surface.[1] Any remaining surface impurities can act as nucleation sites for defects in the growing silicene layer.

Q3: What is the ideal substrate temperature and deposition rate for silicene growth on Ag(111)?

A3: The optimal substrate temperature and deposition rate are crucial for controlling the phase of the synthesized silicene. A substrate temperature in the range of 200-225°C and a low deposition rate of approximately 0.04 ML/second are often used to grow the desirable (4x4) phase of silicene on Ag(111).[1] It is important to note that different silicene phases have different stabilities depending on the temperature, so precise control is necessary to obtain a single-phase layer.[2]

Q4: Can post-growth annealing reduce the number of defects?

A4: Yes, post-growth annealing can be an effective method for reducing the density of grown-in defects in the silicene layer. The thermal energy allows atoms to diffuse and rearrange into a more ordered, lower-energy configuration, thereby healing some of the point defects and improving the overall crystalline quality. However, the annealing temperature and duration must be carefully optimized to avoid decomposition of the silicene or unwanted reactions with the substrate.

## Quantitative Data on Defect Formation

The formation of point defects is a significant source of impurities in epitaxial silicene. The stability and concentration of these defects can depend on the specific superstructure of the silicene.

| Defect Type                                                         | Silicene Superstructure on Ag(111) | Formation Energy Range (eV) | Estimated Defect Concentration (cm <sup>-2</sup> ) |

|---------------------------------------------------------------------|------------------------------------|-----------------------------|----------------------------------------------------|

| Stone-Wales (SW)                                                    | 4x4                                | 1.354 – 1.544               | Low                                                |

| ( $\sqrt{13} \times \sqrt{13}$ )                                    | 0.815 – 1.264                      | Higher than in 4x4          |                                                    |

| Single Vacancy (SV)                                                 | 4x4                                | ~1.5                        | $\sim 4.9 \times 10^7$                             |

| ( $\sqrt{13} \times \sqrt{13}$ ) & ( $2\sqrt{3} \times 2\sqrt{3}$ ) | as low as 0.052                    | $10^{13} - 10^{14}$         |                                                    |

| Double Vacancy (DV)                                                 | 4x4                                | ~1.5                        | $\sim 4.6 \times 10^5$                             |

| ( $\sqrt{13} \times \sqrt{13}$ ) & ( $2\sqrt{3} \times 2\sqrt{3}$ ) | as low as 0.08                     | $10^{13} - 10^{14}$         |                                                    |

Data synthesized from first-principles calculations.[\[4\]](#)[\[5\]](#)

The data clearly indicates that the 4x4 superstructure is significantly more robust against the formation of single and double vacancies compared to the ( $\sqrt{13} \times \sqrt{13}$ ) and ( $2\sqrt{3} \times 2\sqrt{3}$ ) phases, making it a more desirable phase for applications requiring high electronic mobility.[\[3\]](#)[\[4\]](#)[\[5\]](#)[\[6\]](#)

## Experimental Protocols

## Substrate Preparation: Cleaning of Ag(111) Crystal

This protocol describes the standard procedure for preparing an atomically clean Ag(111) substrate in an Ultra-High Vacuum (UHV) system.

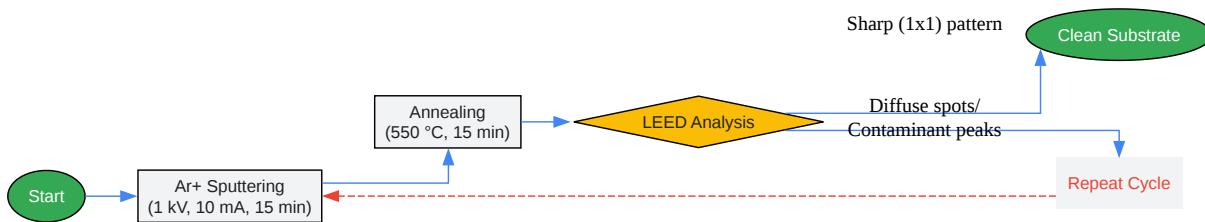

Workflow Diagram:

[Click to download full resolution via product page](#)

Caption: Workflow for Ag(111) substrate cleaning.

Methodology:

- Introduction into UHV: Mount the Ag(111) crystal onto a sample holder and introduce it into the UHV chamber.

- Sputtering: Perform Ar+ ion sputtering to remove the surface oxide layer and other contaminants. Typical parameters are an ion energy of 1 kV and a current of 10 mA for 15 minutes.<sup>[1]</sup>

- Annealing: Anneal the substrate to 550°C for 15 minutes. This step helps to recover the crystalline surface structure and desorb embedded Ar ions.<sup>[1]</sup>

- Surface Characterization: After cooling down, check the surface quality using Low-Energy Electron Diffraction (LEED). A sharp (1x1) LEED pattern with low background intensity indicates a clean and well-ordered surface.

- Repeat if Necessary: If the LEED pattern is not satisfactory, repeat the sputtering and annealing cycles until a high-quality surface is achieved.

## Silicene Synthesis via Molecular Beam Epitaxy (MBE)

This protocol outlines the epitaxial growth of a single-phase (4x4) silicene monolayer on a clean Ag(111) substrate.

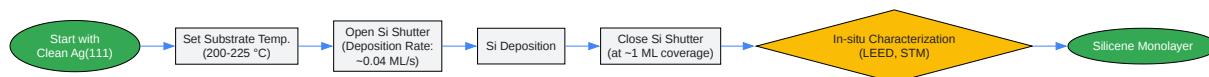

Workflow Diagram:

[Click to download full resolution via product page](#)

Caption: MBE workflow for silicene synthesis.

Methodology:

- Substrate Preparation: Prepare a clean Ag(111) substrate as described in the protocol above.

- Set Substrate Temperature: Heat the Ag(111) substrate to the desired deposition temperature, typically between 200°C and 225°C for the (4x4) phase.[1]

- Silicon Deposition: Open the shutter of the silicon effusion cell to begin the deposition of silicon onto the substrate. The deposition rate should be slow and well-controlled, around 0.04 ML/s.[1]

- Monitor Growth: Monitor the growth in real-time if possible, for example, using Reflection High-Energy Electron Diffraction (RHEED).

- Achieve Monolayer Coverage: Close the silicon shutter once approximately one monolayer of silicon has been deposited.

- In-situ Characterization: After the substrate has cooled, characterize the grown silicene layer using LEED and Scanning Tunneling Microscopy (STM) to confirm the desired (4x4) superstructure and assess the defect density.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. iris.cnr.it [iris.cnr.it]

- 2. researchgate.net [researchgate.net]

- 3. [1512.08860] Point defects in epitaxial silicene on Ag(111) surface [arxiv.org]

- 4. files01.core.ac.uk [files01.core.ac.uk]

- 5. researchgate.net [researchgate.net]

- 6. Item - Point defects in epitaxial silicene on Ag(111) surfaces - University of Wollongong - Figshare [ro.uow.edu.au]

- 7. researchgate.net [researchgate.net]

- 8. Epitaxial growth and structural properties of silicene and other 2D allotropes of Si - Nanoscale Advances (RSC Publishing) DOI:10.1039/D2NA00808D [pubs.rsc.org]

- 9. mediatum.ub.tum.de [mediatum.ub.tum.de]

- 10. coms.events [coms.events]

- 11. arxiv.org [arxiv.org]

- To cite this document: BenchChem. [how to reduce impurities during silicene synthesis]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b1259896#how-to-reduce-impurities-during-silicene-synthesis>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)