# Technical Support Center: Enhancing Silicene Quality Through Annealing

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Silicene*

Cat. No.: *B1259896*

[Get Quote](#)

This technical support center provides troubleshooting guidance and frequently asked questions for researchers, scientists, and drug development professionals working to enhance the quality of silicene through annealing processes.

## Troubleshooting Guides

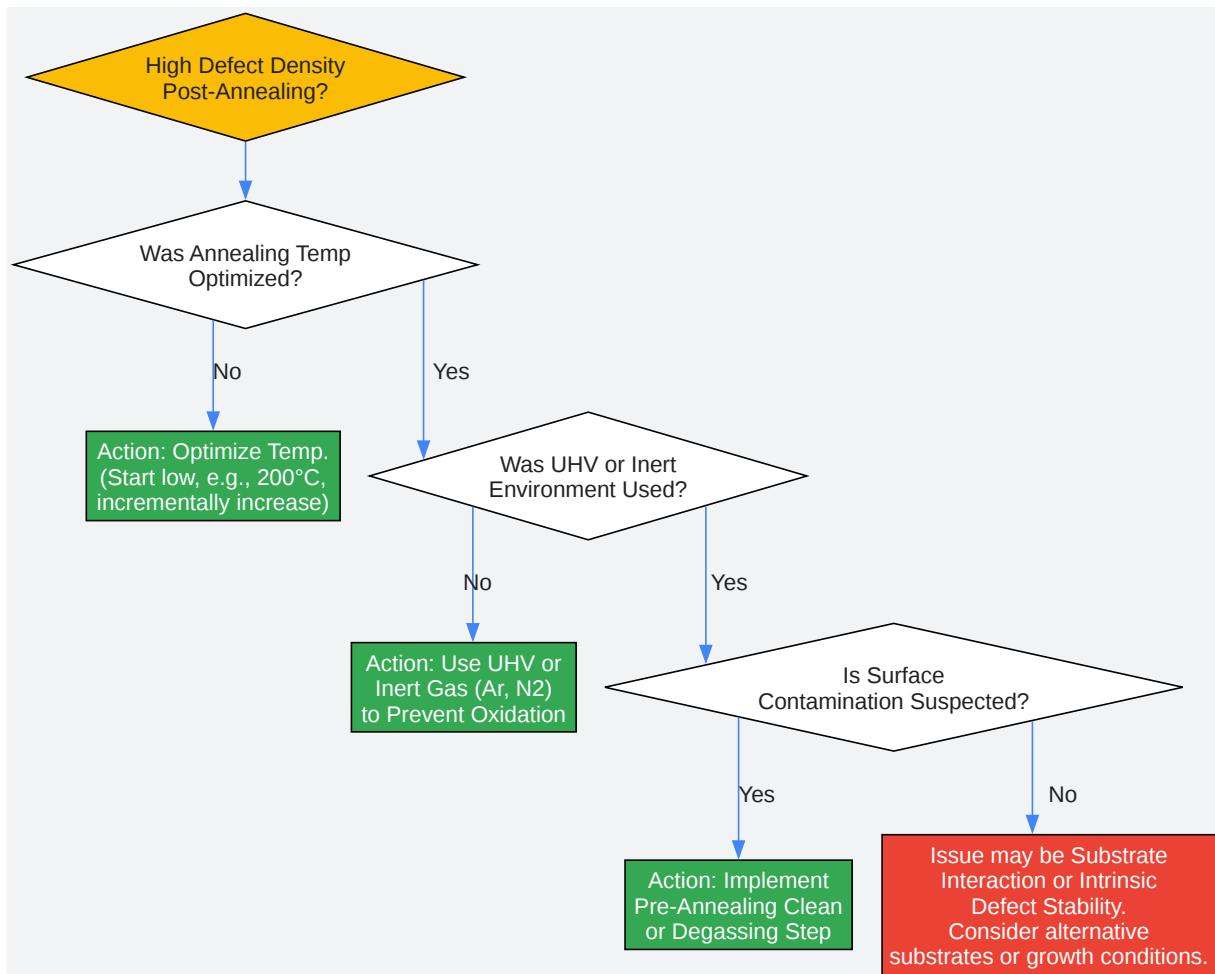

Issue: High Defect Density Observed After Silicene Synthesis

Question: My as-synthesized silicene shows a high defect density in characterization (e.g., high ID/IG ratio in Raman spectroscopy). How can I improve its quality?

Answer: A high defect density is a common issue in directly synthesized silicene. Post-synthesis annealing is a crucial step to reduce these defects. The thermal energy provided during annealing can facilitate the rearrangement of silicon atoms, healing vacancies and other structural imperfections. For instance, annealing in a vacuum or nitrogen environment has been shown to decrease the ID/IG ratio, indicating a reduction in defects.[\[1\]](#)

Question: What are the common types of defects in silicene, and can annealing address all of them?

Answer: Common defects in silicene include:

- Vacancies: Missing silicon atoms, which can cluster together.[\[2\]](#)[\[3\]](#)

- Stone-Wales (SW) defects: A pair of pentagonal and heptagonal rings formed by the rotation of a Si-Si bond.[4][5]

- Extended Line Defects: Linear arrangements of non-hexagonal rings.[2][3]

- Adatoms and Impurities: Unwanted atoms on the silicene surface.

Annealing is most effective at addressing point defects like vacancies by providing the energy for atoms to migrate and fill these empty sites. While it can help in the overall structural ordering, more complex defects like SW defects, which have a significant energy barrier to heal, may be more persistent even at high temperatures.[4][5]

**Issue: Inconsistent or Poor Results After Annealing**

**Question:** I've tried annealing my silicene samples, but the quality hasn't improved, or has even worsened. What could be going wrong?

**Answer:** Several factors can lead to suboptimal annealing results:

- Incorrect Annealing Temperature: The temperature needs to be high enough to promote atomic rearrangement but below the point of significant degradation or unwanted reactions with the substrate. Molecular dynamics simulations show that freestanding silicene can become unstable and start to disintegrate at temperatures around 1100-1500 K.[6] For silicene on a substrate, the optimal temperature can be influenced by the substrate material.

- Inappropriate Annealing Environment: The atmosphere during annealing is critical. Annealing in an ultra-high vacuum (UHV) is often preferred to prevent reactions with residual gases.[7] [8] Inert gas environments like nitrogen or argon can also be used.[1] An oxidizing environment will damage the silicene.

- Substrate Interaction: The interaction between silicene and the substrate can significantly affect the annealing process and the final quality. The substrate can induce strain or facilitate the formation of silicides at high temperatures.

- Contamination: Residues from the synthesis or transfer process (e.g., from polymers like PMMA) can interfere with the annealing process.[9][10] A pre-annealing cleaning step or a specific annealing protocol designed to remove contaminants may be necessary.

Question: My silicene appears to have degraded after high-temperature annealing. What is the maximum recommended annealing temperature?

Answer: The thermal stability of silicene depends on whether it is freestanding or on a substrate. Freestanding silicene is predicted to melt at temperatures ranging from 1200 to 3600 K in simulations.<sup>[6]</sup> Experimentally, for silicene grown on substrates like Ag(111), growth temperatures are typically in the range of 400-500 K.<sup>[8]</sup> Post-growth annealing to remove native oxides has been performed at approximately 780°C (1053 K) in UHV.<sup>[7]</sup> It is crucial to consult literature specific to your substrate and experimental setup, as excessive temperatures can lead to Si sublimation, island formation, or alloying with the substrate.

## Frequently Asked Questions (FAQs)

Q1: What is the primary purpose of annealing silicene?

A1: The primary goals of annealing silicene are to improve its crystalline quality by reducing structural defects, remove surface contaminants, and relieve internal stress.<sup>[11]</sup> This leads to enhanced electronic and structural properties.

Q2: How can I characterize the quality of my silicene before and after annealing?

A2: Raman spectroscopy is a powerful non-destructive technique. The intensity ratio of the D-peak (disorder-induced) to the G-peak (graphitic) (ID/IG) is a key indicator of defect density; a lower ratio signifies higher quality.<sup>[1]</sup> The position and width of the 2D peak also provide information about the electronic structure and strain.<sup>[9][12]</sup> Other valuable characterization techniques include Scanning Tunneling Microscopy (STM) for atomic-resolution imaging and Low-Energy Electron Diffraction (LEED) to assess crystalline order.<sup>[8]</sup>

Q3: What annealing environment (gas, pressure) is optimal?

A3: An ultra-high vacuum (UHV) environment (base pressure ~10-10 Torr) is generally ideal as it minimizes the risk of contamination and unwanted chemical reactions.<sup>[8]</sup> Annealing in an inert gas atmosphere, such as argon or nitrogen, can also be effective.<sup>[1]</sup> The choice depends on the specific goals and available equipment.

Q4: How long should I anneal my silicene samples?

A4: The optimal annealing duration depends on the temperature and the specific defects being targeted. Durations can range from a few minutes for rapid thermal annealing (RTA) to several hours for furnace annealing.[12][13] It is often an empirical parameter that needs to be optimized for your specific process.

Q5: Can annealing change the electronic properties of silicene?

A5: Yes. By reducing defects, annealing can improve charge carrier mobility. However, the interaction with the substrate, which can be modified by annealing, can also significantly alter the electronic band structure. For instance, strong hybridization with a metallic substrate can suppress the desired Dirac cone-like electronic dispersion.[14]

## Quantitative Data Summary

Table 1: Annealing Parameters from Literature

| Material/Substrate           | Annealing Temperature (°C) | Environment                    | Purpose/Observation                                               | Reference |

|------------------------------|----------------------------|--------------------------------|-------------------------------------------------------------------|-----------|

| Graphene on Si(100)          | ~300                       | Nitrogen, Vacuum               | Decrease in ID/IG ratio (defect reduction)                        | [1]       |

| Silicene on ZrB <sub>2</sub> | ~780                       | UHV                            | Removal of native oxides, formation of silicene layer             | [7]       |

| Silicene on Au(100)          | 150 (423 K)                | Not specified                  | Formation of surface silicene from Si clusters                    | [8]       |

| Graphene with Ni contacts    | 200-800                    | Argon                          | Resistance decreased above 300°C; contact degradation above 600°C | [12]      |

| Exfoliated Graphene          | 400                        | N <sub>2</sub> /H <sub>2</sub> | Removal of tape residues                                          | [15]      |

Table 2: Simulated Thermal Stability of Freestanding Silicene

| Simulation Parameter       | Temperature (K) | Observation                                               | Reference |

|----------------------------|-----------------|-----------------------------------------------------------|-----------|

| Onset of Vacancy Formation | ~1100           | Si particles begin to be ejected from their sites         | [6]       |

| Onset of Disintegration    | ≥ 1500          | Tearing apart of the silicene sheet                       | [6]       |

| Melting Temperature Range  | 1200 - 3600     | Varies significantly between different simulation studies | [6]       |

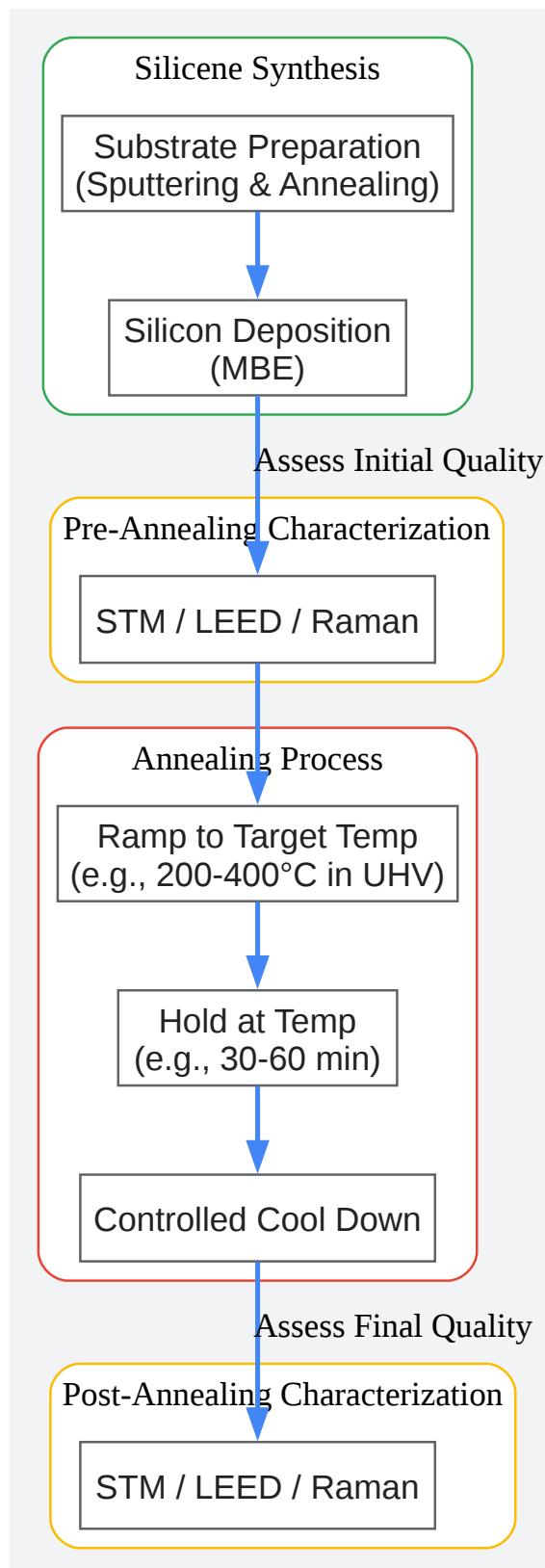

## Experimental Protocols

### Protocol 1: General Post-Synthesis Annealing of Silicene in UHV

- Sample Preparation: Synthesize silicene on a suitable substrate (e.g., Ag(111)) in a UHV chamber.

- Initial Characterization (Optional): If possible, perform in-situ characterization (e.g., STM, LEED) to assess the initial quality of the as-grown silicene.

- Ramping Up Temperature: Slowly ramp up the substrate temperature to the target annealing temperature (e.g., 200-400°C). A slow ramp rate helps prevent thermal shock.

- Annealing: Maintain the target temperature for the desired duration (e.g., 30-60 minutes). The pressure should be kept in the UHV range (< 10<sup>-9</sup> Torr).

- Cooling Down: Slowly ramp down the temperature to room temperature.

- Final Characterization: Perform post-annealing characterization (e.g., STM, LEED, ex-situ Raman spectroscopy) to evaluate the improvement in quality.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Experimental workflow for silicene synthesis and post-growth annealing.

[Click to download full resolution via product page](#)

Caption: Troubleshooting flowchart for suboptimal silicene annealing results.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Annealing effects on structure of the graphene directly synthesized on Si(100) - Institute of Materials Science | KTU [materials.ktu.edu]

- 2. Defects in Silicene: Vacancy Clusters, Extended Line Defects, and Di-adatoms - PMC [pmc.ncbi.nlm.nih.gov]

- 3. Defects in silicene: vacancy clusters, extended line defects, and Di-adatoms - PubMed [pubmed.ncbi.nlm.nih.gov]

- 4. researchgate.net [researchgate.net]

- 5. scispace.com [scispace.com]

- 6. researchgate.net [researchgate.net]

- 7. pubs.aip.org [pubs.aip.org]

- 8. Epitaxial growth and structural properties of silicene and other 2D allotropes of Si - Nanoscale Advances (RSC Publishing) DOI:10.1039/D2NA00808D [pubs.rsc.org]

- 9. Graphene annealing: how clean can it be? - PubMed [pubmed.ncbi.nlm.nih.gov]

- 10. The Effect of Annealing and Optical Radiation Treatment on Graphene Resonators - PMC [pmc.ncbi.nlm.nih.gov]

- 11. universitywafer.com [universitywafer.com]

- 12. Effect of High-Temperature Annealing on Graphene with Nickel Contacts | MDPI [mdpi.com]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Enhancing Silicene Quality Through Annealing]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b1259896#enhancing-the-quality-of-silicene-through-annealing-processes>

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)