# Silicene-Based FETs: Technical Support & Troubleshooting Center

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Silicene*

Cat. No.: *B1259896*

[Get Quote](#)

Welcome to the technical support center for researchers, scientists, and drug development professionals working with silicene-based Field-Effect Transistors (FETs). This guide provides troubleshooting information and frequently asked questions (FAQs) to address common challenges encountered during the synthesis, fabrication, and characterization of silicene devices.

## FAQ 1: Why is the measured carrier mobility in my silicene FET lower than theoretical predictions, and how can I improve it?

Answer: The theoretically predicted intrinsic carrier mobility of freestanding silicene is very high, potentially reaching up to  $2.57 \times 10^5 \text{ cm}^2/\text{Vs}$  for electrons at room temperature.<sup>[1]</sup> However, experimentally measured values are often significantly lower, typically around  $100 \text{ cm}^2/\text{Vs}$ .<sup>[2]</sup> This discrepancy arises from several extrinsic factors that introduce scattering and hinder carrier transport. Key factors include interactions with the substrate, structural defects, impurities introduced during fabrication, and scattering from phonons (lattice vibrations).<sup>[1][3][4]</sup>

### Troubleshooting Guide:

- Substrate Selection: The choice of substrate is critical as it can affect silicene's electronic properties.<sup>[5][6]</sup> While often grown on metallic substrates like Silver (Ag(111)), these interactions can suppress the desired electronic properties.<sup>[6]</sup> Using inert substrates like

hexagonal boron nitride (h-BN) or hydrogen-terminated silicon can help preserve silicene's characteristic Dirac cone.[5][7]

- Defect and Impurity Reduction: Defects in the silicene lattice and impurities from the fabrication process act as scattering centers for charge carriers.[8][9]

- Annealing: Perform vacuum annealing of the completed device. This can remove adsorbed molecules and contaminants from the silicene channel.[10] For other 2D materials, stepped annealing (e.g., up to 300 °C in an Argon atmosphere) has been shown to significantly improve device performance by reducing contaminants.[11]

- Clean Fabrication: Traditional lithography steps can introduce residues.[9] Whenever possible, use cleaner transfer and fabrication techniques to minimize exposure to polymers and solvents.

- Mobility Engineering Strategies: Advanced techniques can be employed to enhance carrier mobility.

- Strain Engineering: Applying mechanical strain can modulate the band structure and affect carrier effective mass, potentially improving mobility.

- Dielectric Engineering: Using high-k dielectrics can screen charged impurities, reducing their scattering effect and thereby improving mobility.

#### Experimental Protocol: Substrate and Annealing Optimization

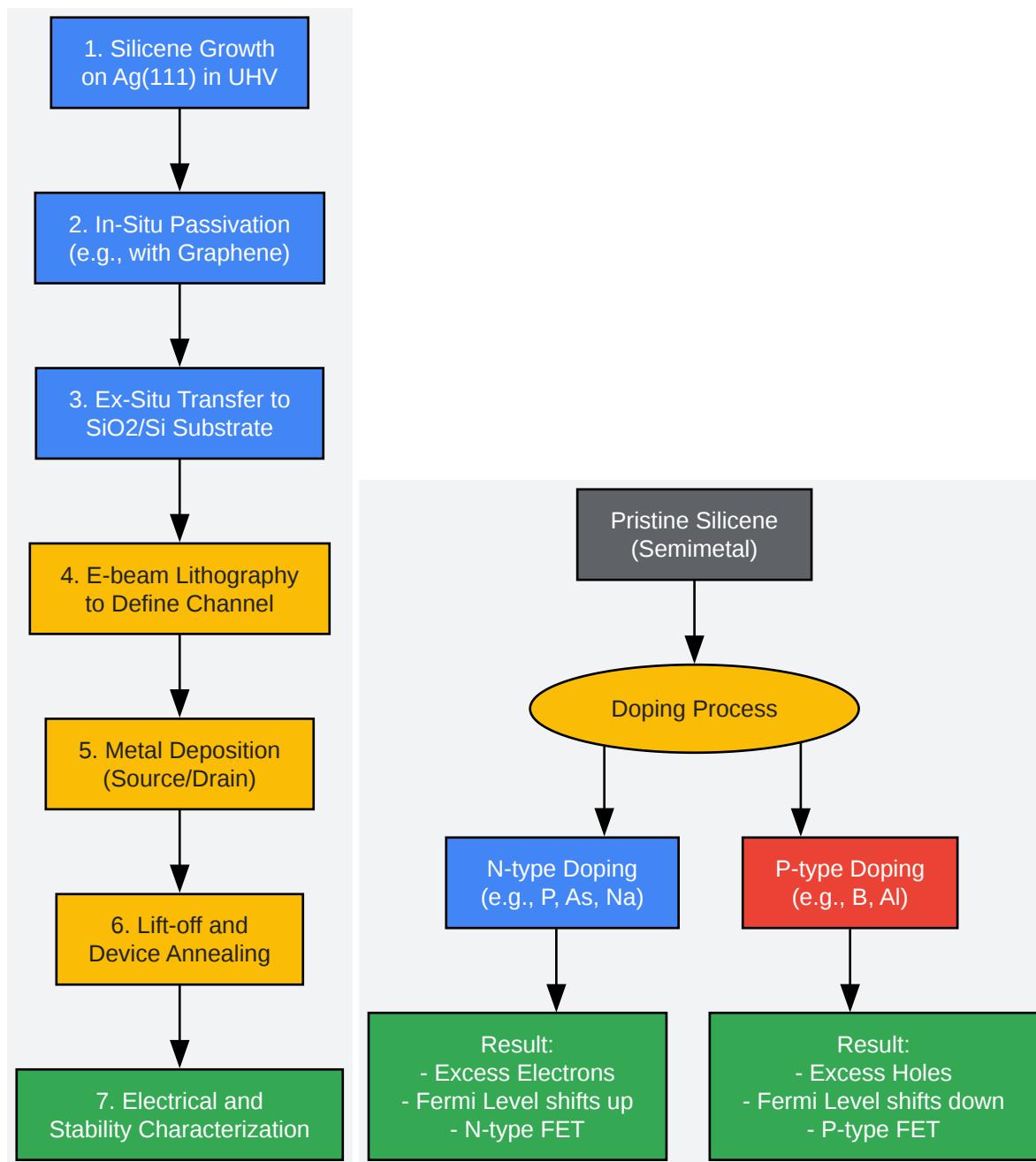

- Silicene Synthesis: Grow monolayer silicene on an Ag(111) substrate via molecular beam epitaxy (MBE) in an ultra-high vacuum (UHV) chamber.

- Transfer to Target Substrate:

- Transfer the synthesized silicene onto different substrates for comparison, such as the standard SiO<sub>2</sub>/Si and an h-BN flake exfoliated onto SiO<sub>2</sub>/Si.

- Use a well-established transfer method, such as a polymer-assisted transfer, ensuring minimal contamination.

- Device Fabrication: Fabricate back-gated FETs using standard electron-beam lithography to define source and drain contacts (e.g., Cr/Au).

- Post-Fabrication Annealing:

- Measure the initial transfer characteristics of the devices.

- Anneal the devices in a high-vacuum chamber ( $< 10^{-5}$  mbar) at a temperature of 150-200°C for several hours to remove adsorbed impurities.

- Re-measure the electrical characteristics to evaluate the impact of annealing.

- Characterization: Extract the field-effect mobility from the linear region of the transfer curve ( $I_D$  vs.  $V_G$ ) using the standard formula. Compare the mobility values obtained on different substrates before and after annealing.

#### Data Presentation: Carrier Mobility Comparison

| 2D Material      | Substrate            | Theoretical Mobility (cm <sup>2</sup> /Vs) | Experimental Mobility (cm <sup>2</sup> /Vs) |

|------------------|----------------------|--------------------------------------------|---------------------------------------------|

| Silicene         | Freestanding         | $\sim 2.6 \times 10^5$ <sup>[1]</sup>      | N/A                                         |

| Silicene         | SiO <sub>2</sub> /Si | -                                          | $\sim 100$ <sup>[2]</sup>                   |

| Graphene         | Freestanding         | $>10^5$                                    | High                                        |

| Graphene         | h-BN                 | High                                       | Up to 140,000                               |

| MoS <sub>2</sub> | SiO <sub>2</sub> /Si | $\sim 200-500$                             | 0.4 - 39 <sup>[12]</sup>                    |

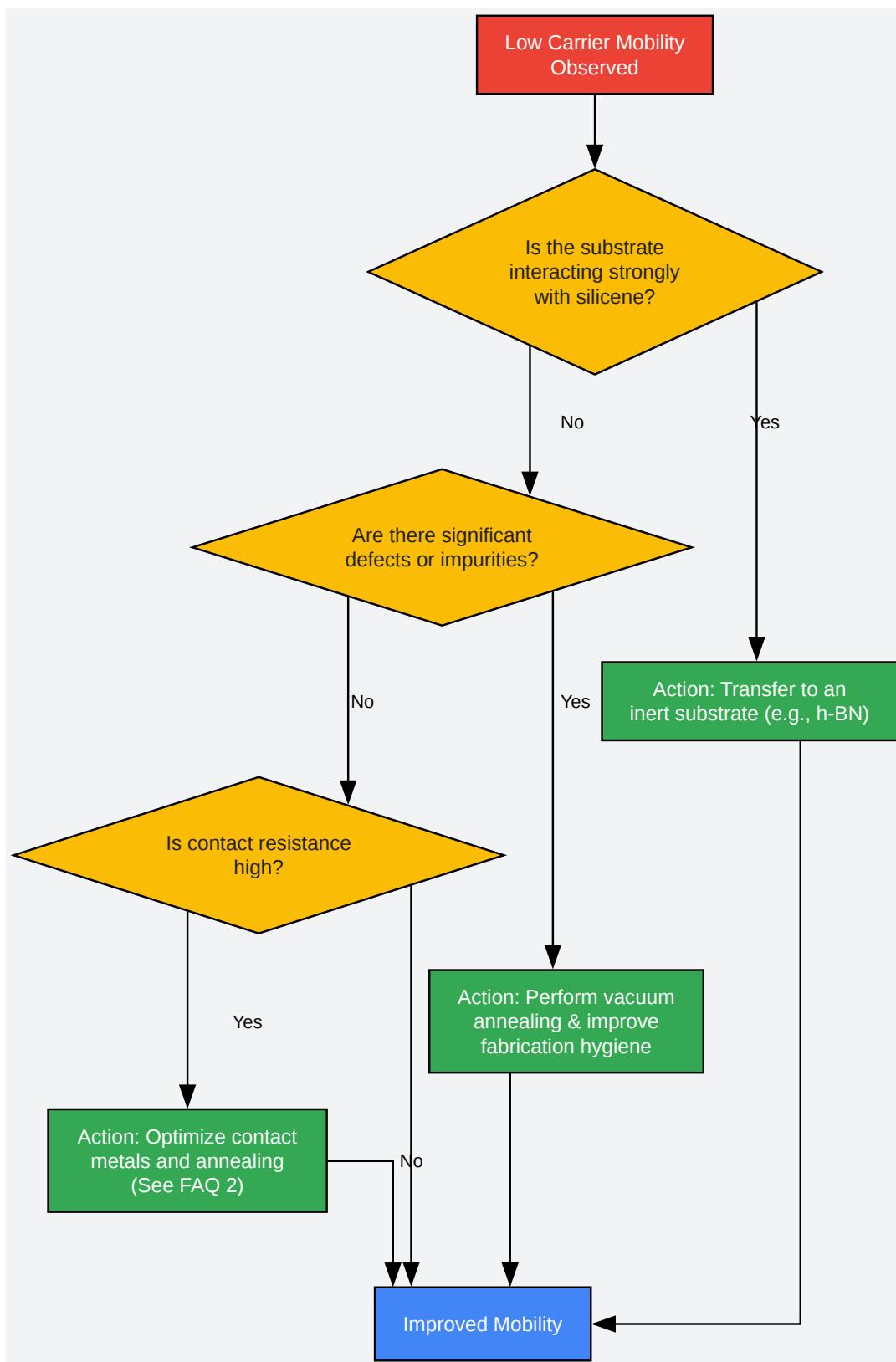

#### Troubleshooting Workflow for Low Carrier Mobility

[Click to download full resolution via product page](#)

A flowchart for diagnosing and resolving low carrier mobility in silicene FETs.

## FAQ 2: What causes high contact resistance in silicene FETs, and how can it be reduced?

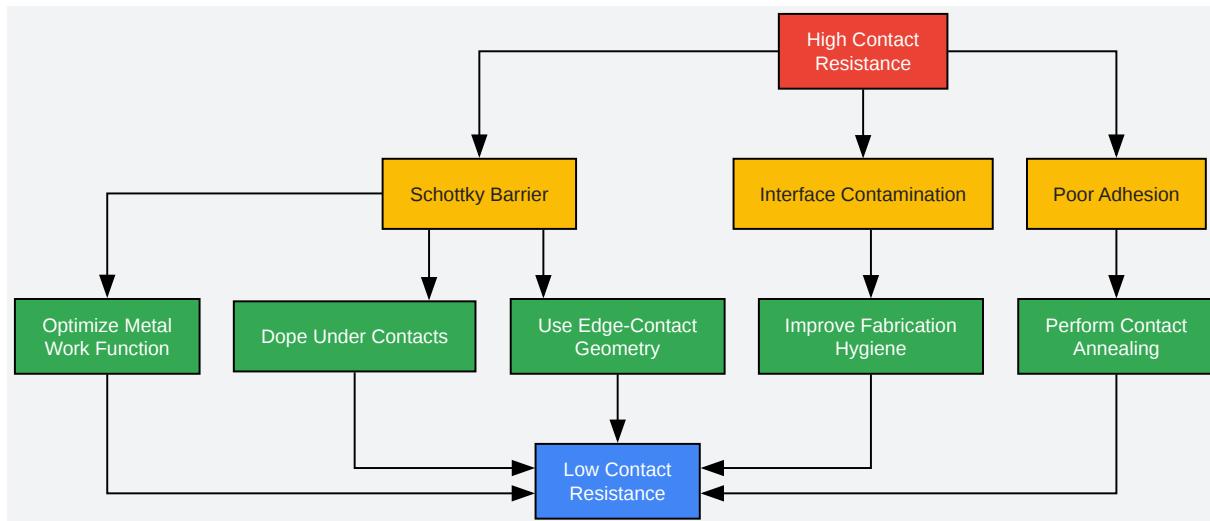

Answer: High contact resistance ( $R_c$ ) at the metal-silicene interface is a primary bottleneck for achieving high-performance devices.[\[3\]](#)[\[12\]](#) It can dominate the total device resistance, masking the intrinsic properties of the silicene channel. Causes include:

- Schottky Barrier: A significant energy barrier can form at the interface between the metal contacts and the silicene, impeding charge carrier injection.

- Poor Adhesion/Wetting: Weak bonding between the deposited metal and the silicene surface can lead to high  $R_c$ .

- Interface Contamination: Residues from the fabrication process can create a resistive layer at the contact interface.[\[13\]](#)

- Current Crowding: In top-contact geometries, current preferentially injects near the edge of the contact, limiting the effective contact area.[\[14\]](#)

### Troubleshooting Guide:

- Contact Metal Selection: Choose metals with work functions that align with the conduction or valence band of silicene to minimize the Schottky barrier height. Low work function metals (e.g., Sc, Y) are better for n-type contacts, while high work function metals (e.g., Pt, Pd, Au) are preferred for p-type contacts.

- Interface Engineering:

- Doping under Contacts: Selectively dope the silicene region under the contacts to reduce the width of the Schottky barrier, allowing for more efficient tunneling. Chemical doping has been shown to reduce  $R_c$  in MoS<sub>2</sub> FETs to as low as 0.5 kΩ·μm.[\[15\]](#)

- Tunneling Layer: Insert an ultra-thin insulating layer (e.g., h-BN, TiO<sub>2</sub>) between the metal and silicene. This can depin the Fermi level and reduce the Schottky barrier, promoting carrier injection via tunneling.

- Contact Annealing: Annealing the device after metal deposition can improve adhesion and promote the formation of carbides or silicides at the interface, which can lead to lower  $R_c$ . Stepped annealing has been shown to reduce contact resistance in  $\text{MoS}_2$  FETs from over 200  $\text{k}\Omega\cdot\mu\text{m}$  to 4.7  $\text{k}\Omega\cdot\mu\text{m}$ .[11]

- Contact Geometry: Fabricate "edge-contacted" structures where the metal directly contacts the one-dimensional edge of the silicene sheet. This has been shown to significantly reduce contact resistance in graphene devices.[14]

#### Data Presentation: Contact Resistance for Different Metals on 2D Materials

| Metal Contact | 2D Material              | Contact Resistance ( $\Omega\cdot\mu\text{m}$ ) | Notes                                        |

|---------------|--------------------------|-------------------------------------------------|----------------------------------------------|

| Pd            | Graphene                 | 100 - 300                                       | Common, good performance.                    |

| Ni            | Graphene                 | < 200                                           | Can form good edge contacts.                 |

| Cr/Au         | Graphene/ $\text{MoS}_2$ | > 1k                                            | Adhesion layer (Cr) can increase resistance. |

| Sc            | $\text{MoS}_2$           | ~200                                            | Good n-type contact.                         |

| Ti/Au         | $\text{MoS}_2$           | 740 - 1.5k                                      | Widely used but not always optimal.          |

#### Logic Diagram: Reducing Contact Resistance

[Click to download full resolution via product page](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. [1705.04025] The role of contact resistance in graphene field-effect devices [arxiv.org]

- 4. researchgate.net [researchgate.net]

- 5. pubs.acs.org [pubs.acs.org]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. allaboutcircuits.com [allaboutcircuits.com]

- 10. Bending Stability of Ferroelectric Gated Graphene Field Effect Transistor for Flexible Electronics - PMC [pmc.ncbi.nlm.nih.gov]

- 11. Reducing MoS2 FET contact resistance by stepped annealing to optimize device performance - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 12. Strategic Mobility Engineering in 2D Semiconductor-based FETs for Enhanced Electronic Devices - PMC [pmc.ncbi.nlm.nih.gov]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Silicene-Based FETs: Technical Support & Troubleshooting Center]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1259896#optimizing-the-performance-of-silicene-based-fets>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)