# Technical Support Center: Reducing Crystal Defects in Gallium Arsenide (GaAs) Wafers

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Gallium arsenate*

Cat. No.: *B1256347*

[Get Quote](#)

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in reducing crystal defects in Gallium Arsenide (GaAs) wafers.

## Troubleshooting Guides

This section offers step-by-step guidance to address common issues related to crystal defects in GaAs wafers.

### Issue 1: High Dislocation Density Observed After Crystal Growth

Q1: My recently grown Vertical Gradient Freeze (VGF) GaAs wafer shows a high etch pit density (EPD) after molten KOH etching. What are the potential causes and how can I reduce the dislocation density?

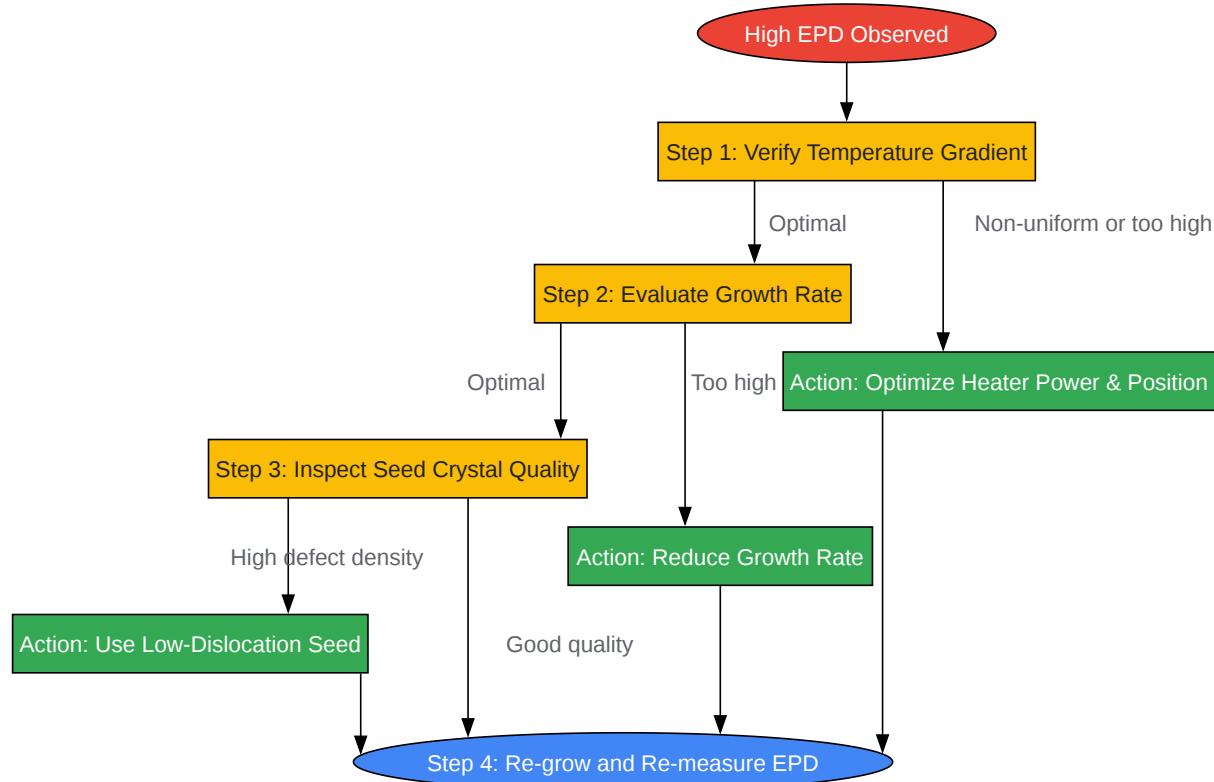

A1: A high EPD in VGF-grown GaAs wafers is typically a result of thermal stress during the crystal growth process. Here is a troubleshooting workflow to identify and mitigate the issue:

Troubleshooting Workflow for High Dislocation Density in VGF-grown GaAs

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for high dislocation density.

Detailed Steps:

- Verify Temperature Gradient: The temperature gradient across the solid-liquid interface is a critical factor. An excessive or non-uniform temperature gradient can induce thermal stress, leading to dislocation formation.<sup>[1]</sup> Industrial VGF processes typically operate with

temperature gradients in the range of 2-10 K/cm in the melt and up to 15 K/cm in the crystal.

[2]

- Action: Review and optimize the power output and positioning of the heaters to achieve a more uniform and gentle thermal gradient.[2][3]

- Evaluate Growth Rate: A high crystal growth rate can also contribute to the generation of dislocations. Typical growth rates for VGF-grown GaAs are in the range of 2-4 mm/h.[2]

- Action: Try reducing the crystal pulling speed to minimize stress.

- Inspect Seed Crystal Quality: Dislocations present in the seed crystal can propagate into the newly grown ingot.

- Action: Ensure that you are using a high-quality seed crystal with a low dislocation density.

- Re-grow and Re-measure EPD: After implementing the corrective actions, grow a new crystal and evaluate the EPD using the molten KOH etching protocol.

## Issue 2: Stacking Faults Detected in MOCVD-Grown Epitaxial Layers

Q2: I am observing stacking faults in my Metal-Organic Chemical Vapor Deposition (MOCVD) grown GaAs epitaxial layers. What are the common causes and how can I eliminate them?

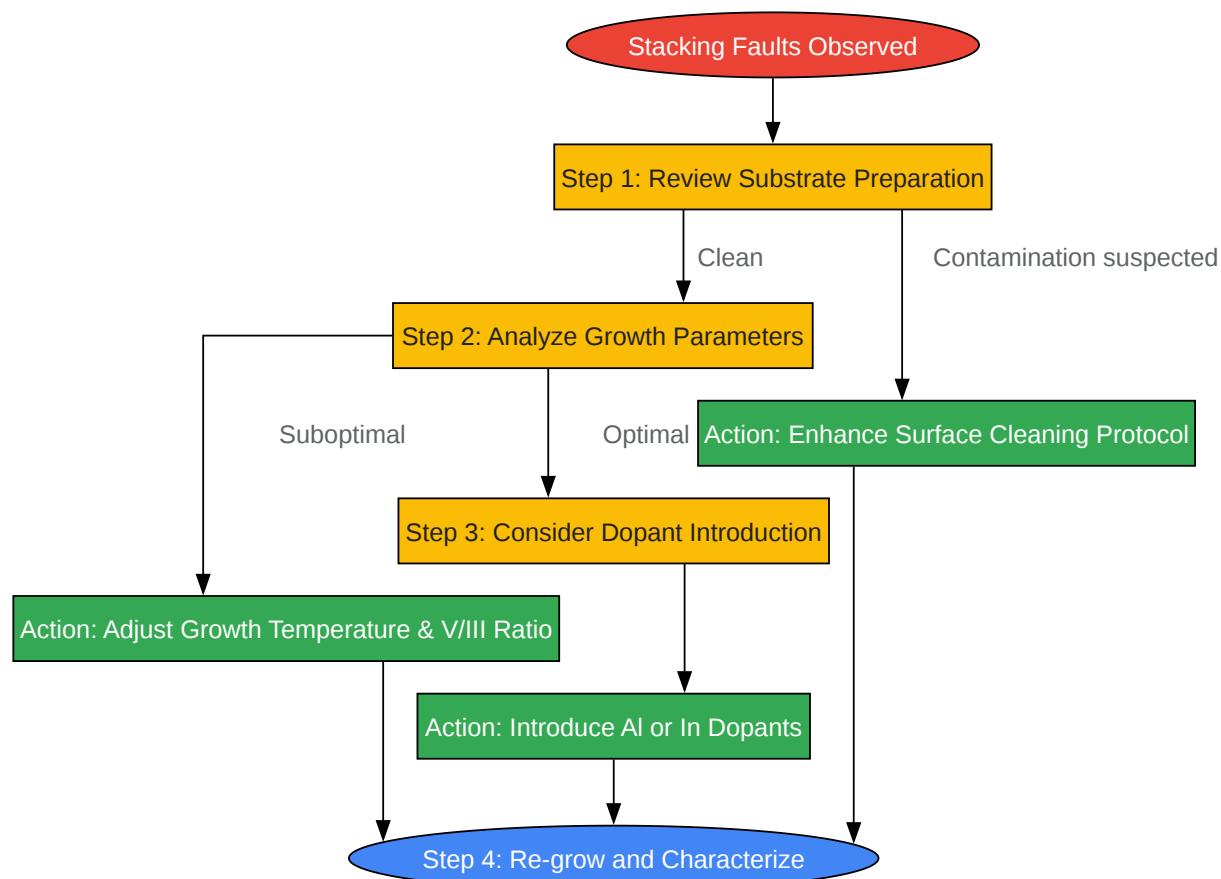

A2: Stacking faults in MOCVD-grown layers often originate from substrate surface contamination or suboptimal growth conditions. The following workflow can help you troubleshoot this issue:

Troubleshooting Workflow for Stacking Faults in MOCVD-grown GaAs

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for stacking faults.

Detailed Steps:

- **Review Substrate Preparation:** The most common cause of stacking faults is contamination on the substrate surface. This can include particulate matter or residual oxides.

- Action: Enhance your substrate cleaning procedure. This may involve a more rigorous solvent clean, an optimized acid etch to remove the native oxide, and ensuring a clean-room environment with minimal particle count.

- Analyze Growth Parameters: Suboptimal growth temperature or V/III ratio (the ratio of Group V to Group III precursors) can lead to the formation of stacking faults.

- Action: Experiment with adjusting the growth temperature and V/III ratio. A systematic study varying these parameters can help identify the optimal growth window for your specific MOCVD reactor.

- Consider Dopant Introduction: The addition of certain dopants, such as Aluminum (Al) and Indium (In), during film growth has been shown to reduce the density of stacking faults.[\[4\]](#)[\[5\]](#)

- Action: If your device structure allows, consider introducing a small amount of Al or In during the initial stages of growth.

- Re-grow and Characterize: After making adjustments, grow a new epitaxial layer and characterize it for the presence of stacking faults using techniques like Transmission Electron Microscopy (TEM) or defect-selective etching.

## Frequently Asked Questions (FAQs)

Q3: What are the common types of crystal defects in GaAs wafers?

A3: Common crystal defects in GaAs wafers include:

- Point Defects: These are zero-dimensional defects and include vacancies (a missing atom), interstitials (an extra atom in a non-lattice position), and antisite defects (a Ga atom on an As site, or vice-versa).

- Dislocations: These are one-dimensional defects that represent a disruption in the crystal lattice.

- Stacking Faults: These are two-dimensional defects that are an error in the stacking sequence of atomic planes.

- Twins and Polycrystalline Defects: These are regions where the crystal orientation changes.

Q4: How do these defects affect the performance of my devices?

A4: Crystal defects can have a significant negative impact on device performance. They can act as scattering centers for charge carriers, reducing mobility. They can also serve as non-radiative recombination centers, which lowers the efficiency of optoelectronic devices like LEDs and lasers. In high-frequency electronic devices, defects can introduce noise and limit performance.

Q5: What is Etch Pit Density (EPD) and how is it measured?

A5: Etch Pit Density (EPD) is a measure of the dislocation density in a semiconductor wafer. It is determined by etching the wafer with a chemical that preferentially attacks the strained regions around dislocations, forming pits that can be observed and counted under a microscope.<sup>[6]</sup> The EPD is then calculated by dividing the number of pits by the area of the field of view.<sup>[6]</sup>

Q6: Can you provide a table of typical EPD values for different grades of GaAs wafers?

A6: Yes, the table below provides typical EPD values for various GaAs wafer types.

| Wafer Type      | Growth Method | Dopant  | Typical EPD (/cm <sup>2</sup> ) |

|-----------------|---------------|---------|---------------------------------|

| n-type          | VGF / VB      | Si      | <5000                           |

| p-type          | VGF           | Zn      | <5000                           |

| Semi-insulating | VGF           | Undoped | <5000                           |

Data sourced from Precision Micro-Optics.<sup>[7]</sup>

Q7: How can I use Photoluminescence (PL) to identify defects in my GaAs wafer?

A7: Photoluminescence (PL) is a non-destructive optical technique that can be used to identify certain defects in GaAs. When a laser excites the material, electrons are promoted to higher energy states. As they relax, they can emit light. Defects can introduce energy levels within the bandgap, leading to characteristic emission peaks at specific energies. By analyzing the PL spectrum, you can identify the presence of these defects.

Q8: Can you provide a table of common PL peaks and their corresponding defects in GaAs?

A8: The following table lists some commonly observed PL emission peaks in GaAs at low temperatures (77K) and their likely origins.

| Emission Peak (eV) | Wavelength (nm) | Corresponding Defect/Transition     |

|--------------------|-----------------|-------------------------------------|

| 1.496              | 829             | Associated with VGa-related defects |

| 1.476              | 840             | GaAs antisite defects               |

| 1.470              | 843             | Associated with VGa-related defects |

| 1.458              | 850.5           | Associated with VGa-related defects |

| 1.452              | 854             | GaAs antisite defects               |

| 1.372              | 904             | As vacancy related defects          |

| 1.326              | 935             | GaAs antisite defects               |

| 1.289              | 962             | As vacancy related defects          |

Data compiled from multiple sources.[\[8\]](#)[\[9\]](#)

## Experimental Protocols

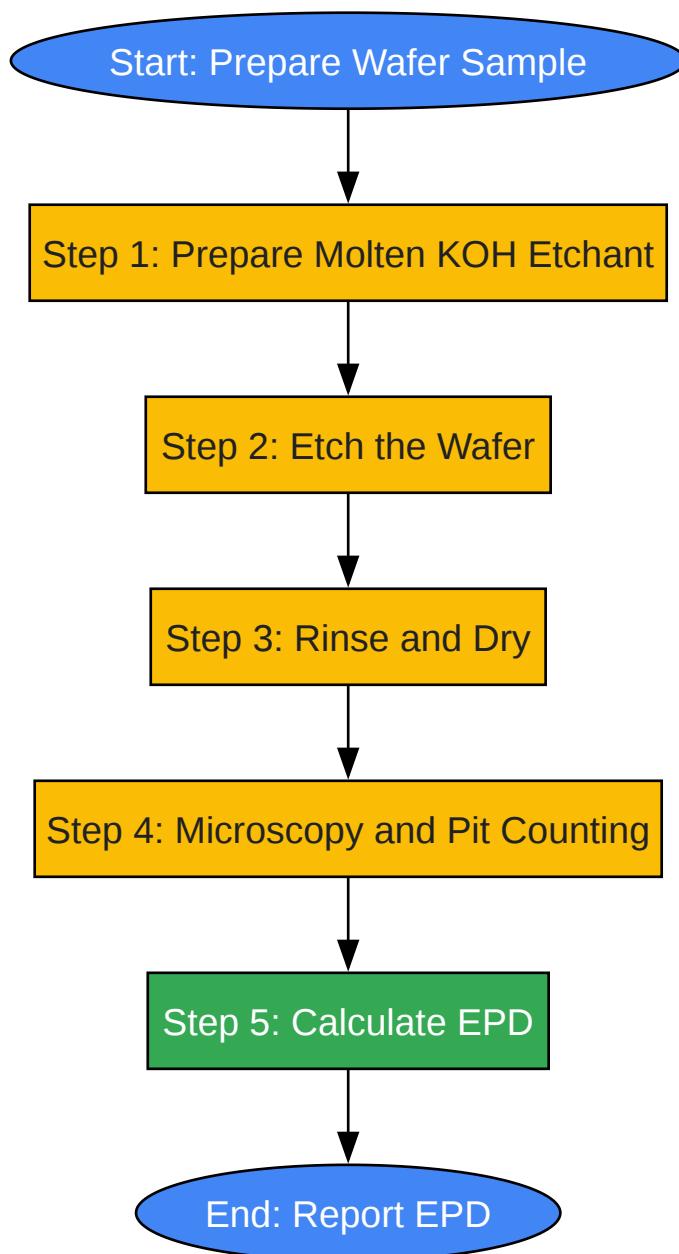

### Protocol 1: Molten KOH Etching for Dislocation Density (EPD) Measurement

This protocol outlines the procedure for revealing dislocation etch pits on a {100} GaAs wafer surface using molten potassium hydroxide (KOH).

Experimental Workflow for Molten KOH Etching

[Click to download full resolution via product page](#)

Caption: Workflow for EPD measurement using molten KOH etching.

Materials and Equipment:

- GaAs wafer sample

- Potassium hydroxide (KOH) pellets

- Nickel or graphite crucible

- High-temperature furnace or hot plate

- Tweezers (Teflon or stainless steel)

- Deionized (DI) water

- Optical microscope with a calibrated field of view

**Procedure:**

- Prepare Molten KOH Etchant:

- Safety First: Molten KOH is extremely corrosive. Always wear appropriate personal protective equipment (PPE), including safety glasses, a face shield, and heat-resistant gloves. Perform this procedure in a fume hood.

- Place KOH pellets in the crucible.

- Heat the crucible in the furnace or on a hot plate to 350-450°C to melt the KOH. The presence of some water from crystallohydrates in the KOH is necessary for selective etching.[10]

- Etch the Wafer:

- Using tweezers, carefully immerse the GaAs wafer into the molten KOH.

- Etch for approximately 30 minutes at 350°C.[11] The etch rate is about 0.08 µm/min.[11]

- Rinse and Dry:

- Carefully remove the wafer from the molten KOH and allow it to cool for a few moments.

- Quench the etching process by immersing the wafer in a beaker of DI water.

- Rinse the wafer thoroughly with DI water to remove any residual KOH.

- Dry the wafer with a gentle stream of nitrogen.

- Microscopy and Pit Counting:

- Place the etched wafer on the microscope stage.

- Using a magnification that allows for clear visualization of the etch pits, count the number of pits within a defined field of view. For 2-inch wafers, a grid with 5 mm side lengths is often used, with counts taken at the center of each grid.[6]

- Calculate EPD:

- Calculate the area of your microscope's field of view.

- The Etch Pit Density (EPD) is calculated as:  $EPD \text{ (pits/cm}^2\text{)} = (\text{Number of pits counted}) / (\text{Area of the field of view in cm}^2)$

- Repeat the counting and calculation for multiple areas on the wafer to get an average EPD.

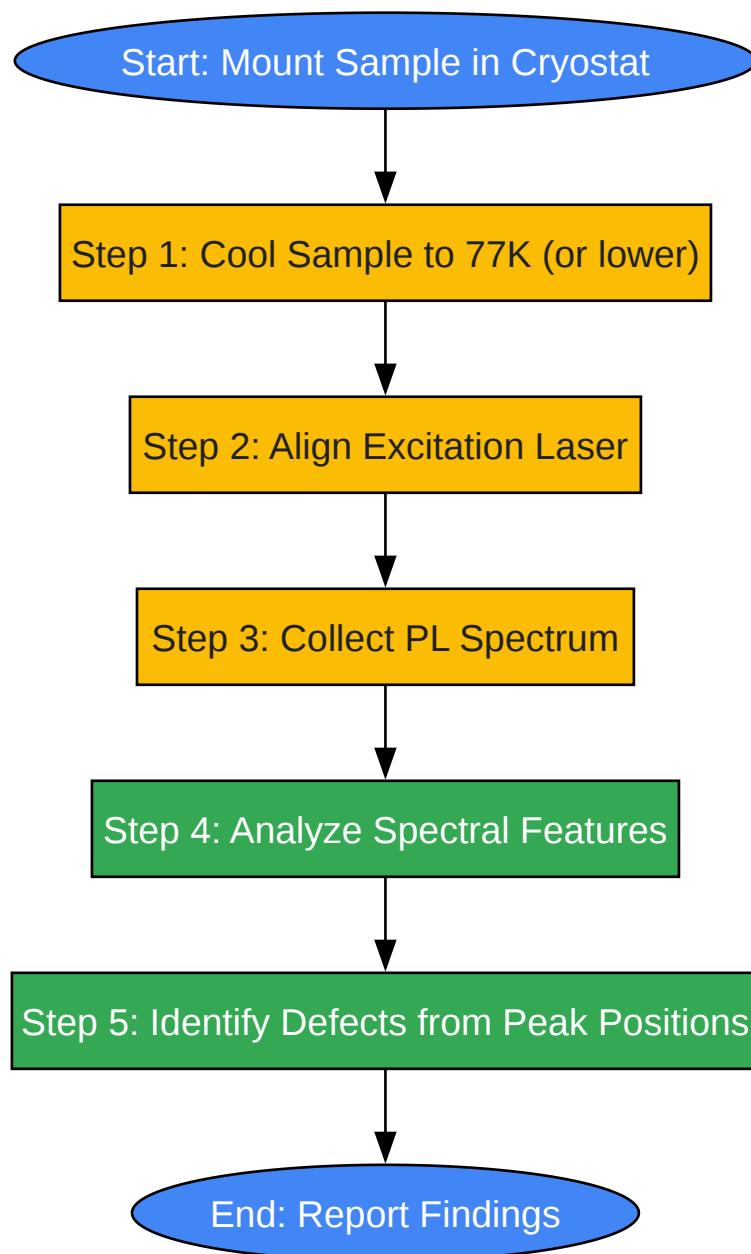

## Protocol 2: Photoluminescence (PL) Spectroscopy for Defect Characterization

This protocol provides a general methodology for performing photoluminescence spectroscopy on a GaAs wafer to identify defect-related emissions.

### Experimental Workflow for Photoluminescence Spectroscopy

[Click to download full resolution via product page](#)

Caption: Workflow for defect characterization using PL.

Materials and Equipment:

- GaAs wafer sample

- Cryostat for low-temperature measurements (e.g., liquid nitrogen cooled to 77K)

- Excitation laser (e.g., He-Ne laser at 632.8 nm or a diode laser with energy above the GaAs bandgap)

- Focusing and collection optics

- Spectrometer

- Detector sensitive to the near-infrared region (e.g., a silicon or InGaAs detector)

**Procedure:**

- Sample Mounting and Cooling:

- Mount the GaAs wafer on the cold finger of the cryostat.

- Evacuate the cryostat and cool the sample to the desired temperature, typically 77K, to reduce thermal broadening of the PL peaks.

- Laser Alignment:

- Align the excitation laser to focus on the desired area of the wafer. The laser spot size can be adjusted using the focusing optics.

- Spectrum Collection:

- Direct the emitted photoluminescence into the spectrometer using the collection optics.

- Acquire the PL spectrum over the desired wavelength range. The integration time will depend on the signal intensity.

- Spectral Analysis:

- Identify the different emission peaks in the collected spectrum.

- Determine the peak position (in eV or nm) and the full width at half maximum (FWHM) for each peak.

- Defect Identification:

- Compare the energies of the observed emission peaks to the known energies of defect-related transitions in GaAs (refer to the table in Q8). This will help in identifying the types of defects present in your sample.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. mdpi.com [mdpi.com]

- 2. Development and Optimization of VGF-GaAs Crystal Growth Process Using Data Mining and Machine Learning Techniques | MDPI [mdpi.com]

- 3. researchgate.net [researchgate.net]

- 4. Stacking fault asymmetry in epitaxial films of mocvd znse/gaas(001) for Philosophical Magazine A: Physics of Condensed Matter, Structure, Defects and Mechanical Properties - IBM Research [research.ibm.com]

- 5. research.monash.edu [research.monash.edu]

- 6. powerwaywafer.com [powerwaywafer.com]

- 7. optics - Gallium Arsenide Wafers [pmoptics.com]

- 8. Low temperature photoluminescence study of GaAs defect states [cpb.iphy.ac.cn]

- 9. pubs.acs.org [pubs.acs.org]

- 10. Analysis of factors influencing the process of selective etching of the {100} monocrystalline GaAs surface to determine the dislocation density | Verbitsky | Industrial laboratory. Diagnostics of materials [zldm.ru]

- 11. KOH:NaOH - GaAs - Wet Etchant by Chemical Composition [steeldata.info]

- To cite this document: BenchChem. [Technical Support Center: Reducing Crystal Defects in Gallium Arsenide (GaAs) Wafers]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1256347#reducing-crystal-defects-in-gallium-arsenide-wafers>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)