# Technical Support Center: Epitaxial Growth of GaAs Layers

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Gallium arsenate

Cat. No.: B1256347

[Get Quote](#)

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to address common issues encountered during the epitaxial growth of Gallium Arsenide (GaAs) layers. The information is tailored for researchers, scientists, and professionals in drug development who utilize GaAs-based devices.

## Frequently Asked Questions (FAQs)

**Q1:** What are the most common types of defects observed in epitaxial GaAs layers?

**A1:** The most prevalent defects in epitaxial GaAs layers include:

- Oval Defects: Elliptical or circular surface imperfections.[1][2][3]

- Dislocations: Line defects within the crystal structure, such as threading and misfit dislocations.[4][5]

- Stacking Faults: Planar defects arising from errors in the sequence of atomic layers.

- Surface Morphology Defects: Irregularities on the surface like hillocks, pits, and surface roughness.

**Q2:** How does substrate preparation affect the quality of the grown GaAs layer?

**A2:** Substrate preparation is a critical step that significantly influences the quality of the epitaxial layer. Improper preparation can lead to the formation of various defects. Key aspects

include:

- Contamination: Particulates or chemical residues on the substrate surface can act as nucleation sites for oval defects and other imperfections.[2][6]

- Native Oxide: A thin layer of native oxide on the GaAs substrate must be effectively removed before growth to ensure proper nucleation and prevent defect formation.

- Surface Roughness: An atomically smooth substrate surface is essential for achieving high-quality epitaxial growth. Chemical etching procedures are often employed to prepare the substrate surface.

**Q3: What is the impact of V/III ratio on the growth of III-V semiconductors?**

**A3:** The V/III ratio, which is the ratio of the flux of group V elements (like Arsenic) to group III elements (like Gallium), is a crucial parameter in both Molecular Beam Epitaxy (MBE) and Metal-Organic Chemical Vapor Deposition (MOCVD). It affects the surface reconstruction, growth rate, and incorporation of impurities and defects. An optimal V/III ratio is necessary for achieving a smooth surface morphology and high crystal quality. For instance, in the MOCVD growth of GaSb on GaAs, a V/III ratio of 2.5 resulted in the lowest surface roughness compared to ratios of 1.25 and 5.[7] In the case of AlGaSb layers grown on GaAs, the growth rate increases with the V/III ratio up to a certain point, after which it starts to decrease due to a site-blocking effect by excess antimony molecules.[8]

## Troubleshooting Guides

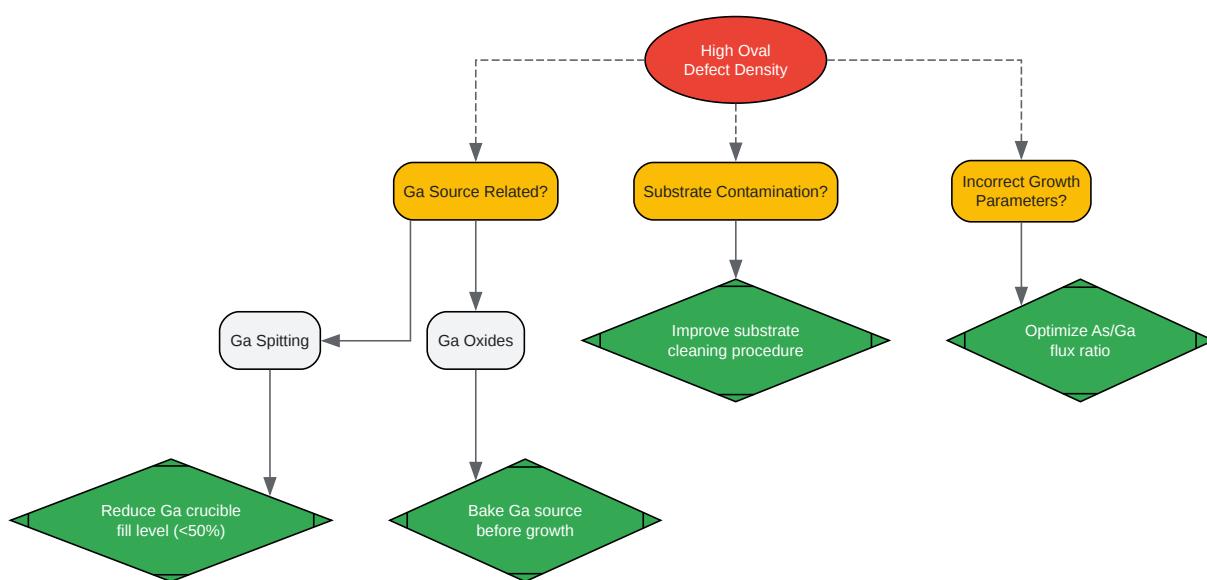

### Issue 1: High Density of Oval Defects

**Q:** My GaAs layer, grown by MBE, shows a high density of oval defects. What are the potential causes and how can I mitigate this issue?

**A:** Oval defects are a common problem in MBE-grown GaAs. Their origin can be traced to several factors.

Potential Causes:

- Gallium (Ga) Source:

- Ga Spitting: Ejection of small Ga droplets from the effusion cell. This can be exacerbated when the crucible is filled to its maximum capacity.[9]

- Gallium Oxides: Volatile oxides like  $\text{Ga}_2\text{O}$  can form in the Ga crucible and subsequently deposit on the substrate, acting as nucleation sites for defects.[6]

- Substrate Contamination: Particulates on the substrate surface prior to growth.[2][6]

- Growth Conditions:

- As<sub>4</sub>/Ga Flux Ratio: An improper arsenic to gallium flux ratio can lead to the formation of small oval defects. There is a narrow range for this ratio that can help in eliminating these defects.[9]

- Substrate Temperature: The substrate temperature can influence the nucleation mechanism of these defects.[1]

#### Troubleshooting Steps:

- Optimize Ga Cell Conditions:

- Avoid overfilling the Ga crucible; using less than half the crucible volume can significantly decrease oval defect density.[9]

- Bake the Ga source at a high temperature before growth to reduce volatile oxides.

- Improve Substrate Preparation:

- Ensure a meticulous chemical cleaning process to remove any surface contaminants.

- Handle substrates in a clean environment (e.g., under a laminar flow hood) to prevent particulate contamination during loading.[9]

- Optimize Growth Parameters:

- Fine-tune the As<sub>4</sub>/Ga flux ratio. A ratio very close to the transition from (2x4) to (3x6) surface reconstruction has been found to eliminate small, coreless oval defects.[9]

- Investigate the effect of substrate temperature on defect density for your specific system.

[\[1\]](#)

## Issue 2: High Threading Dislocation Density

Q: I am observing a high density of threading dislocations in my GaAs layer grown on a silicon (Si) substrate. What strategies can be employed to reduce them?

A: The large lattice mismatch between GaAs and Si is a primary source of threading dislocations. Several techniques can be used to mitigate this.

Potential Causes:

- Lattice Mismatch: The ~4% lattice mismatch between GaAs and Si generates misfit dislocations at the interface, which can then propagate into the epitaxial layer as threading dislocations.

- Thermal Mismatch: The difference in thermal expansion coefficients between GaAs and Si can introduce stress and generate dislocations upon cooling from the growth temperature.

Troubleshooting Steps:

- Introduce Dislocation Filter Layers (DFLs):

- Grow a series of strained-layer superlattices (SLS), such as InGaAs/GaAs or AlGaAs/GaAs. The interfaces of the SLS can bend and terminate propagating threading dislocations.[\[5\]](#)

- Optimize Growth Temperature of DFLs:

- The growth temperature of the DFLs can significantly impact their effectiveness. Higher growth temperatures can enhance dislocation annihilation.

- Employ Thermal Cycle Annealing (TCA):

- Subjecting the grown layer to cycles of high and low temperatures can promote dislocation movement and annihilation.[\[5\]](#)

- Use a Graded Buffer Layer:

- A buffer layer with a gradually changing lattice constant can help to accommodate the lattice mismatch more effectively.

## Quantitative Data Summary

Table 1: Effect of V/III Ratio on Surface Roughness and Growth Rate

| Material System | Growth Method | V/III Ratio | Surface Roughness (RMS)          | Growth Rate                    | Reference |

|-----------------|---------------|-------------|----------------------------------|--------------------------------|-----------|

| GaSb on GaAs    | MOCVD         | 1.25        | 3.6 nm                           | -                              | [7]       |

| GaSb on GaAs    | MOCVD         | 2.5         | 2.2 nm                           | -                              | [7]       |

| GaSb on GaAs    | MOCVD         | 5           | 3.8 nm                           | -                              | [7]       |

| AlGaSb on GaAs  | MOCVD         | < 2         | < 1.87 $\mu\text{m}/\text{hour}$ | -                              | [8]       |

| AlGaSb on GaAs  | MOCVD         | 3           | -                                | 3.54 $\mu\text{m}/\text{hour}$ | [8]       |

Table 2: Influence of Growth Parameters on Defect Densities

| Defect Type            | Material System | Growth Parameter       | Parameter Value                           | Resulting Defect Density                        | Reference |

|------------------------|-----------------|------------------------|-------------------------------------------|-------------------------------------------------|-----------|

| Oval Defects           | GaAs            | Ga Crucible Fill Level | > 50%                                     | High (e.g., $10^4\text{-}10^5\text{ cm}^{-2}$ ) | [9]       |

| Oval Defects           | GaAs            | Ga Crucible Fill Level | < 50%                                     | Low (e.g., < $500\text{ cm}^{-2}$ )             | [9]       |

| Threading Dislocations | GaAs on Si      | DFL Growth Temperature | $550\text{ }^{\circ}\text{C}$ (Low Temp)  | $5.2 \times 10^7\text{ cm}^{-2}$                |           |

| Threading Dislocations | GaAs on Si      | DFL Growth Temperature | $660\text{ }^{\circ}\text{C}$ (High Temp) | $1.5 \times 10^7\text{ cm}^{-2}$                |           |

| Threading Dislocations | GaAs on Si      | No DFL (Control)       | -                                         | $1.2 \times 10^8\text{ cm}^{-2}$                |           |

## Experimental Protocols

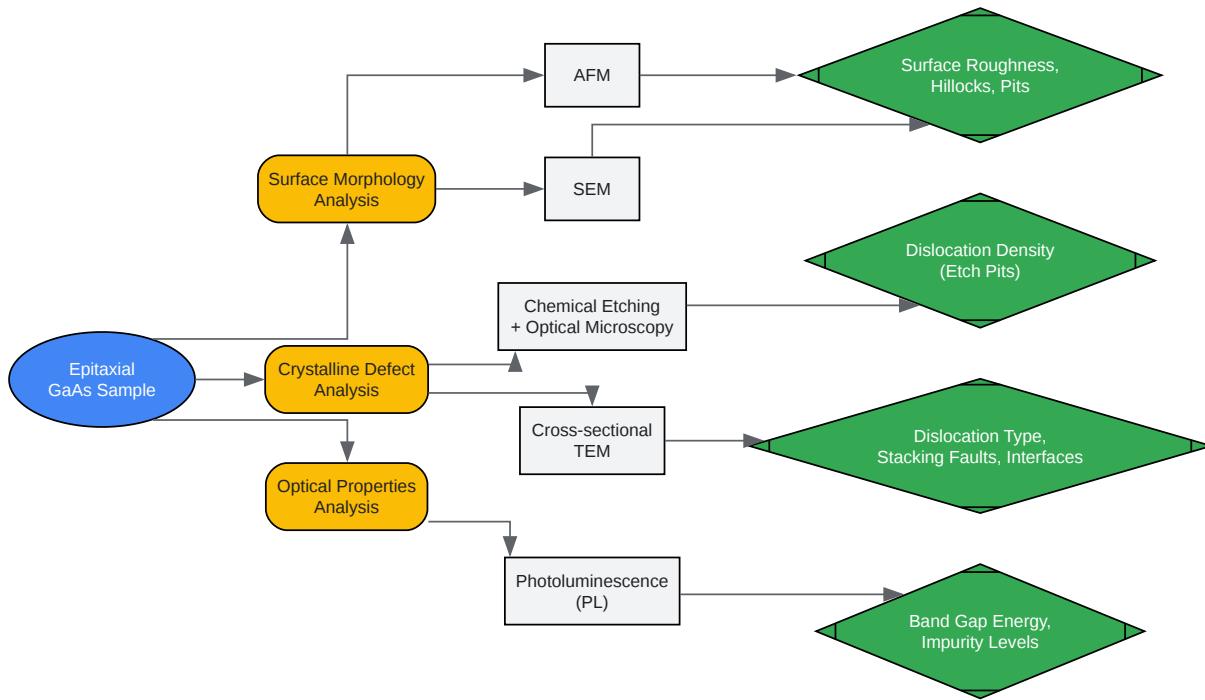

### Protocol 1: Cross-Sectional Transmission Electron Microscopy (TEM) Sample Preparation

This protocol outlines a general procedure for preparing cross-sectional TEM samples of GaAs epitaxial layers.

**Objective:** To prepare an electron-transparent cross-section of the GaAs epitaxial layer and substrate for imaging defects and interfaces.

**Materials:**

- Diamond scribe or wire saw

- Dummy Si or GaAs wafer

- Two-component epoxy glue (e.g., Gatan G1)

- Clamping fixture

- Grinding and polishing machine with diamond lapping films of various grit sizes (e.g., 30  $\mu\text{m}$  down to 0.5  $\mu\text{m}$ )

- Dimple grinder

- Ion mill (e.g., Gatan PIPS)

Procedure:

- Scribing and Cleaving:

- Cleave the GaAs wafer with the epitaxial layer into small pieces (e.g., 2 mm x 4 mm).

- Cleave a similar-sized piece from a dummy wafer.

- Face-to-Face Gluing:

- Glue the two pieces together face-to-face (epitaxial layer to epitaxial layer) using a thin layer of epoxy.

- Place the glued stack in a clamping fixture and cure the epoxy at the recommended temperature (e.g., 120°C for a few minutes).[10]

- Mechanical Grinding and Polishing:

- Mount the sample stack on a grinding stub.

- Mechanically grind the cross-section from both sides using progressively finer diamond lapping films until the sample thickness is about 20-30  $\mu\text{m}$ .[10][11]

- Dimple Grinding:

- Create a dimple in the center of the sample from both sides using a dimple grinder. This will make the central area thinner. The remaining thickness at the center should be around 15-25  $\mu\text{m}$ .[10]

- Ion Milling:

- Place the dimpled sample in an ion mill.

- Use low-angle (e.g., 3-5°) argon ion beams to mill the sample until a small hole appears at the center of the dimple. The area around the edge of the hole should be electron transparent.[10][11]

- A final low-energy milling step can be performed to reduce surface damage.

## Protocol 2: Atomic Force Microscopy (AFM) for Surface Morphology Characterization

This protocol provides a general workflow for characterizing the surface morphology of epitaxial GaAs layers using AFM.

**Objective:** To obtain high-resolution topographical images of the sample surface to analyze features like surface roughness, hillocks, and pits.

**Equipment:**

- Atomic Force Microscope

- AFM cantilever appropriate for the desired imaging mode (e.g., tapping mode)

- Sample mounting stage

**Procedure:**

- **Sample Preparation:**

- Cleave a small piece of the wafer for analysis.

- Ensure the sample surface is clean and free of dust by gently blowing with dry nitrogen.

- **Cantilever Installation and Laser Alignment:**

- Mount the AFM cantilever in the holder.

- Install the holder in the AFM head.

- Align the laser onto the back of the cantilever and adjust the photodetector to obtain a strong signal.[12]

- Cantilever Tuning (for Tapping Mode):

- Perform an auto-tune to find the resonant frequency of the cantilever.[12]

- Engage and Scan:

- Mount the sample on the AFM stage.

- Bring the cantilever close to the sample surface and engage the feedback loop.

- Start scanning the desired area.

- Parameter Optimization:

- Adjust the scan parameters (scan size, scan rate, setpoint, gains) to obtain a high-quality image with minimal artifacts.[12][13]

- Image Analysis:

- Use the AFM software to analyze the obtained images.

- Calculate the root-mean-square (RMS) roughness over a defined area.

- Measure the height and dimensions of surface features.

## Protocol 3: Defect-Revealing Chemical Etching

This protocol describes a method for revealing crystalline defects in GaAs using a chemical etchant.

**Objective:** To selectively etch the GaAs surface to make defects like dislocations visible for microscopic examination.

**Materials:**

- Molten KOH

- Hot plate

- Beakers

- Tweezers

- Deionized (DI) water

- Nitrogen gun

- Optical microscope with Nomarski contrast

**Procedure:**

- Sample Preparation:

- Cleave a piece of the GaAs wafer.

- Degrease the sample by sonicating in acetone, followed by methanol, and then rinsing with DI water.

- Etching:

- Preheat a hot plate to the desired etching temperature (e.g., 300-450°C).

- Place a beaker with KOH pellets on the hot plate and allow it to melt completely.

- Immerse the GaAs sample in the molten KOH for a specific duration (e.g., a few minutes). The etching time will depend on the temperature and the desired etch depth.

- Rinsing and Drying:

- Carefully remove the sample from the molten KOH and quench the etching by immersing it in DI water.

- Rinse the sample thoroughly with DI water.

- Dry the sample with a nitrogen gun.

- Microscopic Examination:

- Examine the etched surface under an optical microscope, preferably with Nomarski (Differential Interference Contrast) optics, to observe the etch pits corresponding to dislocations.

## Visualizations

### Troubleshooting Workflow for Oval Defects

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for high oval defect density.

### Experimental Workflow for Defect Characterization

[Click to download full resolution via product page](#)

Caption: Workflow for characterizing defects in epitaxial GaAs.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Oval Defects in the MBE Grown AlGaAs/InGaAs/GaAs and InGaAs/GaAs Structures | Semantic Scholar [semanticscholar.org]

- 2. opticaapplicata.pwr.edu.pl [opticaapplicata.pwr.edu.pl]

- 3. researchgate.net [researchgate.net]

- 4. The behavior of dislocations in GaAs substrates during the growth of GaxAl1-xAs epitaxial layers for Journal of Applied Physics - IBM Research [research.ibm.com]

- 5. mdpi.com [mdpi.com]

- 6. researchgate.net [researchgate.net]

- 7. Effect of V/III ratios on surface morphology in a GaSb thin film grown on GaAs substrate by MOCVD | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 8. matec-conferences.org [matec-conferences.org]

- 9. bjp-bg.com [bjp-bg.com]

- 10. researchgate.net [researchgate.net]

- 11. apps.dtic.mil [apps.dtic.mil]

- 12. amsec.wwu.edu [amsec.wwu.edu]

- 13. nercf.unl.edu [nercf.unl.edu]

- To cite this document: BenchChem. [Technical Support Center: Epitaxial Growth of GaAs Layers]. BenchChem, [2025]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b1256347#troubleshooting-epitaxial-growth-defects-in-gaas-layers\]](https://www.benchchem.com/product/b1256347#troubleshooting-epitaxial-growth-defects-in-gaas-layers)

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)