# Gallium Arsenide (GaAs) Device Fabrication

## Technical Support Center

**Author:** BenchChem Technical Support Team. **Date:** December 2025

### Compound of Interest

Compound Name: *Gallium arsenate*

Cat. No.: *B1256347*

[Get Quote](#)

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in improving the yield of gallium arsenide (GaAs) device fabrication.

## Troubleshooting Guides

This section provides solutions to common problems encountered during GaAs device fabrication.

Problem: Low device yield due to surface contamination.

Answer:

Surface contamination is a primary source of defects that can significantly reduce device yield. Proper wafer cleaning is crucial to remove organic residues, metallic impurities, and native oxides.

Recommended Wafer Cleaning Protocols:

A multi-step cleaning process is recommended for optimal results. The RCA clean is a standard and effective method.

Experimental Protocol: Standard RCA Clean for GaAs Wafer

- Preparation:

- Use only wafer carriers specifically designated for RCA cleaning.

- Wear appropriate personal protective equipment (PPE), including gloves, a face shield, and an apron.

- Prepare all solutions fresh for each use in a designated wet bench.

- SC-1 (Standard Clean 1) - Organic Removal:

- Prepare a solution of deionized (DI) water, ammonium hydroxide (NH<sub>4</sub>OH), and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) in a 6:1:1 ratio.

- Heat the solution to 70°C.

- Immerse the GaAs wafers in the SC-1 solution for 10 minutes.

- Rinse the wafers thoroughly in a quick dump rinser (QDR) with DI water.

- Oxide Strip (Optional but Recommended):

- To remove the thin oxide layer formed during the SC-1 step, immerse the wafers in a dilute buffered oxide etch (BOE) solution (e.g., 40:1 DI water:BOE) for 10 minutes.

- Rinse the wafers thoroughly in a QDR with DI water.

- SC-2 (Standard Clean 2) - Ionic and Metallic Removal:

- Prepare a solution of DI water, hydrochloric acid (HCl), and H<sub>2</sub>O<sub>2</sub> in a 6:1:1 ratio.

- Heat the solution to 70°C.

- Immerse the wafers in the SC-2 solution for 10 minutes.

- Rinse the wafers thoroughly in a QDR with DI water.

- Drying:

- Use a spin rinse dryer (SRD) to dry the wafers completely.

Problem: Poor ohmic contact quality, leading to high contact resistance.

Answer:

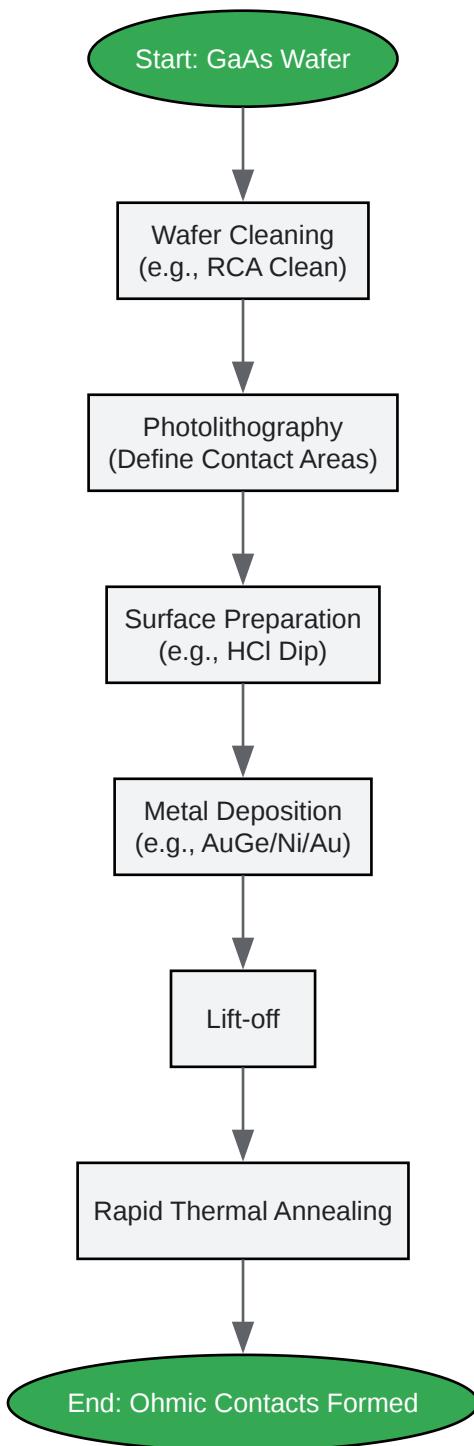

Achieving low-resistance ohmic contacts is critical for device performance. Issues often arise from inadequate surface preparation, improper metal deposition, or suboptimal annealing conditions.

Experimental Protocol: AuGe/Ni/Au Ohmic Contact Fabrication

- Surface Preparation:

- Immediately prior to metal deposition, perform a surface treatment to remove native oxides. A common method is to dip the wafer in a dilute HCl solution (e.g., HCl:H<sub>2</sub>O = 1:10) for 10 seconds, followed by a DI water rinse and nitrogen blow dry.[1]

- Photolithography for Lift-off:

- Define the contact areas using a standard photolithography lift-off process.[2] Ensure a slight undercut in the photoresist profile to facilitate clean metal lift-off.

- Metal Deposition:

- Using an e-beam evaporator, sequentially deposit the following metal layers onto the patterned wafer:

- AuGe (eutectic alloy)

- Ni (as a wetting agent)

- Au (as a final capping layer)[3]

- Lift-off:

- Immerse the wafer in a suitable solvent (e.g., acetone) to dissolve the photoresist and lift off the unwanted metal.[2]

- Annealing:

- Anneal the wafer in a rapid thermal annealing (RTA) system in a forming gas ( $H_2/N_2$ ) or nitrogen ambient. The annealing temperature and time are critical parameters that need to be optimized for the specific device structure.

Quantitative Data: Ohmic Contact Resistance vs. Annealing Temperature

| Annealing Temperature (°C) | Specific Contact Resistivity ( $\Omega \cdot \text{cm}^2$ ) | Reference |

|----------------------------|-------------------------------------------------------------|-----------|

| 250                        | $1.5 \times 10^{-6}$                                        | [4]       |

| 300                        | Negligible increase from 250°C                              | [4]       |

| 350                        | Slight decrease from 300°C                                  |           |

| 400                        | Rapid increase                                              |           |

| 420                        | $2.76 \times 10^{-6}$                                       | [5]       |

Note: The optimal annealing temperature can vary based on the specific metal stack and GaAs doping concentration.

Problem: Inconsistent or poor-quality etching results.

Answer:

Both wet and dry etching processes can present challenges in terms of uniformity, selectivity, and surface morphology. Careful selection of etchants and process parameters is essential.

Experimental Protocol: Selective Wet Etching of GaAs over AlGaAs

A citric acid/hydrogen peroxide solution is a commonly used selective etchant for GaAs over AlGaAs.

- Solution Preparation:

- Prepare a 4:1 volume ratio of citric acid ( $C_6H_8O_7$ ) to hydrogen peroxide ( $H_2O_2$ ).[6]

- Etching Process:

- Immerse the GaAs wafer in the solution at room temperature.

- The etch rate of GaAs is significantly higher than that of AlGaAs, providing good selectivity.[\[6\]](#)

#### Quantitative Data: Wet Etch Rates and Selectivity

| Etchant                                                                                  | Material                               | Etch Rate (nm/min) | Selectivity (GaAs/AlGaAs)                        | Reference           |

|------------------------------------------------------------------------------------------|----------------------------------------|--------------------|--------------------------------------------------|---------------------|

| Citric Acid:H <sub>2</sub> O <sub>2</sub> (4:1)                                          | GaAs                                   | Varies             | 155 (for Al <sub>0.3</sub> Ga <sub>0.7</sub> As) | <a href="#">[6]</a> |

| Citric Acid:H <sub>2</sub> O <sub>2</sub> (4:1)                                          | Al <sub>0.3</sub> Ga <sub>0.7</sub> As | Low                | <a href="#">[6]</a>                              |                     |

| H <sub>3</sub> PO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O (3:1:25) | GaAs                                   | ~300               | <a href="#">[7]</a>                              |                     |

| H <sub>2</sub> SO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O (1:1:10) | InGaAs                                 | ~600               | <a href="#">[7]</a>                              |                     |

Problem: High density of surface defects after epitaxial growth.

Answer:

The quality of the epitaxially grown GaAs layers is highly dependent on the growth conditions and the cleanliness of the substrate.

Key Considerations for MBE and MOCVD Growth:

- Substrate Preparation: Thorough cleaning of the GaAs substrate is critical to remove any contaminants that could act as nucleation sites for defects.

- Growth Temperature: The substrate temperature during growth affects the surface mobility of adatoms and can influence the incorporation of impurities and the formation of defects.

- V/III Ratio: The ratio of the group V (As) to group III (Ga) precursor fluxes is a critical parameter that controls the surface reconstruction and can impact defect formation.

- Growth Rate: A lower growth rate can sometimes lead to higher quality films by allowing more time for adatoms to find their optimal lattice sites.

## Frequently Asked Questions (FAQs)

Q1: What are the most common types of defects in photolithography on GaAs, and how can they be mitigated?

A1: Common photolithography defects include pattern misalignment, line edge roughness, resist scumming, pinholes, and bridging.[\[8\]](#)

- Pattern Misalignment: Caused by mechanical shifts in the wafer stage or optical distortions. Regular equipment calibration and the use of advanced alignment systems can mitigate this. [\[8\]](#)

- Line Edge Roughness (LER): Arises from fluctuations in the photolithographic process and limitations of the photoresist. Using high-contrast photoresists and optimizing exposure and development can reduce LER.[\[8\]](#)

- Resist Scumming: The presence of residual photoresist in cleared areas, often due to inadequate exposure or development. Adjusting exposure energy and development time can resolve this.[\[8\]](#)

- Pinholes and Voids: Small gaps in the photoresist layer, typically caused by particulate contamination. Stringent cleanroom protocols and optimized spin coating are necessary.[\[8\]](#)

- Bridging: Unwanted connections between photoresist features, usually due to overdevelopment or poor control of the bake process. Calibrating the development process and refining the bake schedule are key solutions.[\[8\]](#)

Q2: What is surface passivation, and why is it important for GaAs devices?

A2: Surface passivation is the process of treating the GaAs surface to reduce the density of electronic states within the bandgap. These surface states can act as recombination centers for charge carriers, leading to poor device performance. Passivation is crucial for reducing surface recombination velocity and improving the efficiency and reliability of GaAs devices.[\[9\]](#)[\[10\]](#)

### Experimental Protocol: Ammonium Sulfide ((NH<sub>4</sub>)<sub>2</sub>S) Passivation

- Pre-cleaning: Clean the GaAs wafer using a standard procedure to remove organic and metallic contaminants.

- Passivation: Immerse the wafer in an ammonium sulfide solution. The concentration, temperature, and duration of the treatment can be varied to optimize the passivation effect.

- Rinsing and Drying: After passivation, rinse the wafer with DI water and blow it dry with nitrogen.

The effectiveness of passivation can be evaluated by measuring the photoluminescence intensity, which is expected to increase with a reduction in surface recombination.[\[11\]](#)

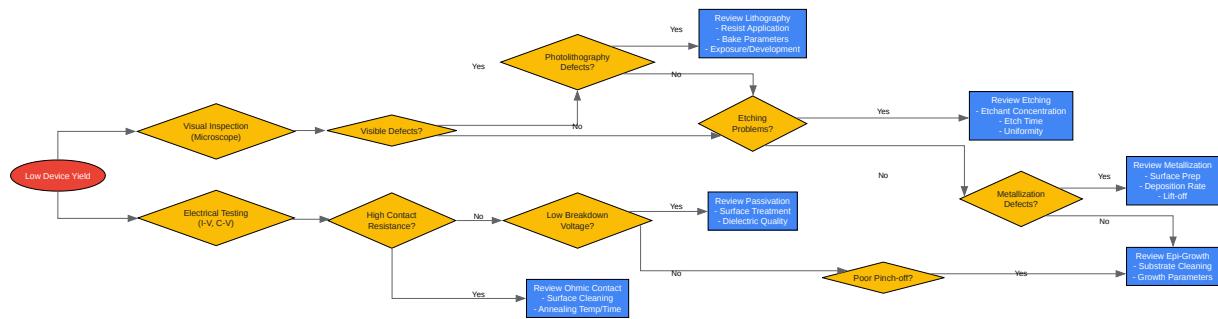

**Q3: How can I troubleshoot a low-yield issue in my GaAs MESFET fabrication process?**

**A3:** A systematic approach is necessary to identify the root cause of low yield. The following logical workflow can be used as a guide.

## Visualizations

Troubleshooting Workflow for Low Yield in GaAs MESFET Fabrication

[Click to download full resolution via product page](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [pubs.aip.org](https://pubs.aip.org) [pubs.aip.org]

- 2. [web.ece.ucsb.edu](https://web.ece.ucsb.edu) [web.ece.ucsb.edu]

- 3. [files01.core.ac.uk](https://files01.core.ac.uk) [files01.core.ac.uk]

- 4. [digital.library.unt.edu](https://digital.library.unt.edu) [digital.library.unt.edu]

- 5. [researchgate.net](https://researchgate.net) [researchgate.net]

- 6. [experts.illinois.edu](https://experts.illinois.edu) [experts.illinois.edu]

- 7. SOP for Wet Etching [[terpconnect.umd.edu](https://terpconnect.umd.edu)]

- 8. Common Lithography Defects and How to Fix Them [[eureka.patsnap.com](https://eureka.patsnap.com)]

- 9. [chalcogen.ro](https://chalcogen.ro) [chalcogen.ro]

- 10. [nepp.nasa.gov](https://nepp.nasa.gov) [nepp.nasa.gov]

- 11. Chemical studies of the passivation of GaAs surface recombination using sulfides and thiols [[authors.library.caltech.edu](https://authors.library.caltech.edu)]

- To cite this document: BenchChem. [Gallium Arsenide (GaAs) Device Fabrication Technical Support Center]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1256347#improving-yield-in-gallium-arsenide-device-fabrication>]

---

### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)