# a comprehensive guide to silicon and its use in semiconductor technology

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Silicon**

Cat. No.: **B1239273**

[Get Quote](#)

An In-depth Technical Guide to **Silicon** in Semiconductor Technology

## Introduction: The Indispensable Element

**Silicon** (Si) is the cornerstone of the modern electronics industry, serving as the primary material for the vast majority of semiconductor devices.<sup>[1]</sup> Its prominence stems from a unique combination of electrical properties, abundance in the Earth's crust (second only to oxygen), and the ability to form a stable, high-quality insulating oxide (**silicon** dioxide, SiO<sub>2</sub>).<sup>[1][2]</sup> As a semiconductor, **silicon** possesses conductivity intermediate between that of a conductor and an insulator, a characteristic that can be precisely controlled, making it ideal for creating the microscopic switches, or transistors, that form the basis of integrated circuits (ICs).<sup>[3][4]</sup> This guide provides a comprehensive overview of **silicon**'s fundamental properties and details the core technological processes that transform this elemental material into the sophisticated microchips powering our world.

## Fundamental Properties of Silicon

The utility of **silicon** in electronics is a direct result of its intrinsic physical, electrical, and thermal properties. **Silicon** is a hard, brittle crystalline solid with a blue-grey metallic lustre.<sup>[3]</sup> <sup>[5]</sup> Its atomic and crystal structure dictates its fundamental semiconductor characteristics.

## Atomic and Crystal Structure

**Silicon** has the atomic number 14, placing it in Group 14 of the periodic table.[3][5] It possesses four valence electrons, which it uses to form strong covalent bonds with four neighboring **silicon** atoms.[1] This bonding arrangement results in a highly ordered and stable diamond cubic crystal lattice structure, which is essential for the predictable electrical behavior required in semiconductor devices.[4][6]

## Electrical Properties

The most critical characteristic of **silicon** for semiconductor applications is its electronic band structure. The energy difference between the valence band and the conduction band, known as the band gap (Eg), determines the energy required to excite an electron into a conductive state.[2][7] **Silicon**'s band gap of approximately 1.12 eV at room temperature is ideal; it is large enough to minimize current leakage but small enough to allow for controlled conductivity through doping.[1][2][4][8]

Table 1: Key Electrical Properties of **Silicon**

| Property                                | Value                 | Units                               |

|-----------------------------------------|-----------------------|-------------------------------------|

| Atomic Number                           | 14                    | -                                   |

| Band Gap (Eg) at 300K                   | 1.12                  | eV                                  |

| Intrinsic Carrier Concentration at 300K | $1.02 \times 10^{10}$ | $\text{cm}^{-3}$                    |

| Dielectric Constant                     | 11.7                  | -                                   |

| Electron Mobility ( $\mu_n$ ) at 300K   | 1450                  | $\text{cm}^2/\text{V}\cdot\text{s}$ |

| Hole Mobility ( $\mu_p$ ) at 300K       | 500                   | $\text{cm}^2/\text{V}\cdot\text{s}$ |

Source:[1][9][10]

## Physical and Thermal Properties

**Silicon**'s physical and thermal characteristics are vital for the manufacturing process and for the reliability of the final electronic devices. Its high melting point allows it to withstand the high-

temperature fabrication steps, and its thermal conductivity enables the dissipation of heat generated during device operation.[1][11]

Table 2: Physical and Thermal Properties of **Silicon**

| Property                                 | Value                | Units             |

|------------------------------------------|----------------------|-------------------|

| Atomic Weight                            | 28.0855              | g/mol             |

| Crystal Structure                        | Diamond Cubic        | -                 |

| Lattice Constant at 300K                 | 0.543                | nm                |

| Density at 300K                          | 2.33                 | g/cm <sup>3</sup> |

| Melting Point                            | 1414                 | °C                |

| Boiling Point                            | 3265                 | °C                |

| Thermal Conductivity at 300K             | 1.31 - 1.49          | W/cm·°C           |

| Coefficient of Thermal Expansion at 300K | $2.6 \times 10^{-6}$ | °C <sup>-1</sup>  |

Source:[3][6][9][11]

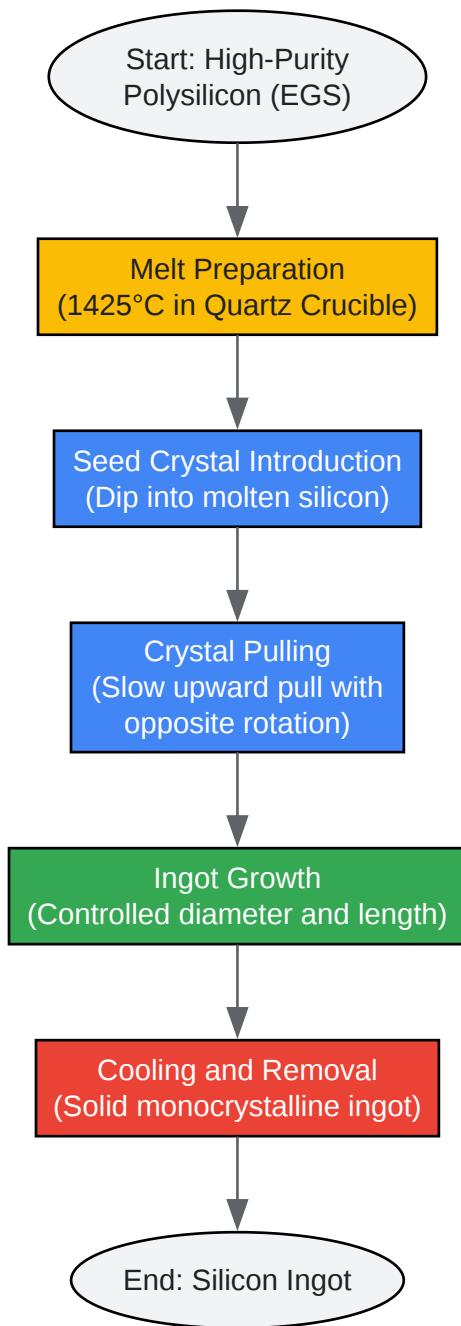

## From Polysilicon to Monocrystalline Ingot: The Czochralski Method

The journey from raw **silicon** to a functional microchip begins with the creation of a large, single-crystal ingot of exceptionally high purity. The Czochralski (CZ) method is the predominant industrial process for achieving this.[12][13]

Czochralski (CZ) Crystal Growth Workflow

[Click to download full resolution via product page](#)

Caption: Workflow of the Czochralski (CZ) method for **silicon** ingot growth.

## Experimental Protocol: Czochralski (CZ) Growth

The Czochralski process is a method of crystal pulling from a melt.[14]

- Melt Preparation: High-purity electronic-grade **silicon** (EGS) is placed into a quartz crucible. [13][15] The crucible is situated inside a vacuum furnace and heated to approximately 1425°C, well above **silicon**'s melting point of 1414°C.[13][14] The process occurs in a controlled inert argon atmosphere.[14]

- Seed Introduction: A small, high-purity single-crystal **silicon** seed with a specific crystallographic orientation is mounted on a rotating pull rod.[12][16] The seed is lowered until it just touches the surface of the molten **silicon**.[14]

- Crystal Pulling: A slight reduction in temperature at the seed-melt interface initiates crystallization.[14] The seed is then slowly pulled upwards (the "pull rate") while being rotated.[12][15] The crucible is typically rotated in the opposite direction to ensure thermal and compositional uniformity in the melt.[13]

- Ingot Formation: As the seed is withdrawn, surface tension causes a thin film of molten **silicon** to adhere to it, which then solidifies, replicating the crystal structure of the seed.[12] By precisely controlling the pull rate and temperature, a large, cylindrical single-crystal ingot (or "boule") is formed.[14] Dopants can be added to the melt to achieve a uniform initial doping level.[13][17]

- Finishing: Once the ingot reaches the desired length, it is cooled and removed from the furnace. The ends are cut off, and the ingot is ground to a precise diameter before being sliced into thin wafers.[12][18]

## Core Semiconductor Fabrication Processes

After the ingot is sliced into wafers and polished to a mirror-like finish, the process of building integrated circuits begins.[19][20] This involves a sequence of hundreds of steps that fall into four main categories: deposition, removal, patterning, and modification of electrical properties. [21]

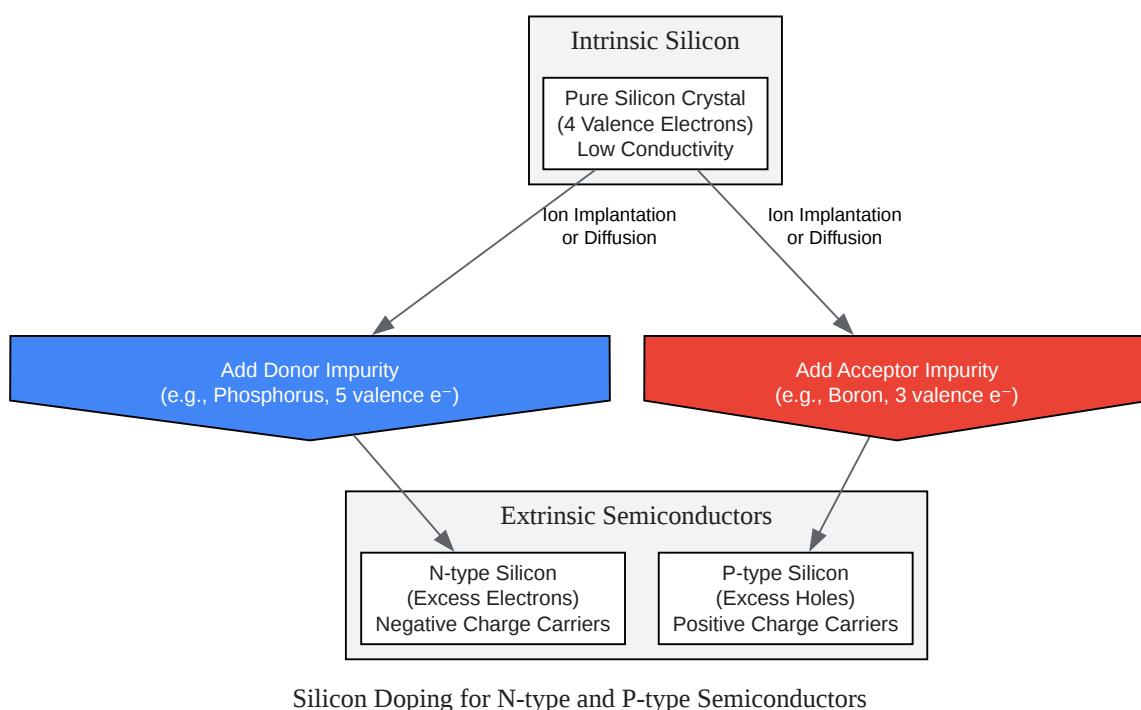

## Modification of Electrical Properties: Doping

Doping is the process of intentionally introducing impurities into the **silicon** crystal lattice to precisely control its resistivity and electrical properties.[22][23]

- N-type Doping: Introduces donor impurities from Group V (e.g., Phosphorus, Arsenic), which have five valence electrons.[23][24] The fifth electron is free to move, increasing the number of negative charge carriers (electrons).[25]

- P-type Doping: Introduces acceptor impurities from Group III (e.g., Boron), which have three valence electrons.[23][24] This creates "holes" (the absence of an electron) that act as positive charge carriers.[5]

[Click to download full resolution via product page](#)

Caption: Logical relationship between intrinsic **silicon** and doped semiconductors.

Ion implantation is a highly controllable doping method popular in large-scale production.[17][22]

- Ion Source Generation: The desired dopant material (e.g., boron for p-type, phosphorus for n-type) is vaporized and ionized to create a plasma.[26]

- Ion Acceleration: The generated ions are extracted from the source and accelerated to a high energy level using an electric field. The energy level determines the implantation depth.[24] [26]

- Mass Separation: A powerful magnet is used to filter the ion beam, ensuring only the desired dopant ions proceed.

- Implantation: The focused beam of high-energy ions is directed at the **silicon** wafer's surface.[26] The ions penetrate the surface and embed themselves within the crystal lattice. [22] Areas of the wafer can be masked off (typically with photoresist) to allow for selective doping.[17]

- Annealing: The implantation process damages the **silicon** crystal lattice. A post-implantation annealing step (heating the wafer to high temperatures) is required to repair this damage and electrically "activate" the implanted dopant atoms, allowing them to become effective charge carriers.[17][27]

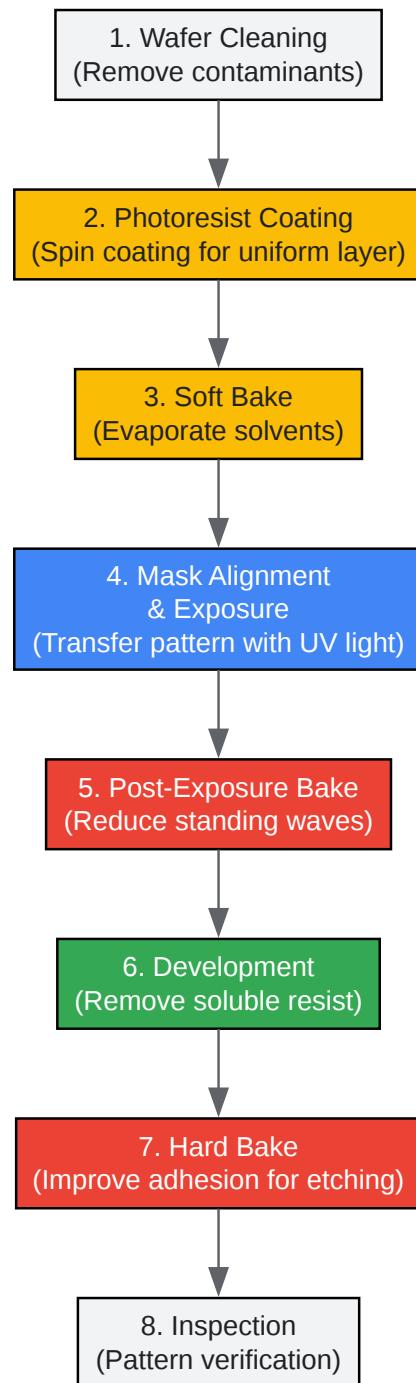

## Patterning: Photolithography

Photolithography is the process used to transfer geometric patterns from a photomask to a layer on the **silicon** wafer.[28][29] It is one of the most critical and repeated steps in semiconductor manufacturing.[30]

### Photolithography Experimental Workflow

[Click to download full resolution via product page](#)

Caption: The sequential steps involved in the photolithography process.

- Surface Preparation: The wafer is chemically cleaned to remove any particulate or organic contamination that could interfere with pattern adhesion.[29] A dehydration bake may be

performed to remove moisture.

- **Photoresist Application:** A light-sensitive polymer called photoresist is applied to the wafer surface.[31] This is typically done via spin coating, where the wafer is spun at high speed to produce a uniform, thin layer.[29]

- **Soft Bake:** The wafer is heated on a hot plate (e.g., 90-100°C for 60 seconds) to evaporate most of the solvent from the photoresist coating.[29]

- **Mask Alignment and Exposure:** A photomask, a plate containing the desired pattern, is precisely aligned over the wafer.[31] A high-intensity ultraviolet (UV) light source exposes the photoresist through the clear parts of the mask.[29][32] The light causes a chemical change in the exposed areas.

- **Post-Exposure Bake (PEB):** The wafer is baked again at a controlled temperature. This step is often used to minimize interference effects from the light waves.[33]

- **Development:** The wafer is immersed in or sprayed with a developer solution.[28] For a positive photoresist, the exposed areas become soluble and are washed away.[29] For a negative photoresist, the exposed areas become insoluble, and the unexposed areas are removed.

- **Hard Bake:** A final bake at a higher temperature (e.g., 120°C) hardens the remaining photoresist to improve its durability for the subsequent etching step.[33]

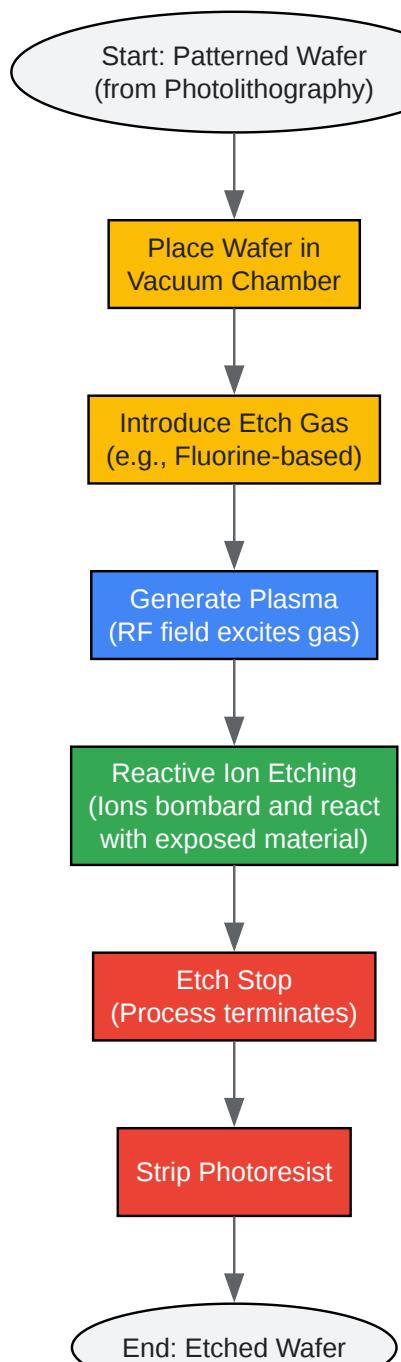

## Removal: Etching

Etching is the process of selectively removing material from the wafer surface to create the patterns defined by the photolithography step.[26][34] The remaining photoresist acts as a protective mask.

### Plasma (Dry) Etching Logical Flow

[Click to download full resolution via product page](#)

Caption: Logical flow diagram for a typical plasma etching process.

Plasma etching, a form of dry etching, uses reactive gases in a plasma state to remove material.<sup>[35][36]</sup> It is favored for creating fine features due to its anisotropic (directional) etching

capability.

- Chamber Loading: The wafer with the patterned photoresist is placed inside a vacuum chamber.[36]

- Gas Introduction: A process gas (or a mixture) is introduced into the chamber at low pressure.[36] The choice of gas depends on the material to be etched; fluorine-containing gases (e.g., CF<sub>4</sub>, SF<sub>6</sub>) are commonly used for **silicon** and **silicon** dioxide.[35][37]

- Plasma Generation: A high-frequency radio frequency (RF) electric field is applied to the chamber, which ionizes the gas and creates a plasma—a high-energy mixture of ions, electrons, and neutral radicals.[36]

- Etching: The electric field directs energetic ions toward the wafer surface. The etching occurs through a combination of physical sputtering (ions knocking atoms off the surface) and chemical reactions between the plasma's reactive species and the wafer material, forming volatile byproducts that are pumped away.[35][38] This process removes the material not protected by the photoresist.

- Resist Stripping: After the etch is complete, the remaining photoresist mask is removed, often using a different plasma process (ashing) or a chemical solvent.[36]

## Advanced Silicon Technologies

To continue the miniaturization of electronic devices as described by Moore's Law, semiconductor manufacturing has evolved beyond traditional bulk **silicon** processing.

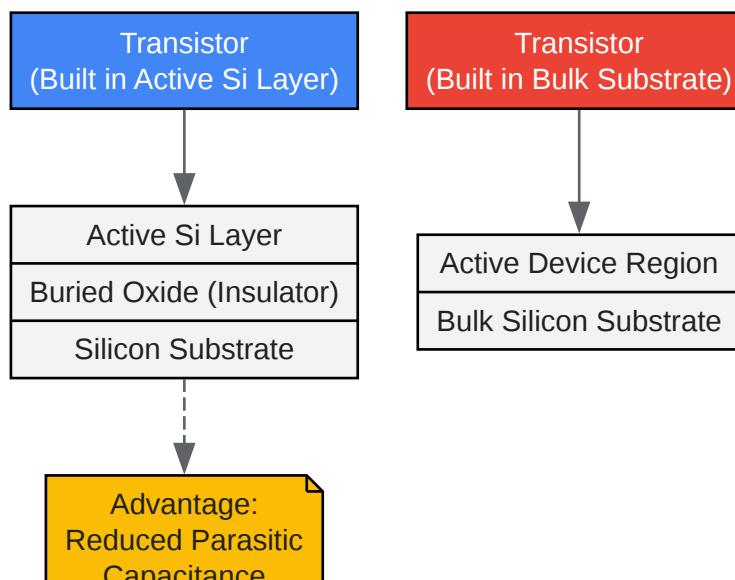

### Silicon-on-Insulator (SOI)

SOI technology involves fabricating devices on a layered substrate consisting of a thin top layer of **silicon**, a middle insulating layer (typically **silicon** dioxide, called the buried oxide or BOX), and a bulk **silicon** substrate.[39][40] This structure reduces parasitic capacitance, which lowers power consumption and increases device speed.[41][42] It also improves resistance to latchup and radiation.[40][41]

Silicon-on-Insulator (SOI) vs. Bulk CMOS

[Click to download full resolution via product page](#)

Caption: A comparison of SOI and traditional bulk **silicon** device structures.

## Conclusion

Silicon's unique and highly tunable properties have established it as the dominant material in the semiconductor industry.[1][2] Through sophisticated and precise manufacturing processes—from the growth of massive single crystals to the nanoscale patterning of circuits via photolithography, doping, and etching—raw **silicon** is transformed into the complex integrated circuits that are fundamental to virtually all modern technology.[32] While new materials are constantly being explored, the vast existing infrastructure and deep understanding of **silicon** processing ensure that it will remain at the heart of electronics for the foreseeable future.[3]

### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [wevolver.com](http://wevolver.com) [wevolver.com]

- 2. Band Gap Theory: Why Silicon Dominates Semiconductor Industry [eureka.patsnap.com](http://eureka.patsnap.com)

- 3. [waferpro.com](http://waferpro.com) [waferpro.com]

- 4. [youtube.com](http://youtube.com) [youtube.com]

- 5. Silicon - Wikipedia [en.wikipedia.org](http://en.wikipedia.org)

- 6. Properties of Silicon - El-Cat.com [el-cat.com](http://el-cat.com)

- 7. [universitywafer.com](http://universitywafer.com) [universitywafer.com]

- 8. [youtube.com](http://youtube.com) [youtube.com]

- 9. [universitywafer.com](http://universitywafer.com) [universitywafer.com]

- 10. What is a wide-band-gap semiconductor? | Toshiba Electronic Devices & Storage Corporation | Europe(EMEA) [toshiba.semicon-storage.com](http://toshiba.semicon-storage.com)

- 11. [wevolver.com](http://wevolver.com) [wevolver.com]

- 12. [waferpro.com](http://waferpro.com) [waferpro.com]

- 13. The Czochralski Method: What, Why and How | Linton Crystal Technologies [lintoncrystal.com](http://lintoncrystal.com)

- 14. PVA CGS | Czochralski Process (Cz) [pvatepla-cgs.com](http://pvatepla-cgs.com)

- 15. [buzztech.in](http://buzztech.in) [buzztech.in]

- 16. [inc42.com](http://inc42.com) [inc42.com]

- 17. Silicon Wafer Doping | Manufacturing Process | SemiconductorX [semiconductorkx.com](http://semiconductorkx.com)

- 18. Wafer forming process | SUMCO CORPORATION [sumcosi.com](http://sumcosi.com)

- 19. [renesas.com](http://renesas.com) [renesas.com]

- 20. Meticulous Wafer Manufacturing Steps [waferworld.com](http://waferworld.com)

- 21. Semiconductor device fabrication - Wikipedia [en.wikipedia.org](http://en.wikipedia.org)

- 22. [appliedphysicsusa.com](http://appliedphysicsusa.com) [appliedphysicsusa.com]

- 23. Doping (semiconductor) - Wikipedia [en.wikipedia.org](http://en.wikipedia.org)

- 24. The Complete Guide to Doping in Semiconductors: What Is it and Why Is it Necessary? [waferworld.com](http://waferworld.com)

- 25. [waferpro.com](http://waferpro.com) [waferpro.com]

- 26. What Are the Steps in Semiconductor Manufacturing? [surfxttechnologies.com](http://surfxttechnologies.com)

- 27. [intech-technologies.com](http://intech-technologies.com) [intech-technologies.com]

- 28. Photolithography - Wikipedia [en.wikipedia.org]

- 29. Photolithography in Semiconductor Manufacturing [waferworld.com]

- 30. [horiba.com](http://horiba.com) [horiba.com]

- 31. Semiconductor Front-End Process Episode 3: Photolithography [news.skhynix.com]

- 32. [theelevateedge.com](http://theelevateedge.com) [theelevateedge.com]

- 33. What is Photolithography? - GeeksforGeeks [geeksforgeeks.org]

- 34. [waferpro.com](http://waferpro.com) [waferpro.com]

- 35. [thierry-corp.com](http://thierry-corp.com) [thierry-corp.com]

- 36. Plasma etching - Wikipedia [en.wikipedia.org]

- 37. [electrochem.org](http://electrochem.org) [electrochem.org]

- 38. [bjp-bg.com](http://bjp-bg.com) [bjp-bg.com]

- 39. Silicon on insulator - Wikipedia [en.wikipedia.org]

- 40. Silicon On Insulator ( SOI ) – SignOff Semiconductors [signoffsemiconductors.com]

- 41. Silicon On Insulator (SOI) | Queen's Advanced MicroEngineering Centre [qub.ac.uk]

- 42. Silicon on Insulator - AnySilicon Semipedia [anysilicon.com]

- To cite this document: BenchChem. [a comprehensive guide to silicon and its use in semiconductor technology]. BenchChem, [2025]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b1239273#a-comprehensive-guide-to-silicon-and-its-use-in-semiconductor-technology\]](https://www.benchchem.com/product/b1239273#a-comprehensive-guide-to-silicon-and-its-use-in-semiconductor-technology)

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)