# Technical Support Center: Enhancing Charge Carrier Mobility in **s-Indacene** OFETs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **s-Indacene**

Cat. No.: **B1235719**

[Get Quote](#)

This technical support center provides researchers, scientists, and drug development professionals with a centralized resource for troubleshooting and optimizing the performance of **s-Indacene** based Organic Field-Effect Transistors (OFETs). The following sections are designed to address common issues encountered during experimentation and offer guidance on enhancing charge carrier mobility.

## Frequently Asked Questions (FAQs)

**Q1:** What are the key molecular design strategies to enhance charge carrier mobility in **s-Indacene** derivatives?

**A1:** Enhancing charge carrier mobility in **s-Indacene** OFETs begins at the molecular level. Key strategies include:

- Extending  $\pi$ -conjugation and enhancing molecular planarity: A more extensive and planar  $\pi$ -system facilitates efficient intramolecular charge transport.[1][2][3]

- Optimizing donor-acceptor structures: Introducing appropriate electron-donating or withdrawing groups can tune the frontier molecular orbital energy levels for better charge injection and transport.[1][2]

- Promoting strong intermolecular aggregation and well-ordered structures: Close  $\pi$ - $\pi$  stacking and ordered molecular packing are crucial for efficient intermolecular charge hopping.[1][2][3] The introduction of specific side chains, such as triisopropylsilyl (TIPS)

ethynyl groups, has been shown to afford favorable solid-state packing in some **s-Indacene** derivatives.[4]

- Alkyl chain engineering: The length and shape (linear vs. branched) of alkyl side chains play a critical role in influencing molecular packing and solubility, which in turn affects charge carrier mobility.[3]

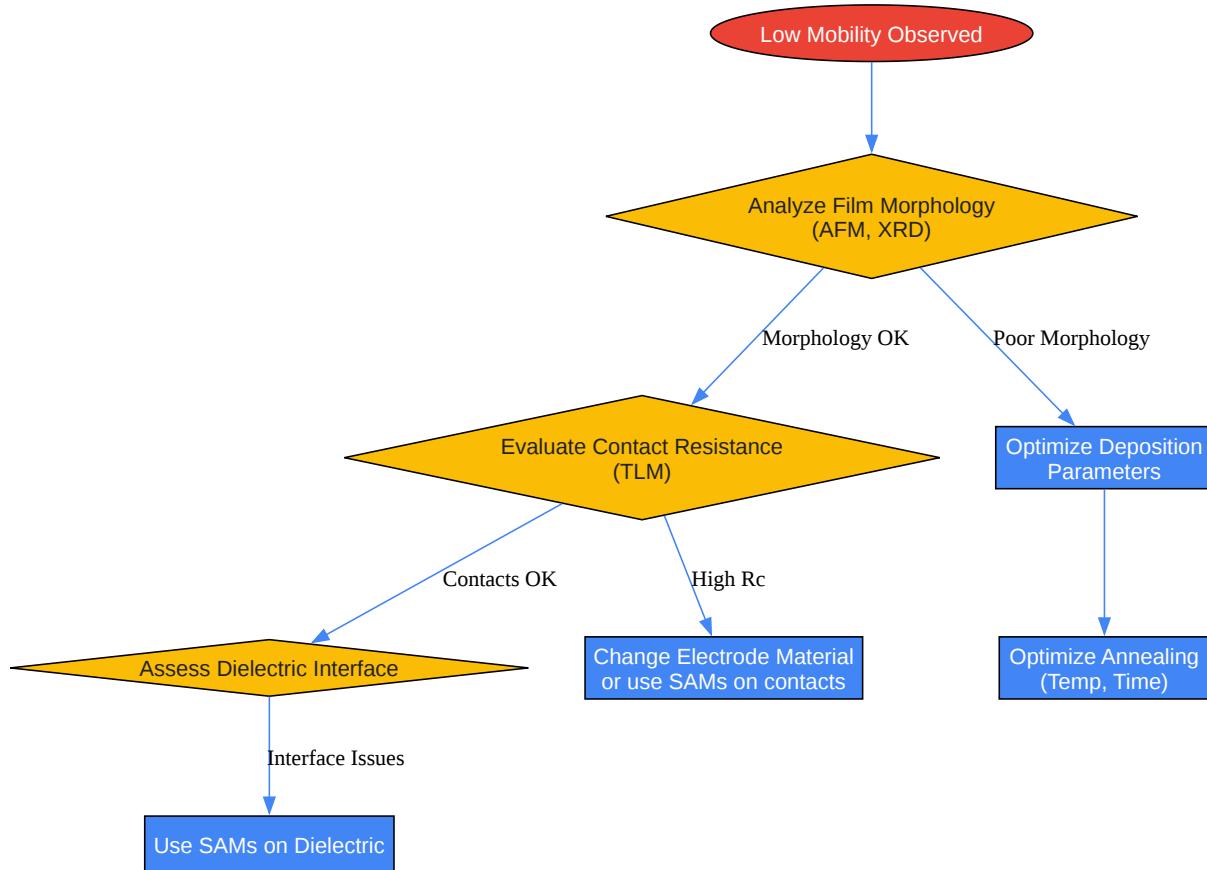

Q2: My **s-Indacene** OFET is showing very low or no field-effect mobility. What are the potential causes?

A2: Low or no mobility can stem from several factors:

- Poor Film Morphology: Disordered or amorphous thin films of the **s-Indacene** semiconductor will have very poor charge transport pathways. This can be caused by suboptimal deposition conditions (e.g., spin-coating speed, solvent choice) or the lack of an appropriate post-deposition treatment like thermal annealing.

- High Contact Resistance: A significant energy barrier between the source/drain electrodes and the **s-Indacene** semiconductor layer can impede charge injection, leading to low measured mobility. This is often due to a mismatch between the work function of the metal electrode and the frontier molecular orbitals of the organic semiconductor.

- Traps at the Dielectric Interface: Charge traps at the semiconductor-dielectric interface can immobilize charge carriers, reducing the overall mobility. These traps can arise from impurities, surface roughness of the dielectric, or dangling bonds.

- Degradation of the Organic Semiconductor: Exposure to oxygen, moisture, or even ambient light can degrade the **s-Indacene** compound, leading to poor device performance.

Q3: How does thermal annealing affect the performance of **s-Indacene** OFETs?

A3: Thermal annealing is a critical post-deposition step that can significantly enhance the charge carrier mobility of **s-Indacene** OFETs. The primary benefits of annealing include:

- Improved Crystallinity and Molecular Ordering: Heating the semiconductor film provides the molecules with the thermal energy needed to self-assemble into more ordered, crystalline domains. This improved packing facilitates more efficient intermolecular charge transport.

- Reduced Grain Boundaries: Annealing can promote the growth of larger crystalline grains, reducing the number of grain boundaries that can act as scattering sites for charge carriers.

- Removal of Residual Solvent: The annealing process helps to drive off any residual solvent from the thin film, which can otherwise act as charge traps. It is important to optimize the annealing temperature and duration for each specific **s-Indacene** derivative, as excessive heat can lead to film dewetting or degradation.

Q4: What is the importance of the semiconductor-dielectric interface and how can it be optimized?

A4: The semiconductor-dielectric interface is where the charge accumulation and transport occur in an OFET. A high-quality interface is crucial for achieving high mobility. This interface can be optimized by:

- Surface Treatment of the Dielectric: Using self-assembled monolayers (SAMs) like hexamethyldisilazane (HMDS) or pentafluorobenzenethiol (PFBT) can modify the surface energy of the dielectric, promoting better ordering of the **s-Indacene** molecules and reducing charge traps.

- Choosing an Appropriate Dielectric Material: The choice of dielectric material can influence the degree of charge carrier scattering at the interface.

- Minimizing Interface Roughness: A smooth dielectric surface is essential for uniform film formation and to prevent the creation of physical traps for charge carriers.

## Troubleshooting Guide

This guide provides a systematic approach to diagnosing and resolving common issues encountered during the fabrication and characterization of **s-Indacene** OFETs.

| Observed Problem                           | Potential Cause(s)                                                                                                  | Recommended Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low hole/electron mobility                 | 1. Poorly ordered semiconductor film.2. High contact resistance.3. Traps at the semiconductor-dielectric interface. | 1. Optimize the deposition parameters (e.g., spin-coating speed, substrate temperature).2. Introduce a thermal annealing step or optimize the annealing temperature and time.3. Choose source/drain electrodes with a work function that aligns with the HOMO/LUMO of your s-Indacene derivative to ensure Ohmic contact. <a href="#">[1]</a> <a href="#">[2]</a> 4. Treat the dielectric surface with a suitable SAM before depositing the semiconductor. |

| High OFF current / Low ON/OFF ratio        | 1. Impurities in the semiconductor material.2. Gate leakage current.3. Bulk conductivity of the semiconductor film. | 1. Purify the s-Indacene material before use.2. Ensure the integrity of the gate dielectric layer; check for pinholes or cracks.3. Optimize the thickness of the semiconductor film; thicker films can sometimes lead to higher bulk conductivity.                                                                                                                                                                                                         |

| Large threshold voltage (V <sub>th</sub> ) | 1. Presence of a high density of charge traps.2. Fixed charges in the dielectric layer.                             | 1. Improve the cleanliness of the substrate and the deposition environment.2. Use a high-purity dielectric material.3. Treat the dielectric surface with a SAM to passivate trap states.                                                                                                                                                                                                                                                                   |

---

|                                                             |                                                                                       |                                                                                                                                                                                                  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device instability (performance degrades over time)         | 1. Degradation of the s-Indacene material due to exposure to air, moisture, or light. | 1. Fabricate and characterize the devices in an inert atmosphere (e.g., a glovebox).2. Encapsulate the final device to protect it from the ambient environment.                                  |

| Non-ideal output characteristics (e.g., non-linear turn-on) | 1. Significant contact resistance effects.                                            | 1. Use a four-probe measurement technique to decouple the contact resistance from the channel resistance.2. Treat the source/drain contacts with a suitable SAM to reduce the injection barrier. |

---

## Quantitative Data Summary

The following table summarizes reported charge carrier mobility values for various organic semiconductors, providing a benchmark for performance. Note that values for specific **s-Indacene** derivatives can vary significantly based on the molecular structure and processing conditions.

| Organic Semiconductor                  | Deposition Method  | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio      | Reference |

|----------------------------------------|--------------------|--------------------------------|-------------------|-----------|

| Dinaphtho-fused s-indacene derivatives | Solution-processed | > 7                            | -                 | [4]       |

| PTFDFT                                 | -                  | $\mu_h = 1.08, \mu_e = 2.23$   | -                 | [1]       |

| PDPPFT                                 | -                  | $\mu_h = 0.78, \mu_e = 0.24$   | -                 | [1]       |

| P-NDF                                  | -                  | $\mu_h = 0.55$                 | -                 | [1]       |

| P-BDF                                  | -                  | $\mu_h = 0.85$                 | -                 | [1]       |

| PIDT-DPP                               | Solution-processed | 0.065                          | $4.6 \times 10^5$ | [5]       |

| DPPTT with NMe <sub>4</sub> I additive | -                  | 4.4                            | -                 | [6]       |

| Neat DPPTT                             | -                  | 0.8                            | -                 | [6]       |

## Experimental Protocols

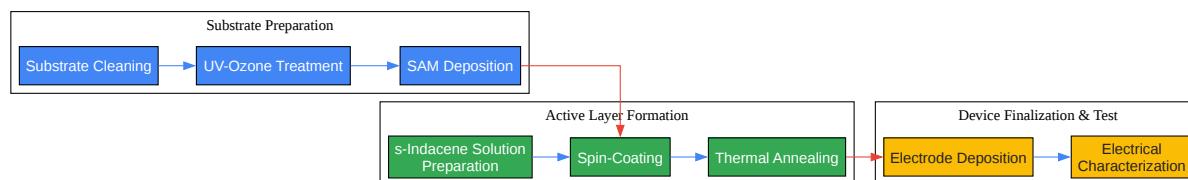

### General Protocol for Solution-Processed s-Indacene OFET Fabrication (Bottom-Gate, Top-Contact)

This protocol provides a general framework. Researchers should optimize the specific parameters for their **s-Indacene** derivative and experimental setup.

- Substrate Cleaning:

- Substrates (e.g., heavily n-doped Si with a thermally grown SiO<sub>2</sub> layer) are sequentially cleaned in an ultrasonic bath with deionized water, acetone, and isopropanol for 15 minutes each.

- The substrates are then dried with a stream of nitrogen gas.

- An optional UV-ozone treatment for 10-15 minutes can be performed to remove organic residues and improve the hydrophilicity of the surface.

- Dielectric Surface Treatment (Optional but Recommended):

- A self-assembled monolayer (SAM) is applied to the  $\text{SiO}_2$  surface to improve the interface properties. For example, the substrates can be immersed in a dilute solution of hexamethyldisilazane (HMDS) in toluene or exposed to HMDS vapor.

- **s-Indacene** Solution Preparation:

- Dissolve the **s-Indacene** derivative in a suitable organic solvent (e.g., toluene, chloroform, or chlorobenzene) at a specific concentration (typically 1-10 mg/mL).

- The solution should be stirred, possibly with gentle heating, until the material is fully dissolved. Filtering the solution through a PTFE syringe filter can remove any particulate impurities.

- Thin Film Deposition (Spin-Coating):

- The **s-Indacene** solution is spin-coated onto the prepared substrate. Typical spin-coating parameters are in the range of 1000-4000 rpm for 30-60 seconds. These parameters should be optimized to achieve the desired film thickness and morphology.

- The spin-coating process should ideally be carried out in an inert atmosphere to prevent solvent evaporation issues and material degradation.

- Thermal Annealing:

- The substrate with the deposited **s-Indacene** film is annealed on a hotplate at a temperature typically between 80°C and 150°C for a duration of 10-60 minutes. The optimal annealing temperature and time are highly dependent on the specific **s-Indacene** derivative and must be determined experimentally. This step should be performed in an inert atmosphere.

- Source-Drain Electrode Deposition:

- Source and drain electrodes (e.g., Gold) are thermally evaporated onto the **s-Indacene** film through a shadow mask. A thin adhesion layer of chromium or titanium may be used. The channel length and width are defined by the shadow mask.

- Device Characterization:

- The electrical characteristics of the OFET are measured using a semiconductor parameter analyzer in an inert atmosphere or in a vacuum probe station. Transfer and output curves are recorded to extract key parameters such as charge carrier mobility, threshold voltage, and the on/off ratio.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Workflow for the fabrication and characterization of **s-Indacene** OFETs.

[Click to download full resolution via product page](#)

Caption: A logical flowchart for troubleshooting low mobility in **s-Indacene** OFETs.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Molecular Design Concept for Enhancement Charge Carrier Mobility in OFETs: A Review [mdpi.com]

- 2. researchgate.net [researchgate.net]

- 3. Molecular Design Concept for Enhancement Charge Carrier Mobility in OFETs: A Review - PMC [pmc.ncbi.nlm.nih.gov]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. Remarkable enhancement of charge carrier mobility of conjugated polymer field-effect transistors upon incorporating an ionic additive - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Technical Support Center: Enhancing Charge Carrier Mobility in s-Indacene OFETs]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b1235719#enhancing-the-charge-carrier-mobility-in-s-indacene-ofets>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)