# Copper Phosphide in Semiconductor Devices: Application Notes and Protocols

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Phosphide*

Cat. No.: *B1233454*

[Get Quote](#)

For Researchers, Scientists, and Drug Development Professionals

## Introduction

Copper **phosphide**, a binary compound of copper and phosphorus, is emerging as a compelling material for a new generation of semiconductor devices. Its unique electronic and optical properties, coupled with the natural abundance of its constituent elements, make it an attractive candidate for applications in transistors, memristors, solar cells, and thermoelectric devices. This document provides detailed application notes and experimental protocols for the synthesis of copper **phosphide** and the fabrication of semiconductor devices, intended to guide researchers in exploring the potential of this promising material.

## Material Properties and Characteristics

Copper **phosphide** exists in several stoichiometric forms, with copper(I) **phosphide** ( $Cu_3P$ ) and copper **diphosphide** ( $CuP_2$ ) being the most studied for semiconductor applications. The electronic nature of  $Cu_3P$  has been a subject of debate, with studies suggesting it can exhibit properties ranging from a semiconductor to a semimetal, often influenced by stoichiometry and defects like copper vacancies.<sup>[1]</sup>  $Cu_3P$  is typically a p-type material.<sup>[1]</sup> In contrast,  $CuP_2$  is a phosphorus-rich semiconductor.<sup>[2]</sup>

## Quantitative Data Summary

The following tables summarize key quantitative data for copper **phosphide** materials and devices as reported in the literature.

Table 1: Electronic and Physical Properties of Copper **Phosphides**

| Property          | Cu <sub>3</sub> P                                                                                  | CuP <sub>2</sub>                                               | Source |

|-------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------|

| Crystal Structure | Hexagonal                                                                                          | Monoclinic                                                     | [2][3] |

| Band Gap          | ~1.6 eV (disputed, can be semimetallic)                                                            | ~1.5 eV                                                        | [1][4] |

| Conductivity Type | p-type                                                                                             | p-type                                                         | [1][5] |

| Hole Mobility     | 28.8 cm <sup>2</sup> /(V·s) (thin film, 300 K) to 276 cm <sup>2</sup> /(V·s) (thin film, low temp) | 147 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> (nanowire) | [1][5] |

| Resistivity       | 4.6 × 10 <sup>-5</sup> Ω·cm (thin film)                                                            | -                                                              | [1]    |

| Melting Point     | 900 °C                                                                                             | -                                                              | [6]    |

Table 2: Performance Metrics of Copper **Phosphide**-Based Devices

| Device Type                                                     | Key Parameter                 | Value                                          | Source |

|-----------------------------------------------------------------|-------------------------------|------------------------------------------------|--------|

| CuP <sub>2</sub> Nanowire FET                                   | On/Off Ratio                  | > 10 <sup>4</sup>                              | [2][5] |

| Cu <sub>3</sub> P Nanoribbon Memristor                          | On/Off Ratio                  | up to 10 <sup>4</sup>                          | [7]    |

| Ternary Copper Phosphide Thermoelectric (ACuP)                  | Figure of Merit (zT)          | 0.5 at 800 K                                   | [8]    |

| Cu <sub>3</sub> P/g-C <sub>3</sub> N <sub>4</sub> Photocatalyst | H <sub>2</sub> Evolution Rate | up to 343 μmol h <sup>-1</sup> g <sup>-1</sup> | [9]    |

## Experimental Protocols

This section provides detailed methodologies for the synthesis of copper **phosphide** and the fabrication of representative semiconductor devices.

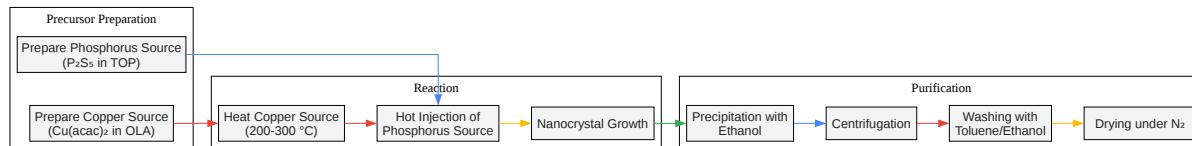

### Protocol 1: Solvothermal Synthesis of Cu<sub>3</sub>P Nanocrystals

This protocol describes a solution-based synthesis of Cu<sub>3</sub>P nanocrystals using a hot-injection method.<sup>[7]</sup>

#### Materials:

- Copper(II) acetylacetone (Cu(acac)<sub>2</sub>)

- Phosphorus pentasulfide (P<sub>2</sub>S<sub>5</sub>)

- Trioctylphosphine (TOP)

- Oleylamine (OLA)

- Toluene

- Ethanol

#### Equipment:

- Three-neck flask

- Schlenk line

- Heating mantle

- Syringe

- Centrifuge

- Round-bottom flask

**Procedure:**

- **Phosphorus Precursor Preparation:**

- In a round-bottom flask under a nitrogen atmosphere, dissolve a controlled quantity of  $P_2S_5$  in TOP.

- Stir the mixture at 40 °C for 20 minutes until the solution turns homogeneously orange. This solution serves as the in-situ phosphorus source.

- **Copper Precursor Preparation:**

- In a three-neck flask connected to a Schlenk line, combine 1.5 mmol of  $Cu(acac)_2$  with 10.0 mL of degassed OLA.

- Heat the mixture under nitrogen to the desired reaction temperature (between 200 °C and 300 °C). Copper nanocrystals will form in the solution.

- **Hot Injection and Growth:**

- Rapidly inject the prepared phosphorus precursor solution into the hot copper precursor solution.

- Allow the reaction to proceed at the set temperature. The size of the resulting  $Cu_3P$  nanocrystals can be controlled by the reaction temperature.

- **Purification:**

- After the reaction, cool the flask to room temperature.

- Add toluene to the solution, followed by ethanol to precipitate the  $Cu_3P$  nanocrystals.

- Centrifuge the mixture to collect the nanocrystals.

- Wash the collected nanocrystals with a toluene/ethanol mixture at least three times.

- Dry the purified  $Cu_3P$  nanocrystals under a stream of nitrogen.

[Click to download full resolution via product page](#)

### Solvothermal Synthesis of Cu<sub>3</sub>P Nanocrystals Workflow

## Protocol 2: Topochemical Synthesis of Cu<sub>3</sub>P Nanoribbons

This protocol details the synthesis of single-crystal Cu<sub>3</sub>P nanoribbons from crystalline red phosphorus (cRP) nanoribbons.<sup>[7]</sup>

#### Materials:

- Amorphous red phosphorus (a-RP)

- Iodine (I<sub>2</sub>)

- Copper acetylacetone (Cu(acac)<sub>2</sub>)

- N-Methyl pyrrolidone (NMP)

- Ethanol

#### Equipment:

- Tube furnace

- Sealed quartz ampoule

- Beaker

- Stir plate

Procedure:

- Synthesis of Crystalline Red Phosphorus (cRP) Nanoribbons:

- Seal a mixture of amorphous red phosphorus and a small amount of iodine as a transport agent in a quartz ampoule under vacuum.

- Place the ampoule in a two-zone tube furnace and perform chemical vapor transport to grow bulk cRP crystals.

- Exfoliate the bulk cRP crystals into cRP nanoribbons by sonication in a suitable solvent.

- Topochemical Conversion to  $\text{Cu}_3\text{P}$  Nanoribbons:

- Disperse the cRP nanoribbons in NMP.

- Prepare a solution of copper acetylacetone in NMP.

- Mix the two solutions and stir at a specific temperature to allow the topochemical conversion of cRP to  $\text{Cu}_3\text{P}$  nanoribbons. During this process, copper ions intercalate into the cRP lattice, leading to the formation of  $\text{Cu}_3\text{P}$  while preserving the nanoribbon morphology.

- Wash the resulting  $\text{Cu}_3\text{P}$  nanoribbons with ethanol and redisperse them in a suitable solvent.

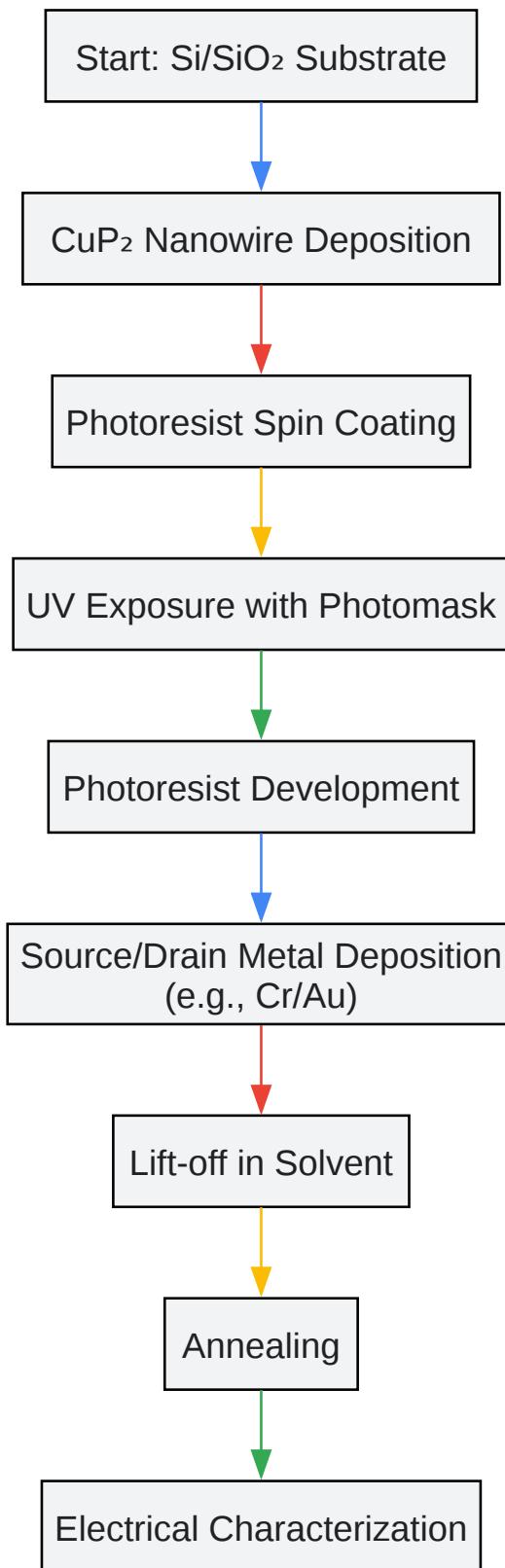

## Protocol 3: Fabrication of a $\text{CuP}_2$ Nanowire Field-Effect Transistor (FET)

This protocol outlines the steps to fabricate a back-gated field-effect transistor using a single  $\text{CuP}_2$  nanowire.[\[5\]](#)

Materials:

- CuP<sub>2</sub> nanowires (synthesized via a method like supercritical fluid-liquid-solid growth)

- Highly doped silicon wafer with a SiO<sub>2</sub> layer (e.g., 300 nm)

- Photoresist (e.g., S1813)

- Developer

- Metal for contacts (e.g., Cr/Au or Ti/Au)

- Isopropyl alcohol (IPA)

**Equipment:**

- Spin coater

- Hot plate

- Photolithography system (mask aligner)

- Electron-beam or thermal evaporator

- Probe station and semiconductor device analyzer

**Procedure:**

- Substrate Preparation:

- Clean the Si/SiO<sub>2</sub> wafer using a standard cleaning procedure (e.g., RCA clean). The highly doped silicon will act as the back gate, and the SiO<sub>2</sub> layer as the gate dielectric.

- Nanowire Deposition:

- Disperse the synthesized CuP<sub>2</sub> nanowires in a volatile solvent like IPA.

- Drop-cast the nanowire suspension onto the Si/SiO<sub>2</sub> substrate and allow the solvent to evaporate.

- Contact Patterning (Photolithography):

- Spin-coat a layer of photoresist onto the substrate.

- Pre-bake the photoresist on a hot plate.

- Use a mask aligner to expose the photoresist with a UV lamp through a photomask designed for the source and drain electrode patterns, ensuring the pattern aligns with a selected nanowire.

- Develop the photoresist to reveal the areas for metal deposition.

- Contact Deposition:

- Immediately before metal deposition, briefly dip the substrate in a buffered oxide etch (BOE) solution to remove any native oxide from the nanowire surface in the contact regions.

- Deposit the source and drain contact metals (e.g., 5 nm Cr for adhesion followed by 80 nm Au) using an electron-beam or thermal evaporator.

- Lift-off:

- Immerse the substrate in a suitable solvent (e.g., acetone) to dissolve the remaining photoresist, lifting off the excess metal and leaving behind the patterned source and drain electrodes in contact with the CuP<sub>2</sub> nanowire.

- Annealing:

- Anneal the device in an inert atmosphere (e.g., N<sub>2</sub> or Ar) at a moderate temperature (e.g., 200 °C) to improve the contact between the metal electrodes and the nanowire.

- Device Characterization:

- Place the fabricated device on a probe station.

- Use a semiconductor device analyzer to measure the electrical characteristics, such as the output and transfer curves, to determine the on/off ratio and charge carrier mobility.

[Click to download full resolution via product page](#)

CuP<sub>2</sub> Nanowire FET Fabrication Workflow

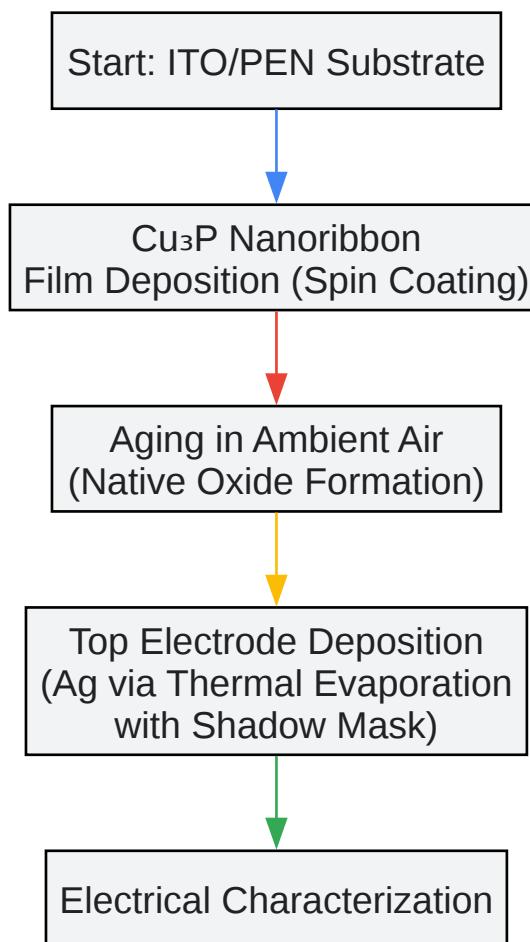

## Protocol 4: Fabrication of a Flexible Cu<sub>3</sub>P Nanoribbon Memristor

This protocol describes the fabrication of a flexible memristor with a Ag/Cu<sub>3</sub>P/ITO structure on a PEN substrate.[\[7\]](#)

### Materials:

- Cu<sub>3</sub>P nanoribbons (synthesized as per Protocol 2)

- Indium tin oxide (ITO)-coated polyethylene naphthalate (PEN) substrate

- Silver (Ag) for top electrodes

### Equipment:

- Spin coater

- Thermal evaporator

- Shadow mask

- Probe station and semiconductor device analyzer

### Procedure:

- Substrate Preparation:

- Clean the ITO/PEN substrate.

- Cu<sub>3</sub>P Nanoribbon Film Deposition:

- Drop-cast the Cu<sub>3</sub>P nanoribbon suspension onto the ITO/PEN substrate.

- Spin-coat the substrate (e.g., at 1500 rpm for 20 s, then 3000 rpm for 10 s) to form a uniform film of nanoribbons.

- Allow the film to age under ambient conditions to form a native oxide layer on the surface of the nanoribbons, which can enhance the resistive switching behavior.

- Top Electrode Deposition:

- Place a shadow mask with desired electrode patterns (e.g., circular pads with a diameter of 80  $\mu\text{m}$ ) on top of the  $\text{Cu}_3\text{P}$  nanoribbon film.

- Deposit the top silver electrodes (e.g., 200 nm thick) through the shadow mask using a thermal evaporator.

- Device Characterization:

- Perform current-voltage (I-V) measurements using a probe station and semiconductor device analyzer by applying a voltage to the top Ag electrode while the bottom ITO electrode is grounded.

- Investigate the resistive switching behavior, retention, and endurance of the memristor device.

[Click to download full resolution via product page](#)

Flexible Cu<sub>3</sub>P Memristor Fabrication Workflow

## Signaling Pathways and Device Physics

The operation of copper **phosphide**-based semiconductor devices relies on fundamental electronic processes.

### Field-Effect Transistor (FET)

In a CuP<sub>2</sub> nanowire FET, the conductance of the nanowire channel is modulated by an external electric field applied through the back gate. As a p-type semiconductor, applying a negative gate voltage accumulates holes in the channel, increasing its conductivity (ON state). Conversely, a positive gate voltage depletes the holes, reducing the conductivity (OFF state).

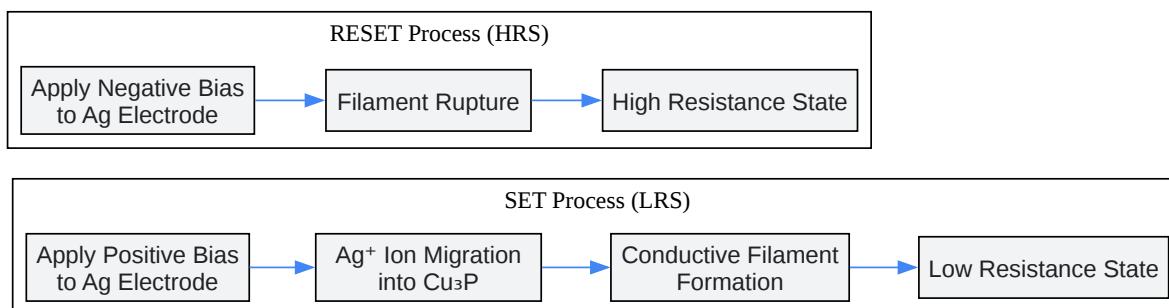

### Memristor

The resistive switching in a Cu<sub>3</sub>P-based memristor is often attributed to the formation and rupture of conductive filaments.<sup>[8]</sup> In the Ag/Cu<sub>3</sub>P/ITO device, the application of a positive voltage to the Ag electrode can cause Ag ions to migrate into the Cu<sub>3</sub>P layer, forming a conductive filament and switching the device to a low resistance state (LRS). A negative voltage can rupture this filament, returning the device to a high resistance state (HRS). The native oxide on the Cu<sub>3</sub>P nanoribbons can act as a charge trapping layer, enhancing the stability of the resistive switching.<sup>[7]</sup>

[Click to download full resolution via product page](#)

#### Resistive Switching Mechanism in Ag/Cu<sub>3</sub>P/ITO Memristor

## Conclusion

Copper **phosphide** presents a versatile platform for developing a range of semiconductor devices. The protocols and data presented in this document provide a foundation for researchers to engage with this material system. Further exploration into doping, heterostructuring, and device optimization will undoubtedly unlock the full potential of copper **phosphide** in next-generation electronics. The provided methodologies for synthesis and fabrication are intended to be starting points, and optimization of parameters will be necessary for specific applications and desired device performance.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. universitywafer.com [universitywafer.com]

- 2. researchgate.net [researchgate.net]

- 3. E-beam Evaporation Systems – Denton Vacuum [dentonvacuum.com]

- 4. lithoguru.com [lithoguru.com]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. crystec.com [crystec.com]

- 8. researchgate.net [researchgate.net]

- 9. cityu.edu.hk [cityu.edu.hk]

- To cite this document: BenchChem. [Copper Phosphide in Semiconductor Devices: Application Notes and Protocols]. BenchChem, [2025]. [Online PDF]. Available at: <https://www.benchchem.com/product/b1233454#copper-phosphide-applications-in-semiconductor-devices>

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)