# Troubleshooting low device performance in 3,4-Dimethylthiophene OFETs

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: 3,4-Dimethylthiophene

Cat. No.: B1217622

[Get Quote](#)

## Technical Support Center: 3,4-Dimethylthiophene OFETs

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers and scientists working with Organic Field-Effect Transistors (OFETs) based on **3,4-Dimethylthiophene** and related thiophene compounds.

## Troubleshooting Guide

This guide addresses common performance issues encountered during the fabrication and characterization of **3,4-Dimethylthiophene** OFETs.

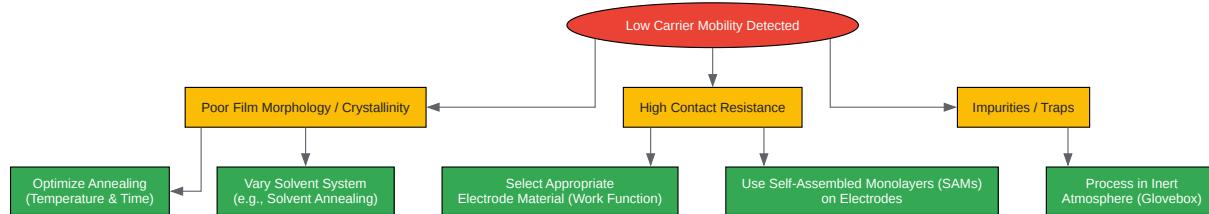

### Issue 1: Why is the charge carrier mobility ( $\mu$ ) of my device lower than expected?

Low carrier mobility is a frequent issue that can originate from several factors related to the morphology of the organic semiconductor film and the device architecture.

- Potential Cause 1: Poor Crystallinity or Molecular Ordering. The charge transport in polycrystalline organic semiconductors is highly dependent on the ordering of the molecules. [1] Disordered films have more grain boundaries and traps, which impede charge carrier movement.

- Solution:

- Optimize Annealing Process: Thermal annealing can significantly improve the crystallinity of the polymer film.[2][3] Systematically vary the annealing temperature and time to find the optimal conditions for your specific **3,4-Dimethylthiophene** derivative.

- Solvent Selection: The choice of solvent and its evaporation rate can influence film morphology. High-boiling-point solvents or solvent annealing techniques can promote the self-organization of polymer chains, leading to more ordered structures.[3]

- Substrate Surface Treatment: A treated substrate surface can enhance the ordering of the first few monolayers of the semiconductor, which form the conductive channel.[1]

• Potential Cause 2: High Contact Resistance. Poor injection of charge carriers from the source electrode into the organic semiconductor can severely limit the measured mobility.[4] This results in an underestimation of the intrinsic material mobility.[5]

• Solution:

- Electrode Material: Ensure the work function of the source/drain electrodes is well-matched with the HOMO level of your p-type **3,4-Dimethylthiophene** semiconductor to minimize the hole injection barrier.[5]

- Self-Assembled Monolayers (SAMs): Treating the electrodes with SAMs, such as pentafluorobenzenethiol (PFBT), can modify their work function and reduce the contact barrier.[6][7]

• Potential Cause 3: Impurities and Trap States. Chemical impurities, moisture, or oxygen can create trap states within the semiconductor or at the dielectric interface, capturing charge carriers and reducing mobility.[8][9]

• Solution:

- Inert Atmosphere: Fabricate and characterize your devices in an inert atmosphere (e.g., a nitrogen-filled glovebox) to minimize exposure to air and moisture.[9]

- Material Purity: Use high-purity materials for the semiconductor, solvent, and dielectric layers.

[Click to download full resolution via product page](#)

Caption: Troubleshooting workflow for low carrier mobility.

Issue 2: My device has a high OFF-state current, leading to a low ON/OFF ratio. What's wrong?

A high OFF-state current (leakage current) compromises the switching behavior of the transistor.

- Potential Cause 1: Gate Leakage. Significant current is flowing through the gate dielectric instead of from source to drain.

- Solution:

- Dielectric Thickness: Ensure your gate dielectric layer is sufficiently thick and free of pinholes. For solution-processed dielectrics, you may need thicknesses greater than 500 nm to avoid shorts.[10]

- Dielectric Material Quality: The choice of dielectric material is crucial. Some polymer dielectrics can be prone to leakage.[11] Consider using a high-quality, thermally grown SiO<sub>2</sub> or a cross-linked polymer dielectric.

- Potential Cause 2: Bulk Conduction. The semiconductor film might be too thick, allowing a significant current to flow through the bulk of the material, independent of the gate voltage.

[12]

- Solution:

- Optimize Film Thickness: Reduce the thickness of the active layer. Thinner films are more effectively depleted of charge carriers at zero gate bias, leading to lower OFF currents.[12]

- Potential Cause 3: Doping from Environment. Unintentional doping, often from oxygen or moisture, can increase the intrinsic conductivity of the semiconductor, leading to a "normally ON" behavior.[9]

- Solution:

- Inert Environment: As with low mobility, processing and measuring in an inert environment is critical to prevent unwanted doping.[9]

Issue 3: I'm observing a large or unstable threshold voltage ( $V_{th}$ ). What does this indicate?

The threshold voltage is the gate voltage required to turn the transistor "on." A large or shifting  $V_{th}$  points to charge trapping.

- Potential Cause 1: Trap States at the Semiconductor/Dielectric Interface. The interface is a critical region where charge accumulation occurs. Defects, impurities, or hydroxyl groups on an untreated  $\text{SiO}_2$  surface can act as charge traps.[13]

- Solution:

- Surface Passivation: Treat the dielectric surface before depositing the semiconductor. For  $\text{SiO}_2$ , common treatments include silanization with agents like octadecyltrichlorosilane (OTS) or hexamethyldisilazane (HMDS) to passivate surface traps and create a more favorable interface for molecular ordering.[14][15]

- Potential Cause 2: Mobile Ions in the Dielectric. Some polymer dielectrics may contain mobile ions that can drift under an applied gate bias, causing a shift in the threshold voltage.

- Solution:

- Select High-Purity Dielectrics: Choose a dielectric material known for its high purity and electrical stability.

## Frequently Asked Questions (FAQs)

Q1: What are typical performance metrics for thiophene-based OFETs?

While specific data for homopolymers of **3,4-Dimethylthiophene** is not widely available, the performance of other solution-processed thiophene-based polymers can provide a useful benchmark.[\[16\]](#) Performance is highly dependent on the specific molecular structure, device architecture, and processing conditions.

Table 1: Performance of Representative Thiophene-Based Polymers in OFETs

| Polymer/Small Molecule        | Deposition Method  | Mobility (cm <sup>2</sup> /Vs) | On/Off Ratio      | Reference            |

|-------------------------------|--------------------|--------------------------------|-------------------|----------------------|

| Poly(3-hexylthiophene) (P3HT) | Solution Shearing  | ~ 0.1                          | > 10 <sup>5</sup> | <a href="#">[16]</a> |

| P3HT                          | Spin Coating       | ~ 9.26 x 10 <sup>-3</sup>      | Not Specified     | <a href="#">[15]</a> |

| PDPP-2S-Se                    | Solution-Processed | ~ 0.59 (hole)                  | > 10 <sup>4</sup> | <a href="#">[16]</a> |

| PffBT4T-2OD/SEBS blend        | Solution-Processed | ~ 8.6                          | Not Specified     | <a href="#">[16]</a> |

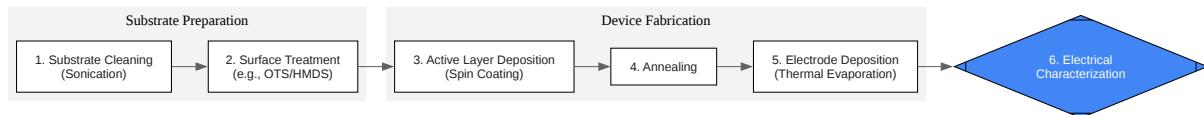

Q2: Can you provide a standard experimental protocol for fabricating a solution-processed thiophene OFET?

The following is a generalized protocol for a bottom-gate, top-contact OFET architecture, which can be adapted for **3,4-Dimethylthiophene** derivatives.[\[14\]](#)[\[15\]](#)

Experimental Protocol: OFET Fabrication

- Substrate Cleaning:

- Use highly doped n-type silicon wafers with a thermally grown  $\text{SiO}_2$  layer (e.g., 200-300 nm) as the gate and gate dielectric.

- Sequentially sonicate the substrates in a cleaning solution (e.g., Hellmanex), deionized water, and isopropanol (IPA).[\[15\]](#)

- Dry the substrates thoroughly with a stream of dry nitrogen.

- Dielectric Surface Treatment (Crucial Step):

- To create a hydrophobic and trap-free surface, treat the  $\text{SiO}_2$  with a silanizing agent. A common method is immersion in an octadecyltrichlorosilane (OTS) solution.[\[14\]](#)

- Alternatively, expose the substrates to hexamethyldisilazane (HMDS) vapor.

- Active Layer Deposition:

- Prepare a solution of the **3,4-Dimethylthiophene** polymer/oligomer in a suitable organic solvent (e.g., chloroform, chlorobenzene, TCB) at a specific concentration (e.g., 5-10 mg/mL).[\[14\]](#)[\[15\]](#)

- Deposit the active layer onto the treated substrate using a technique like spin-coating. The spin speed and time will determine the film thickness.[\[12\]](#)

- Annealing:

- Transfer the substrates to a hot plate in an inert atmosphere (e.g., inside a glovebox).

- Anneal the film at a temperature optimized for the specific material (e.g., 100-150 °C) for a set duration (e.g., 10-30 minutes) to improve film crystallinity.[\[2\]](#)[\[17\]](#)

- Source/Drain Electrode Deposition:

- Using a shadow mask to define the channel length (L) and width (W), thermally evaporate the source and drain electrodes (e.g., 50 nm of Gold) onto the semiconductor film.

- Characterization:

- Measure the output and transfer characteristics of the OFET using a semiconductor parameter analyzer in an inert atmosphere or in the dark to minimize environmental effects.[15]

- Extract key parameters like mobility ( $\mu$ ), on/off ratio, and threshold voltage ( $V_{th}$ ) from the collected data.

[Click to download full resolution via product page](#)

Caption: Standard experimental workflow for OFET fabrication.

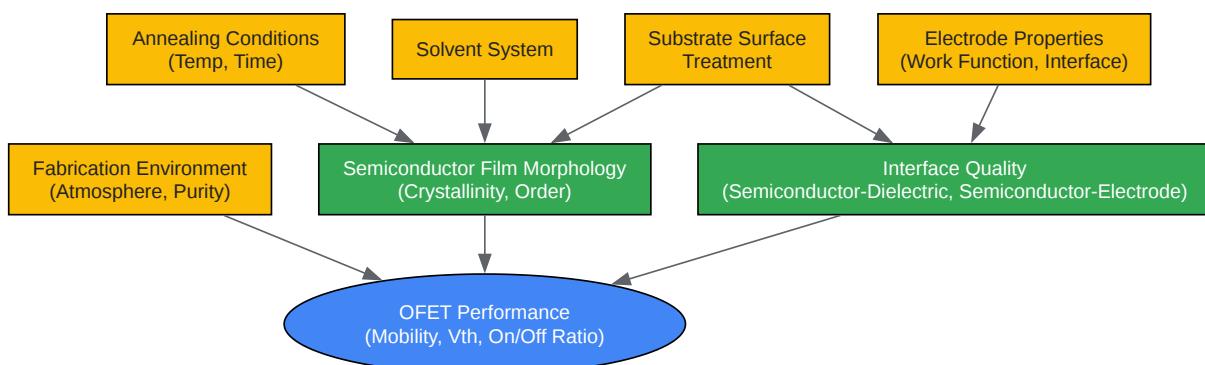

Q3: How do different processing factors influence overall device performance?

Multiple interconnected factors during fabrication determine the final device characteristics. The quality of the interfaces and the morphology of the semiconductor are paramount.

[Click to download full resolution via product page](#)

Caption: Key factors influencing OFET device performance.

**Need Custom Synthesis?**

*BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.*

*Email: [info@benchchem.com](mailto:info@benchchem.com) or Request Quote Online.*

## References

- 1. Easy and cheap fabrication gives brilliant OFET performance [advancedsciencenews.com]

- 2. Effect of annealing on the electronic structure of poly(3-hexylthiophene) thin film - Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. pubs.aip.org [pubs.aip.org]

- 7. Self-forming electrode modification in organic field-effect transistors - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- 11. researchgate.net [researchgate.net]

- 12. researchgate.net [researchgate.net]

- 13. Organic field-effect transistor-based sensors: recent progress, challenges and future outlook - Journal of Materials Chemistry C (RSC Publishing) DOI:10.1039/D4TC04265D [pubs.rsc.org]

- 14. benchchem.com [benchchem.com]

- 15. ossila.com [ossila.com]

- 16. benchchem.com [benchchem.com]

- 17. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Troubleshooting low device performance in 3,4-Dimethylthiophene OFETs]. BenchChem, [2025]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b1217622#troubleshooting-low-device-performance-in-3-4-dimethylthiophene-ofets\]](https://www.benchchem.com/product/b1217622#troubleshooting-low-device-performance-in-3-4-dimethylthiophene-ofets)

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)