# Application Notes and Protocols: Antimony in Semiconductor Manufacturing

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Diantimony*

Cat. No.: *B1203571*

[Get Quote](#)

## Introduction

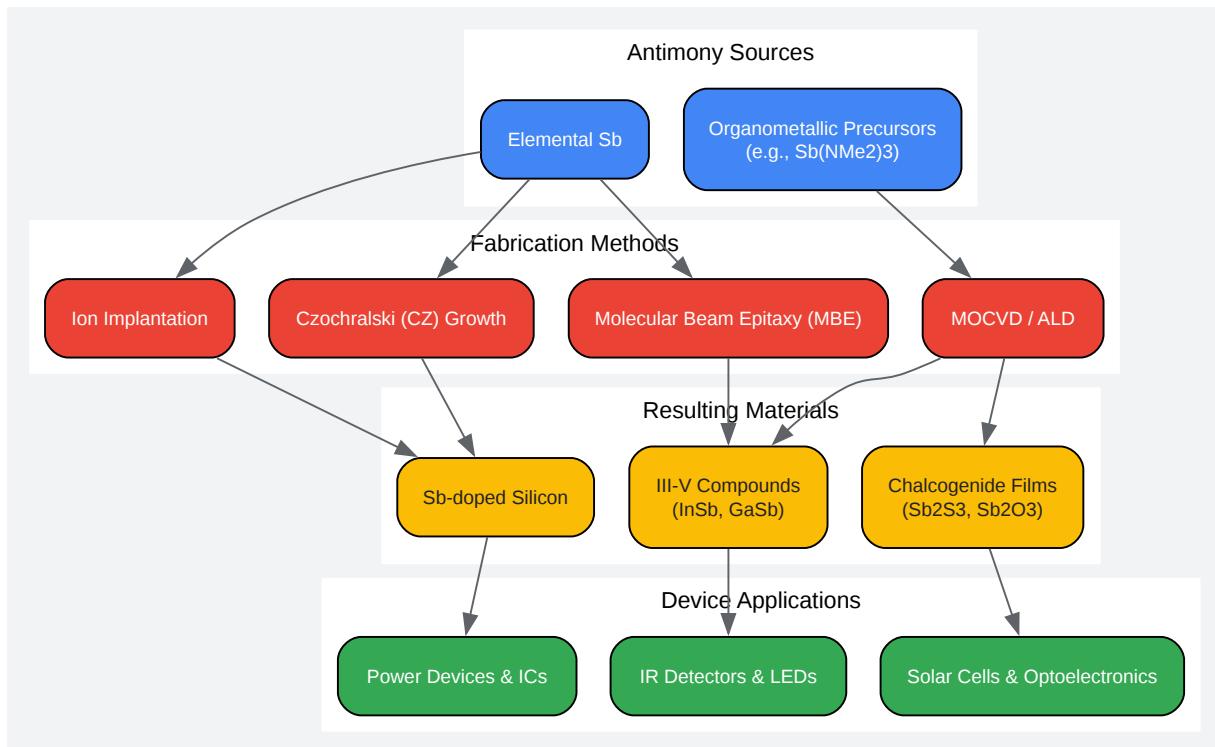

Antimony (Sb) and its compounds are crucial materials in the semiconductor industry, utilized in a range of applications from n-type doping of silicon to the fabrication of advanced III-V compound semiconductors. The term "**diantimony**" typically refers to compounds containing two antimony atoms, such as **diantimony** trioxide ( $Sb_2O_3$ ), or the diatomic molecule  $Sb_2$  observed in the vapor phase. These materials are valued for their specific electronic and physical properties.

This document provides detailed application notes and experimental protocols for the use of antimony in two primary areas:

- N-Type Doping of Silicon: Utilizing elemental antimony for creating n-type regions in silicon wafers through ion implantation and crystal growth methods.

- Fabrication of Antimony-Based Compound Semiconductors: Focusing on materials like Indium Antimonide (InSb), Gallium Antimonide (GaSb), and Antimony Trisulfide ( $Sb_2S_3$ ) for optoelectronic and high-speed device applications.

Antimony offers distinct advantages over other n-type dopants like arsenic and phosphorus, most notably a lower diffusion coefficient. This property allows for the formation of sharper, more abrupt doping profiles and enhanced thermal stability, which is critical for fabricating ultra-shallow junctions in advanced CMOS devices and for high-power electronics.<sup>[1][2]</sup>

Furthermore, heavily antimony-doped silicon substrates exhibit minimal autodoping effects,

making them ideal for epitaxial growth.[2][3] In the realm of compound semiconductors, antimonides are key for infrared detection and high-frequency applications.[4][5]

## Application: N-Type Doping of Silicon with Antimony

Antimony is a well-established n-type dopant for silicon, creating extrinsic semiconductor material by introducing extra electrons that increase conductivity.[6] It is particularly favored for applications requiring high dopant concentrations, minimal diffusion, and thermal stability, such as in power devices and as a buried layer in integrated circuits.[2][7]

## Data Presentation: Properties of Antimony-Doped Silicon

The electrical properties of silicon wafers are highly dependent on the antimony doping concentration and the subsequent processing steps. The following tables summarize key quantitative data for Sb-doped silicon produced by ion implantation and the Czochralski (CZ) growth method.

| Parameter                 | Value                                                 | Conditions / Notes                                       | Reference(s) |

|---------------------------|-------------------------------------------------------|----------------------------------------------------------|--------------|

| Dopant Species            | Antimony (Sb)                                         | N-type dopant                                            | [2][7]       |

| Common Wafer Orientations | <100> or <111>                                        | Standard for IC manufacturing                            | [8]          |

| Typical Resistivity Range | 0.001 - 10 ohm-cm                                     | Heavily doped to lightly doped                           | [8][9]       |

| Key Advantage             | Low Diffusion Coefficient                             | Allows for abrupt junctions and thermal stability        | [2][3]       |

| Applications              | Power Devices, ICs, Epitaxial Substrates, Solar Cells | Suitable for high-temperature and high-frequency devices | [1][7][10]   |

Table 1: General Properties and Applications of Antimony-Doped Silicon.

| Implant Energy (keV) | Implant Dose (ions/cm <sup>2</sup> ) | Annealing Conditions    | Resulting Junction Depth (nm) | Sheet Resistance (Ω/sq) | Reference(s) |

|----------------------|--------------------------------------|-------------------------|-------------------------------|-------------------------|--------------|

| 2 - 5                | 1x10 <sup>15</sup>                   | 600-800°C (RTA)         | < 20                          | -                       | [2]          |

| 5                    | 5x10 <sup>14</sup>                   | 600-800°C (RTA)         | ~22                           | 400                     | [2][11]      |

| 10                   | 6x10 <sup>14</sup>                   | 800°C (RTA)             | 19                            | 260                     | [10]         |

| 40                   | 4x10 <sup>14</sup>                   | < 800°C (RTA)           | ~60                           | < 200                   | [10][11]     |

| 120                  | 2.3x10 <sup>15</sup>                 | 900°C, 30 min (Furnace) | -                             | -                       | [6]          |

Table 2: Quantitative Data for Antimony Ion Implantation into Silicon.

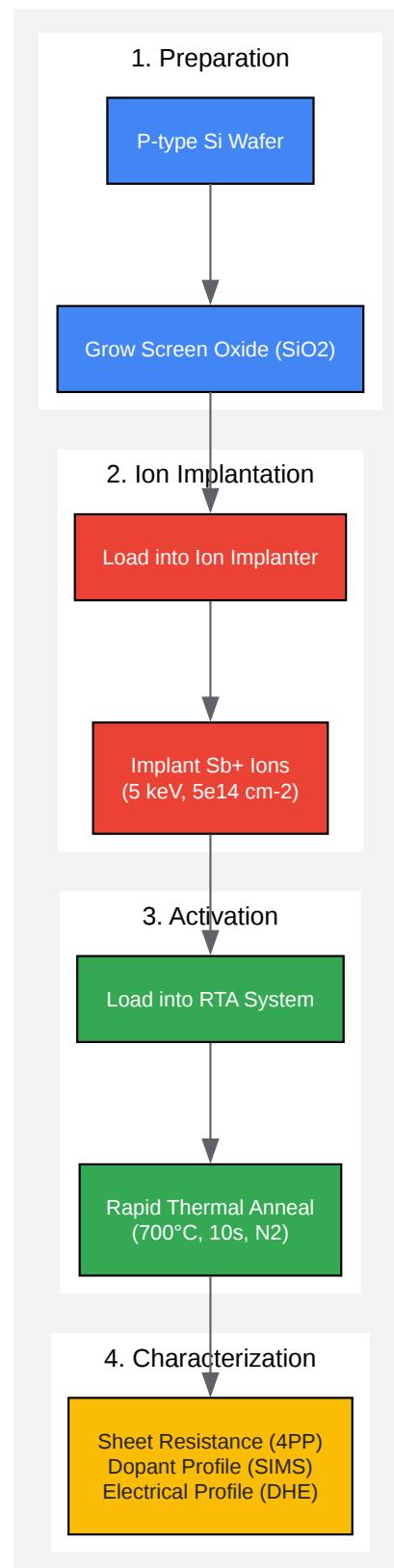

## Experimental Protocol: Ultra-Shallow Junction Formation via Ion Implantation

This protocol outlines a representative process for creating ultra-shallow n<sup>+</sup>/p junctions in silicon using low-energy antimony ion implantation, a critical step for modern CMOS device fabrication.[2][12]

Objective: To form an n-type doped layer with a junction depth of less than 25 nm.

### Materials and Equipment:

- P-type Silicon (Si) wafers, <100> orientation, resistivity 10-20 Ω·cm.

- Ion Implanter capable of low-energy (<10 keV) Sb<sup>+</sup> ion beams.

- Screen oxide layer (SiO<sub>2</sub>, ~2-5 nm), thermally grown.

- Rapid Thermal Annealing (RTA) system.

- Characterization tools: Secondary Ion Mass Spectrometry (SIMS), Four-Point Probe, Differential Hall Effect (DHE) measurement system.

Procedure:

- Substrate Preparation: Start with a clean, p-type silicon wafer. Grow a thin (2-5 nm) screen oxide layer on the surface to minimize ion channeling and protect the silicon surface.

- Ion Implantation:

- Load the wafer into the ion implanter.

- Perform the antimony implantation with the following parameters:

- Ion Species: Sb<sup>+</sup>

- Implant Energy: 5 keV (for junction depths ~20-25 nm)[2][11]

- Implant Dose:  $5 \times 10^{14}$  to  $1 \times 10^{15}$  ions/cm<sup>2</sup>[2]

- Wafer Tilt Angle: 7° off normal to minimize channeling.

- Post-Implantation Annealing:

- Transfer the implanted wafer to the RTA system.

- The annealing step is crucial to repair lattice damage caused by implantation and to electrically activate the antimony dopant atoms.

- Perform the RTA process in a nitrogen (N<sub>2</sub>) ambient with the following parameters:

- Annealing Temperature: 700°C

- Annealing Time: 10 seconds

- Note: A low thermal budget (e.g., 600-800°C) is critical to prevent significant dopant diffusion, preserving the shallow junction profile.[2][10]

- Characterization:

- Measure the sheet resistance of the doped layer using a four-point probe.

- Determine the atomic concentration versus depth profile of Sb using SIMS.

- Measure the electrically active dopant profile and carrier mobility using DHE to confirm junction depth and electrical activation.[\[2\]](#)

## Visualization: Ion Implantation and Annealing Workflow

[Click to download full resolution via product page](#)

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. [researchportalplus.anu.edu.au](http://researchportalplus.anu.edu.au) [researchportalplus.anu.edu.au]

- 2. Research Portal [[openresearch.surrey.ac.uk](http://openresearch.surrey.ac.uk)]

- 3. Electrical properties of Indium Antimonide (InSb) [[ioffe.ru](http://ioffe.ru)]

- 4. [cityu.edu.hk](http://cityu.edu.hk) [cityu.edu.hk]

- 5. researchgate.net [researchgate.net]

- 6. Characterization of silicon surfaces implanted with antimony ions and submitted to annealing and ageing treatments - PubMed [pubmed.ncbi.nlm.nih.gov]

- 7. Electrical Properties of Gallium Indium Antimonide (GaInSb) [ioffe.ru]

- 8. Characterization of Silicon Surfaces Implanted with Antimony Ions...: Ingenta Connect [ingentaconnect.com]

- 9. powerwaywafer.com [powerwaywafer.com]

- 10. researchgate.net [researchgate.net]

- 11. MBE Growth Service of Customized InSb Epilayer for Researches [ganwafer.com]

- 12. Shallow Junction Formation, High Energy Implantation [ebrary.net]

- To cite this document: BenchChem. [Application Notes and Protocols: Antimony in Semiconductor Manufacturing]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1203571#diantimony-in-semiconductor-manufacturing>]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)