# Phenalene in Organic Field-Effect Transistors: A Comparative Performance Guide

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Phenalene**

Cat. No.: **B1197917**

[Get Quote](#)

For Researchers, Scientists, and Drug Development Professionals

The relentless pursuit of novel organic semiconductors with enhanced performance, stability, and processability is a cornerstone of next-generation electronics. Among the diverse array of molecular structures, **phenalene** and its derivatives have emerged as a compelling class of materials for application in Organic Field-Effect Transistors (OFETs). This guide provides a comprehensive assessment of the performance of **phenalene**-based materials in OFETs, offering an objective comparison with the well-established benchmark material, pentacene. This analysis is supported by a summary of key performance metrics from experimental studies, detailed experimental protocols, and visualizations of the device fabrication and characterization workflows.

## Quantitative Performance Comparison

The performance of an OFET is primarily evaluated by its charge carrier mobility ( $\mu$ ), which dictates the switching speed of the transistor, the on/off current ratio ( $I_{on}/I_{off}$ ), which indicates the device's ability to switch between conducting and non-conducting states, and the threshold voltage ( $V_{th}$ ), the minimum gate voltage required to turn the transistor on. The following table summarizes the performance of a **phenalene** derivative in a solution-processed OFET and provides a comparison with a commonly cited high-performance p-type semiconductor, pentacene, also fabricated via solution processing.

| Organic Semiconductor | Device Architecture      | Deposition Method                  | Charge Carrier Mobility ( $\mu$ ) [ $\text{cm}^2/\text{Vs}$ ] | On/Off Ratio (Ion/Ioff)                            | Threshold Voltage (Vth) [V]                        |

|-----------------------|--------------------------|------------------------------------|---------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Phenalene Derivative  | Top-Contact, Bottom-Gate | Solution-Processed                 | Data not available in a directly comparable format            | Data not available in a directly comparable format | Data not available in a directly comparable format |

| TIPS-Pentacene        | Top-Contact, Bottom-Gate | Solution-Processed (Spray-Coating) | 0.191[1]                                                      | > 105                                              | -0.9[1]                                            |

| Pentacene             | Top-Contact, Bottom-Gate | Thermal Evaporation                | 1.10[2]                                                       | 0.48 x 105[2]                                      | -2.71[2]                                           |

Note: A direct, head-to-head comparison of **phenalene** and pentacene OFETs fabricated and characterized under identical conditions is not readily available in the reviewed literature. The data presented for the **phenalene** derivative and pentacene are from separate studies with potentially different experimental parameters, which can significantly influence device performance. Therefore, this table serves as a preliminary reference, and further research with standardized testing conditions is necessary for a definitive comparative assessment.

## Experimental Protocols

The fabrication and characterization of OFETs are intricate processes where minor variations in procedure can lead to significant differences in device performance. Below are detailed methodologies for the fabrication of a solution-processed, top-contact, bottom-gate OFET, a common architecture for evaluating new organic semiconductors, and the subsequent electrical characterization. These protocols are generalized and would require optimization for specific **phenalene** derivatives.

### I. Fabrication of a Top-Contact, Bottom-Gate (TCBG) OFET

This protocol outlines the steps for fabricating a TCBG OFET using a heavily doped silicon wafer as the gate electrode with a thermally grown silicon dioxide ( $\text{SiO}_2$ ) layer as the gate dielectric.

#### 1. Substrate Cleaning:

- The  $\text{Si}/\text{SiO}_2$  substrate is sequentially cleaned in an ultrasonic bath with deionized water, acetone, and isopropyl alcohol for 15 minutes each.

- The substrate is then dried with a stream of nitrogen gas.

- To remove any organic residues, the substrate is treated with UV-ozone for 10 minutes.

#### 2. Dielectric Surface Modification:

- To improve the interface between the dielectric and the organic semiconductor, a self-assembled monolayer (SAM) is often applied.

- For p-type semiconductors, a common treatment is with octadecyltrichlorosilane (OTS). The substrate is immersed in a 10 mM solution of OTS in toluene for 30 minutes in a nitrogen-filled glovebox.

- The substrate is then rinsed with fresh toluene and annealed at 120°C for 10 minutes.

#### 3. Organic Semiconductor Deposition (Solution-Processing):

- A solution of the organic semiconductor (e.g., a **phenalene** derivative) is prepared in a suitable organic solvent (e.g., chloroform, chlorobenzene, or dichlorobenzene) at a specific concentration (e.g., 5-10 mg/mL).

- The solution is then deposited onto the treated  $\text{SiO}_2$  surface via spin-coating. A typical two-step spin-coating process might be:

- 500 rpm for 5 seconds (for spreading).

- 2000 rpm for 60 seconds (for thinning).

- The spin-coating parameters (speed and time) are critical for controlling the film thickness and morphology and must be optimized for the specific material and solvent system.<sup>[3]</sup>

#### 4. Thermal Annealing:

- After deposition, the film is annealed on a hot plate in a nitrogen atmosphere to remove residual solvent and improve the molecular ordering of the semiconductor film.

- The annealing temperature and time are crucial parameters that significantly impact device performance and need to be carefully optimized for each material.<sup>[1]</sup> For example, a post-

deposition annealing step might be at 100-150°C for 30-60 minutes.

### 5. Source and Drain Electrode Deposition:

- Source and drain electrodes are then deposited on top of the organic semiconductor layer through a shadow mask via thermal evaporation.

- Gold (Au) is a common electrode material for p-type semiconductors due to its high work function, which facilitates efficient hole injection. A typical thickness for the electrodes is 40-50 nm.

## II. Electrical Characterization

The electrical performance of the fabricated OFETs is characterized using a semiconductor parameter analyzer in a probe station under an inert atmosphere (e.g., nitrogen or vacuum) to prevent degradation from air and moisture.

### 1. Transfer Characteristics:

- The drain current ( $ID$ ) is measured as a function of the gate voltage ( $VG$ ) at a constant, high drain-source voltage ( $VDS$ ) (saturation regime).

- From the transfer curve, the following parameters are extracted:

- Field-Effect Mobility ( $\mu$ ): Calculated from the slope of the  $(ID)^{1/2}$  vs.  $VG$  plot in the saturation regime.

- On/Off Current Ratio ( $I_{on}/I_{off}$ ): The ratio of the maximum  $ID$  (on-state) to the minimum  $ID$  (off-state).

- Threshold Voltage ( $V_{th}$ ): The  $VG$  at which the transistor begins to conduct, determined from the x-intercept of the linear fit to the  $(ID)^{1/2}$  vs.  $VG$  plot.

### 2. Output Characteristics:

- The drain current ( $ID$ ) is measured as a function of the drain-source voltage ( $VDS$ ) for different constant gate voltages ( $VG$ ).

- The output characteristics confirm the proper transistor operation, showing linear and saturation regions.

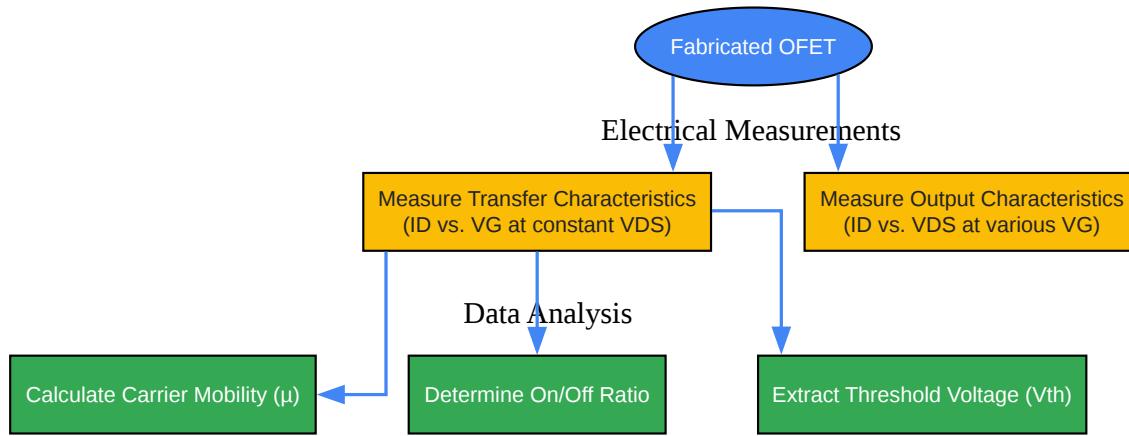

## Visualizing the Workflow

To provide a clear understanding of the experimental processes, the following diagrams, generated using the DOT language, illustrate the logical flow of the OFET fabrication and

characterization procedures.

[Click to download full resolution via product page](#)

Caption: Workflow for Top-Contact, Bottom-Gate OFET Fabrication.

[Click to download full resolution via product page](#)

Caption: Workflow for OFET Electrical Characterization.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Fabrication, TCAD and compact model verification of TIPS-pentacene organic thin film transistor [jos.ac.cn]

- 2. Characteristics of pentacene organic thin film transistor with top gate and bottom contact [cpsjournals.cn]

- 3. ossila.com [ossila.com]

- To cite this document: BenchChem. [Phenalene in Organic Field-Effect Transistors: A Comparative Performance Guide]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1197917#assessing-the-performance-of-phenalene-in-organic-field-effect-transistors>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)