# mitigating leakage current in hafnium-based gate dielectrics

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: **Hafnium**

Cat. No.: **B1195468**

[Get Quote](#)

## Technical Support Center: Hafnium-Based Gate Dielectrics

This technical support center provides troubleshooting guidance and frequently asked questions for researchers, scientists, and professionals working with **hafnium**-based gate dielectrics. The focus is on mitigating leakage current and addressing common experimental issues.

## Troubleshooting Guide

This section addresses specific problems that may be encountered during the fabrication and characterization of **hafnium**-based gate dielectric devices.

### Issue: Unusually High Leakage Current in As-Deposited HfO<sub>2</sub> Films

- Question: My as-deposited HfO<sub>2</sub> film shows a very high leakage current before any annealing. What are the potential causes and how can I fix it?

- Answer: High leakage current in as-deposited films is often due to an amorphous structure with a high density of defects, such as oxygen vacancies and dangling bonds.<sup>[1]</sup> Additionally, residual impurities from precursor molecules can create conductive pathways.<sup>[2]</sup>

- Troubleshooting Steps:

- Verify Deposition Parameters: Ensure that the atomic layer deposition (ALD) or sputtering process parameters are within the optimal window. For ALD, check precursor pulse and purge times to ensure self-limiting growth and prevent unwanted chemical vapor deposition (CVD) reactions.[3][4]

- Precursor Quality: Contaminated or degraded precursors are a common source of impurities. Verify the purity of your **hafnium** precursor (e.g., TDMAH, TDEAH) and oxidant (e.g., H<sub>2</sub>O, O<sub>3</sub>).[5]

- Substrate Preparation: An improperly cleaned silicon surface can lead to poor interface quality and higher leakage. Ensure your pre-deposition cleaning process effectively removes organic and native oxide layers.

- Deposition Temperature: Low deposition temperatures can result in more disordered films with higher impurity content.[6] Conversely, excessively high temperatures can cause precursor decomposition.[3] Operate within the established ALD temperature window for your specific precursors.[7]

#### Issue: Leakage Current Increases After Post-Deposition Annealing (PDA)

- Question: I performed a post-deposition anneal to improve my HfO<sub>2</sub> film quality, but the leakage current increased. Why did this happen?

- Answer: While PDA is intended to densify the film and reduce defects, a significant increase in leakage current post-annealing is typically caused by the crystallization of the HfO<sub>2</sub> film.[8] The formation of polycrystalline structures introduces grain boundaries, which can act as high-leakage pathways.[9][10]

- Troubleshooting Steps:

- Optimize Annealing Temperature: HfO<sub>2</sub> tends to crystallize at temperatures above 500-600°C.[9][11] If your process allows, try annealing at a lower temperature (e.g., 400°C) to densify the film while keeping it in an amorphous state.[12] The optimal annealing temperature is a trade-off between defect reduction and crystallization.[13]

- Incorporate Dopants: Doping the HfO<sub>2</sub> with elements like Aluminum (Al) or Silicon (Si) to form HfAlO or HfSiON can increase the crystallization temperature, allowing for a higher

thermal budget without forming leaky grain boundaries.[8]

- Control Annealing Ambient: Annealing in an oxygen-deficient ambient (like N<sub>2</sub>) can exacerbate the formation of oxygen vacancies, which are electrically active defects. Annealing in a controlled O<sub>2</sub> ambient can help passivate these vacancies.[11][13]

Issue: Poor C-V Characteristics (Frequency Dispersion, Hysteresis, or Flatband Voltage Shifts)

- Question: My Capacitance-Voltage (C-V) measurements show significant frequency dispersion and a large hysteresis loop. What does this indicate?

- Answer: These features point to a high density of traps, either within the bulk of the HfO<sub>2</sub> film or at the HfO<sub>2</sub>/Si interface.[14][15][16] Interface traps (D<sub>it</sub>) can readily charge and discharge, causing frequency dispersion, while slower bulk traps contribute to hysteresis and flatband voltage (V<sup>fB</sup>) instability.[17]

- Troubleshooting Steps:

- Interface Passivation: The interface between silicon and HfO<sub>2</sub> is critical. Growing a thin, high-quality interfacial layer (e.g., SiO<sub>2</sub> or SiON) before HfO<sub>2</sub> deposition can significantly reduce interface trap density.

- Nitrogen Incorporation: Introducing nitrogen, for instance through plasma nitridation or annealing in an N<sub>2</sub> or NH<sub>3</sub> ambient, can passivate defects both in the bulk HfO<sub>2</sub> and at the interface.[8][18][19] This forms a **hafnium** oxynitride (HfON) which can improve electrical properties and thermal stability.[18]

- Post-Metallization Annealing (PMA): A low-temperature anneal (e.g., 400-450°C) in a forming gas (H<sub>2</sub>/N<sub>2</sub>) after gate electrode deposition can help passivate dangling bonds at the Si-dielectric interface.

## Frequently Asked Questions (FAQs)

Q1: What is the most effective method to reduce leakage current in HfO<sub>2</sub>?

A1: There is no single "best" method, as the optimal approach depends on the specific device requirements and process flow. However, a combination of techniques is usually most effective.

This typically involves:

- Doping/Alloying: Incorporating elements like Al, Si, or N to form ternary (e.g., HfAlO, HfSiON) or quaternary compounds. These materials generally have higher crystallization temperatures and can be engineered for better electrical properties.[\[8\]](#) Adding a small amount of Al can reduce leakage by up to six-fold.[\[20\]](#)

- Interface Engineering: Growing a high-quality, ultrathin interfacial layer of SiO<sub>2</sub> or SiON on the silicon substrate before HfO<sub>2</sub> deposition is crucial for minimizing interface traps.

- Optimized Annealing: Performing a carefully controlled post-deposition anneal to passivate bulk defects without causing extensive crystallization.[\[1\]](#)[\[11\]](#)

Q2: How does nitrogen incorporation help in reducing leakage current?

A2: Nitrogen incorporation, typically forming HfON or HfSiON, helps in several ways:

- Increased Crystallization Temperature: Nitrogen helps to keep the dielectric in a more stable amorphous state during subsequent high-temperature processing steps, preventing the formation of leaky grain boundaries.[\[8\]](#)

- Defect Passivation: Nitrogen atoms can passivate oxygen vacancies within the HfO<sub>2</sub> lattice, which are a primary source of trap-assisted tunneling and leakage.[\[18\]](#)

- Improved Interfacial Quality: Nitridation of the interfacial layer can reduce interface trap density and act as a barrier against dopant diffusion from the gate electrode.[\[8\]](#)

Q3: What is trap-assisted tunneling (TAT) and why is it significant in HfO<sub>2</sub>?

A3: Trap-assisted tunneling (TAT) is a major leakage mechanism in HfO<sub>2</sub> and other high-k dielectrics.[\[21\]](#)[\[22\]](#) It is a two-step process where an electron tunnels from the electrode into a defect state (a "trap") within the dielectric's bandgap, and then from the trap into the conduction band of the dielectric or the other electrode. HfO<sub>2</sub> tends to have a higher density of these bulk traps (often linked to oxygen vacancies) compared to SiO<sub>2</sub>, making TAT a dominant leakage pathway, especially at lower electric fields.[\[21\]](#)

Q4: Can I deposit HfO<sub>2</sub> directly on silicon without an interfacial layer?

A4: While it is possible to deposit  $\text{HfO}_2$  directly on a hydrogen-terminated silicon surface, it is generally not recommended for high-performance gate dielectric applications.<sup>[3]</sup> An uncontrolled interfacial layer of **hafnium** silicate ( $\text{HfSi}_x\text{O}_y$ ) often forms anyway.<sup>[3]</sup> This uncontrolled interface typically has a high density of traps, leading to poor C-V characteristics and high leakage.<sup>[23][24]</sup> A deliberately grown, high-quality thin oxide or oxynitride layer provides a much more electrically stable interface.

## Data and Experimental Protocols

### Quantitative Data Summary

The following tables summarize the impact of various processing techniques on the electrical properties of **hafnium**-based dielectrics.

Table 1: Effect of Post-Deposition Annealing (PDA) on  $\text{HfO}_2$  Properties

| Annealing Temp. (°C) | Annealing Ambient | Leakage Current Density @ -1.5V (A/cm²) | Equivalent Oxide Thickness (EOT) (nm) | Film Structure               |

|----------------------|-------------------|-----------------------------------------|---------------------------------------|------------------------------|

| As-deposited         | -                 | High (varies)                           | ~3.5 (example)                        | Amorphous                    |

| 400                  | $\text{N}_2$      | Moderate                                | 2.9                                   | Mostly Amorphous             |

| 600                  | $\text{N}_2$      | Lower                                   | Increases slightly                    | Polycrystalline (monoclinic) |

| 800                  | $\text{N}_2$      | $3.09 \times 10^{-6}$ <sup>[12]</sup>   | Increased                             | Polycrystalline (monoclinic) |

| 1000                 | $\text{O}_2$      | Varies (can increase)                   | Increased                             | Polycrystalline (monoclinic) |

Data synthesized from multiple sources for illustrative comparison.<sup>[11][12]</sup>

Table 2: Effect of Doping on  $\text{HfO}_2$  Properties

| Dielectric Material                      | Dopant Concentration | Leakage                                        |                           |  | Key Benefit                                               |

|------------------------------------------|----------------------|------------------------------------------------|---------------------------|--|-----------------------------------------------------------|

|                                          |                      | Current Reduction (vs. pure HfO <sub>2</sub> ) | EOT Reduction             |  |                                                           |

| HfAlO                                    | < 2% Al/(Al+Hf)      | Up to 6-fold[20]                               | Up to 18%[20]             |  | Increased crystallization temperature, reduced SILC. [20] |

| HfO <sub>2</sub> -ZrO <sub>2</sub> (HZO) | 0.7 mol.% La         | Significant decrease                           | N/A (Ferroelectric focus) |  | Reduced leakage, decreased coercive field. [25]           |

| HfON                                     | Varies               | Significant                                    | Varies                    |  | Increased thermal stability, defect passivation.[8]       |

## Key Experimental Protocols

### Protocol 1: Atomic Layer Deposition (ALD) of HfO<sub>2</sub>

This protocol provides a general procedure for depositing HfO<sub>2</sub> thin films using a thermal ALD process.

- Substrate Preparation:

- Start with a p-type or n-type silicon (100) wafer.

- Perform a standard RCA clean or a simplified Piranha etch (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> solution) followed by an HF dip to remove the native oxide and passivate the surface with hydrogen.

- Immediately transfer the wafer to the ALD reaction chamber to minimize re-oxidation.

- ALD Process Parameters:

- **Hafnium** Precursor: Tetrakis(dimethylamido)**hafnium** (TDMAH) or Tetrakis(ethylmethylamido)**hafnium** (TEMAH).

- Oxidant Precursor: Deionized (DI) water ( $H_2O$ ) or Ozone ( $O_3$ ).

- Carrier Gas: High-purity Nitrogen ( $N_2$ ) or Argon (Ar).

- Deposition Temperature: 180°C - 300°C (A typical temperature is 250°C).[6][7]

- Deposition Cycle:

- Step 1: Precursor Pulse: Pulse the **hafnium** precursor into the chamber (e.g., 0.5 - 1.0 seconds).[3] The precursor molecules will chemisorb onto the substrate surface.

- Step 2: Purge: Purge the chamber with the carrier gas (e.g., 5 - 10 seconds) to remove any unreacted precursor molecules and byproducts.

- Step 3: Oxidant Pulse: Pulse the oxidant (e.g.,  $H_2O$ ) into the chamber (e.g., 0.5 - 1.0 seconds).[3] This reacts with the chemisorbed precursor layer to form a monolayer of  $HfO_2$ .

- Step 4: Purge: Purge the chamber again with the carrier gas (e.g., 5 - 10 seconds) to remove unreacted oxidant and reaction byproducts.

- Film Thickness:

- Repeat the deposition cycle until the desired film thickness is achieved. The growth-per-cycle (GPC) is typically around 1.0 - 1.6 Å/cycle.[6]

- Monitor thickness in-situ with spectroscopic ellipsometry or ex-situ after deposition.

## Protocol 2: Post-Deposition Annealing (PDA)

This protocol describes a typical PDA process to improve the quality of the deposited  $HfO_2$  film.

- Sample Preparation:

- Use the wafer with the as-deposited HfO<sub>2</sub> film.

- Annealing System:

- Use a rapid thermal annealing (RTA) system or a conventional tube furnace.

- Annealing Parameters:

- Temperature: 400°C to 800°C. A lower temperature (~400-500°C) is often chosen to avoid crystallization.[26]

- Ambient: High-purity N<sub>2</sub> for densification, or a dilute O<sub>2</sub>/N<sub>2</sub> mixture to passivate oxygen vacancies.

- Duration: For RTA, 30 - 60 seconds. For a tube furnace, 15 - 30 minutes.[18][26]

- Procedure:

- Load the wafer into the annealing chamber.

- Purge the chamber with the chosen ambient gas.

- Ramp up the temperature to the setpoint.

- Hold at the setpoint temperature for the specified duration.

- Ramp down the temperature and unload the wafer.

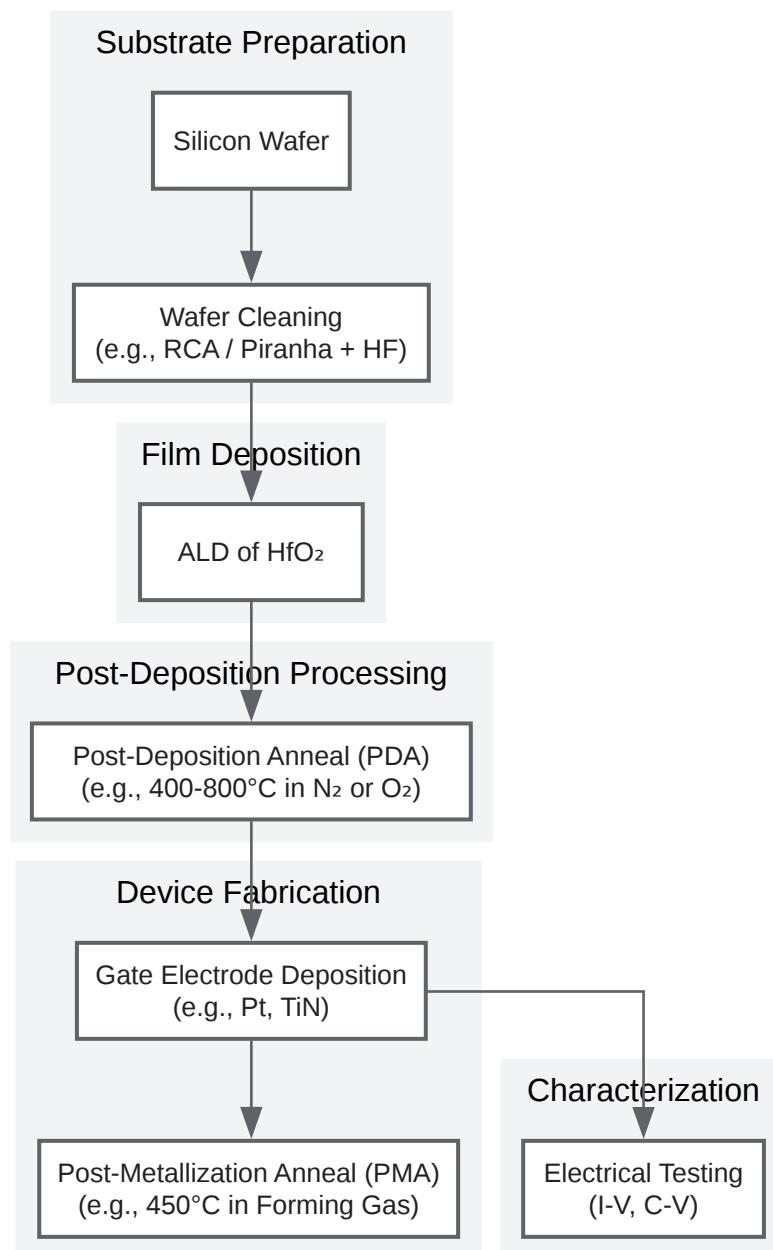

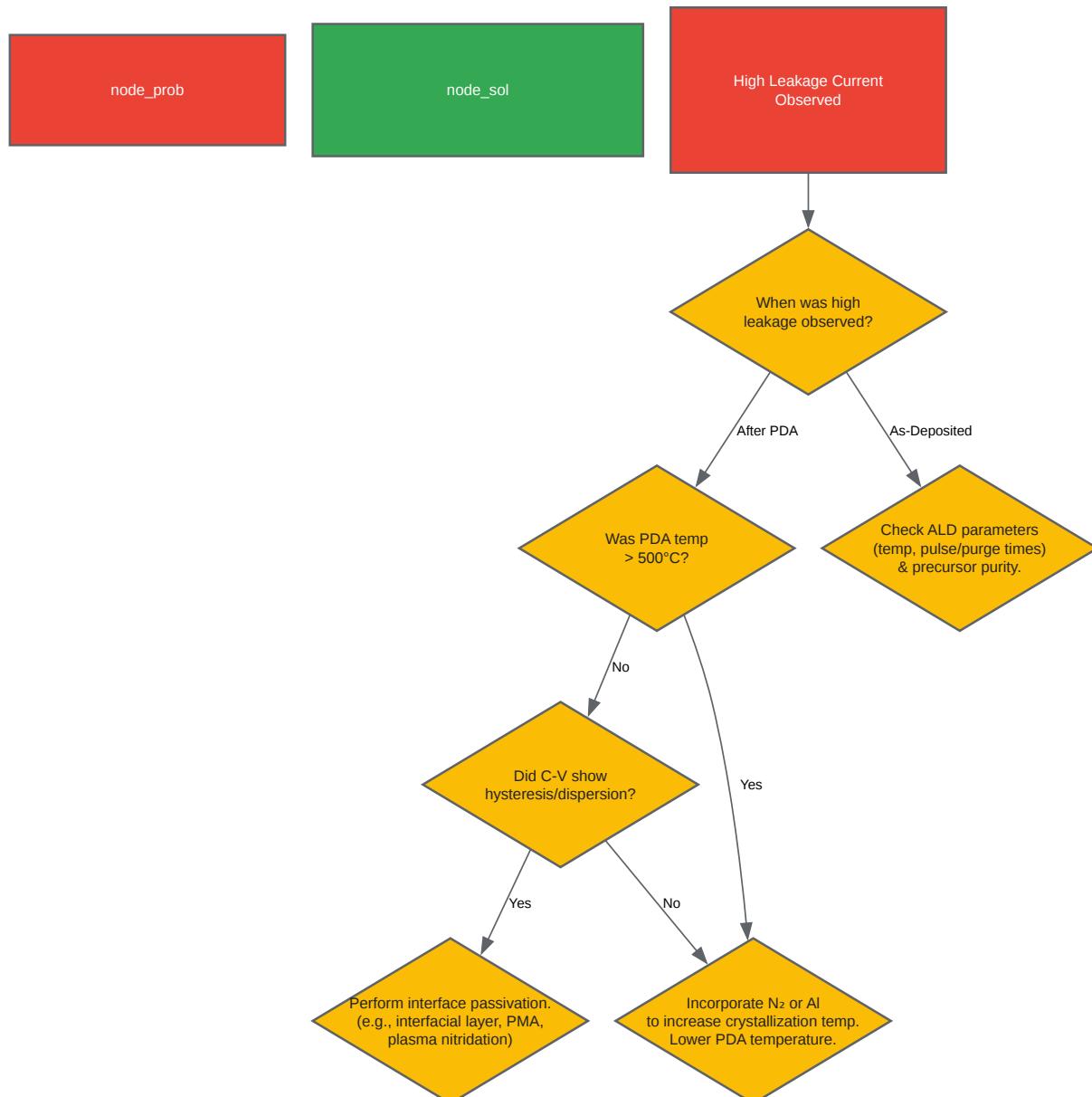

## Visualizations

[Click to download full resolution via product page](#)

Caption: Standard experimental workflow for fabricating and testing HfO<sub>2</sub>-based MOS capacitors.

[Click to download full resolution via product page](#)

Caption: A logical decision tree for troubleshooting high leakage current in HfO<sub>2</sub> gate dielectrics.

**Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. mdpi.com [mdpi.com]

- 2. researchgate.net [researchgate.net]

- 3. web.enr.oregonstate.edu [web.enr.oregonstate.edu]

- 4. researchgate.net [researchgate.net]

- 5. semiengineering.com [semiengineering.com]

- 6. mdpi.com [mdpi.com]

- 7. Atomic layer deposition of HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and HfAlO<sub>x</sub> using O<sub>3</sub> and metal(diethylamino) precursors | Journal of Materials Research | Cambridge Core [cambridge.org]

- 8. cityu.edu.hk [cityu.edu.hk]

- 9. researchgate.net [researchgate.net]

- 10. przyrbwn.icm.edu.pl [przyrbwn.icm.edu.pl]

- 11. arxiv.org [arxiv.org]

- 12. electrochem.org [electrochem.org]

- 13. arxiv.org [arxiv.org]

- 14. Frontiers | Characterization of Interface and Bulk Traps in Ultrathin Atomic Layer-Deposited Oxide Semiconductor MOS Capacitors With HfO<sub>2</sub>/In<sub>2</sub>O<sub>3</sub> Gate Stack by C-V and Conductance Method [frontiersin.org]

- 15. sigroup.sjtu.edu.cn [sigroup.sjtu.edu.cn]

- 16. researchgate.net [researchgate.net]

- 17. Stress-induced leakage current and defect generation in nFETs with HfO<sub>2</sub>/TiN gate stacks during positive-bias temperature stress | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 18. cityu.edu.hk [cityu.edu.hk]

- 19. researchgate.net [researchgate.net]

- 20. researchgate.net [researchgate.net]

- 21. briefs.techconnect.org [briefs.techconnect.org]

- 22. lup.lub.lu.se [lup.lub.lu.se]

- 23. pubs.aip.org [pubs.aip.org]

- 24. csqs.xjtu.edu.cn [csqs.xjtu.edu.cn]

- 25. pubs.aip.org [pubs.aip.org]

- 26. mdpi.com [mdpi.com]

- To cite this document: BenchChem. [mitigating leakage current in hafnium-based gate dielectrics]. BenchChem, [2025]. [Online PDF]. Available at: [\[https://www.benchchem.com/product/b1195468#mitigating-leakage-current-in-hafnium-based-gate-dielectrics\]](https://www.benchchem.com/product/b1195468#mitigating-leakage-current-in-hafnium-based-gate-dielectrics)

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [\[Contact our Ph.D. Support Team for a compatibility check\]](#)

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)