# Application Notes: Hafnium Oxide (HfO<sub>2</sub>) as a High-k Dielectric in Microelectronics

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Hafnium*

Cat. No.: *B1195468*

[Get Quote](#)

## 1. Introduction: The Scaling Challenge in Semiconductor Devices

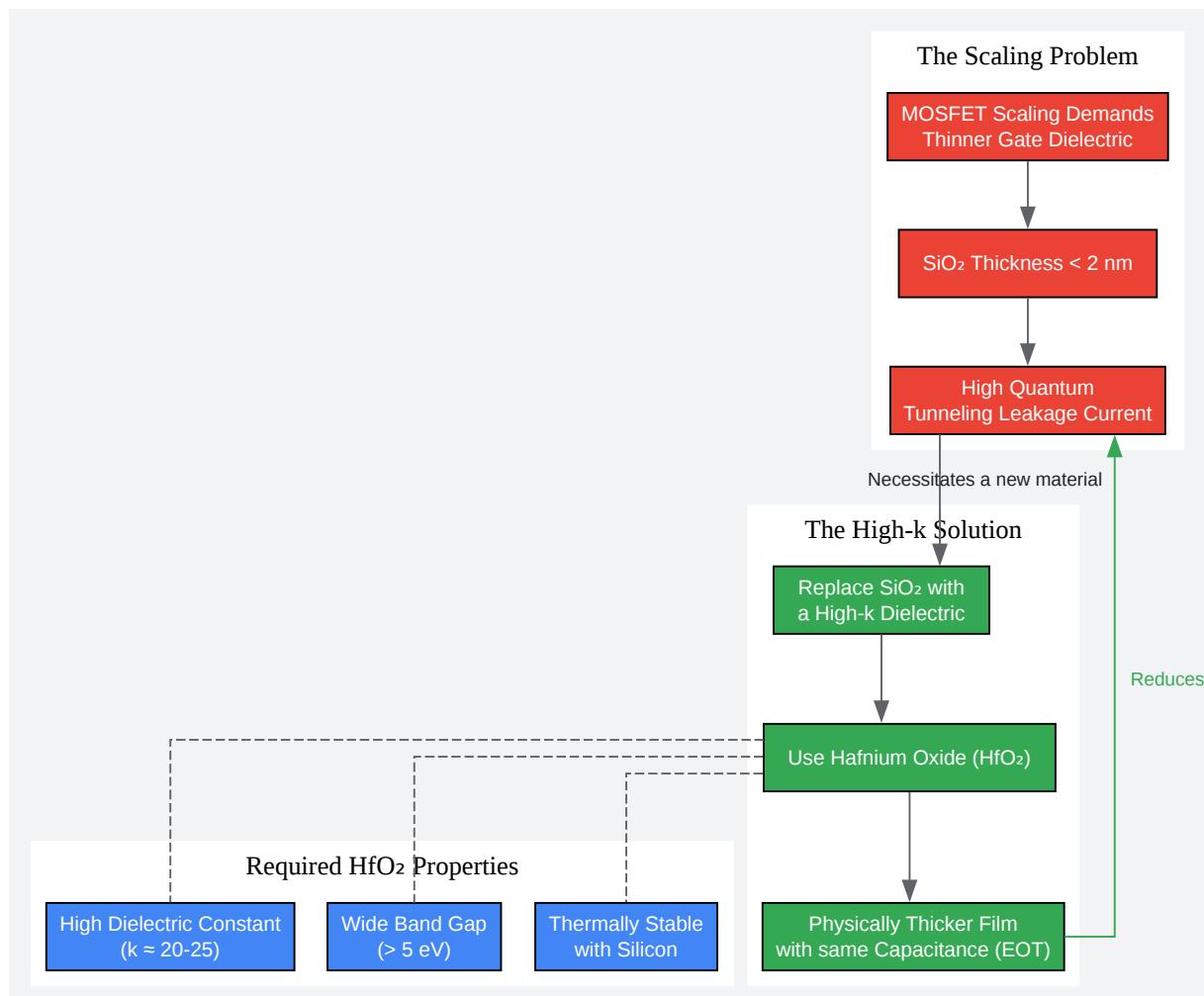

For decades, the continuous miniaturization of metal-oxide-semiconductor field-effect transistors (MOSFETs), the fundamental building blocks of modern microchips, has been guided by Moore's Law.<sup>[1][2]</sup> This trend has been enabled by progressively thinning the silicon dioxide (SiO<sub>2</sub>) gate dielectric layer to maintain the necessary gate capacitance for controlling the transistor channel. However, as this SiO<sub>2</sub> layer approaches a thickness of just a few atomic layers (< 1.5-2.0 nm), quantum tunneling effects become significant, leading to a dramatic increase in gate leakage current.<sup>[1][2][3][4]</sup> This leakage results in excessive power consumption, heat generation, and reduced device reliability, posing a fundamental barrier to further scaling.<sup>[2][5]</sup>

To overcome this challenge, the semiconductor industry has transitioned to using "high-k" dielectric materials. A high-k dielectric possesses a significantly higher dielectric constant (k) than SiO<sub>2</sub> (k ≈ 3.9). This allows for the deposition of a physically thicker insulating layer that provides the same equivalent oxide thickness (EOT) and capacitance as a much thinner SiO<sub>2</sub> layer, thereby drastically reducing leakage current while maintaining transistor performance.<sup>[1][3]</sup>

## 2. Hafnium Oxide (HfO<sub>2</sub>): The Material of Choice

Among various high-k candidates, **hafnium** oxide (HfO<sub>2</sub>) has emerged as the industry standard and one of the most suitable replacements for SiO<sub>2</sub>.<sup>[3][6][7]</sup> Intel first introduced **hafnium**-

based high-k dielectrics in its 45 nm processors in 2007.[2][6][8] The suitability of HfO<sub>2</sub> stems from a combination of advantageous properties:

- High Dielectric Constant: HfO<sub>2</sub> exhibits a dielectric constant in the range of 20-25, approximately 4-6 times higher than that of SiO<sub>2</sub>.[8][9] This allows for a significant increase in physical thickness for the same EOT, effectively suppressing leakage currents.

- Wide Band Gap: With a band gap of about 5.3-6.0 eV, HfO<sub>2</sub> provides a sufficient energy barrier to electrons and holes, contributing to its excellent insulating properties.[8][9][10][11]

- Thermal Stability: HfO<sub>2</sub> is thermodynamically stable when in direct contact with silicon, which is crucial for withstanding the high-temperature manufacturing processes of microchips.[3][6][7][12]

- Process Compatibility: HfO<sub>2</sub> can be deposited using established semiconductor manufacturing techniques like Atomic Layer Deposition (ALD), which offers precise, atomic-level control over film thickness and uniformity.[13][14]

### 3. Key Applications in Microchips

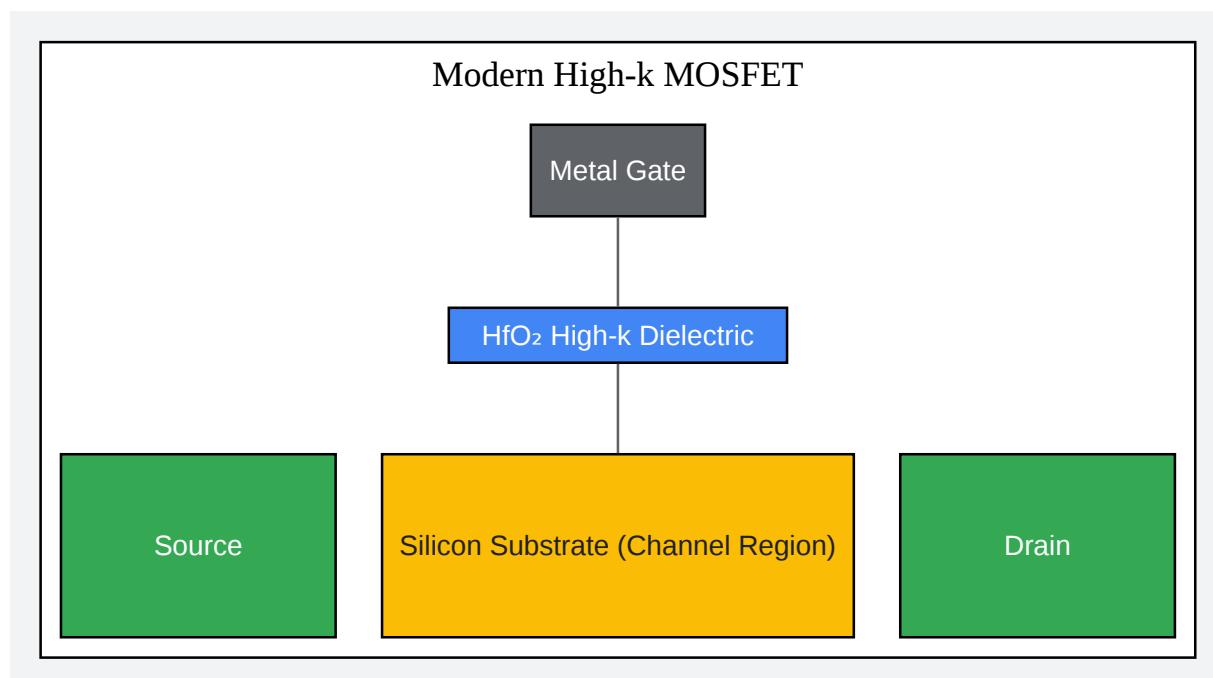

- Gate Dielectric in CMOS Transistors: This is the primary application of HfO<sub>2</sub>. By replacing SiO<sub>2</sub>, it has enabled the continued scaling of logic transistors (e.g., in CPUs and GPUs) to advanced nodes (45nm and beyond), including modern FinFET architectures.[2][6][7]

- Capacitors in DRAM: HfO<sub>2</sub> is used as the dielectric material in deep trench capacitors for Dynamic Random-Access Memory (DRAM) cells, where its high-k value allows for high-density charge storage in a small footprint.[8]

- Emerging Memory Technologies: The unique properties of HfO<sub>2</sub>, particularly its ferroelectric phases, are being harnessed for next-generation non-volatile memory devices like Ferroelectric FETs (FeFETs) and resistive-switching memories (RRAM).[6][8][11]

## Data Presentation

Table 1: Comparison of Gate Dielectric Material Properties

| Property                               | Silicon Dioxide<br>(SiO <sub>2</sub> ) | Hafnium Oxide<br>(HfO <sub>2</sub> )              | Other High-k<br>Candidates<br>(Typical)                                                        |

|----------------------------------------|----------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------|

| Dielectric Constant (k)                | ~3.9[8]                                | 18 - 25[8][9][11][13]                             | Al <sub>2</sub> O <sub>3</sub> : ~9, ZrO <sub>2</sub> : ~25,<br>TiO <sub>2</sub> : ~80[7][9]   |

| Band Gap (eV)                          | ~9                                     | 5.3 - 6.0[8][9][10][11]                           | Al <sub>2</sub> O <sub>3</sub> : ~9, ZrO <sub>2</sub> : ~5.8,<br>TiO <sub>2</sub> : ~3.5[3][7] |

| Conduction Band<br>Offset with Si (eV) | ~3.2                                   | 1.4 - 2.0[9]                                      | > 1.0 is required[3]                                                                           |

| Crystallization<br>Temperature (°C)    | Amorphous                              | ~500 (can be<br>increased by alloying)<br>[8][12] | Varies                                                                                         |

| Thermodynamic<br>Stability with Si     | Excellent                              | Good[3][6]                                        | Some materials are<br>reactive (e.g., TiO <sub>2</sub> )[7]                                    |

Table 2: Typical Electrical Properties of HfO<sub>2</sub> Thin Films

| Deposition Method                | Dielectric Constant<br>(k) | Leakage Current<br>Density @ 1 MV/cm<br>(A/cm <sup>2</sup> ) | Breakdown Field<br>(MV/cm) |

|----------------------------------|----------------------------|--------------------------------------------------------------|----------------------------|

| Atomic Layer<br>Deposition (ALD) | 12 - 20[13][15]            | ~10 <sup>-8</sup> - 10 <sup>-9</sup>                         | > 4                        |

| Sputtering                       | ~21[10]                    | ~10 <sup>-7</sup>                                            | ~6.5[12]                   |

| High-k Sputtering<br>(HiTUS)     | ~30[11]                    | ~10 <sup>-9</sup> - 10 <sup>-8</sup> [11]                    | > 3[11]                    |

| Solution Processed               | ~10.2[16]                  | ~10 <sup>-9</sup> [16]                                       | ~6[16]                     |

## Experimental Protocols

### Protocol 1: Atomic Layer Deposition (ALD) of HfO<sub>2</sub> Thin Films

This protocol describes a typical thermal ALD process for depositing  $\text{HfO}_2$  on a silicon substrate using a metal-organic precursor and water as the oxidant.

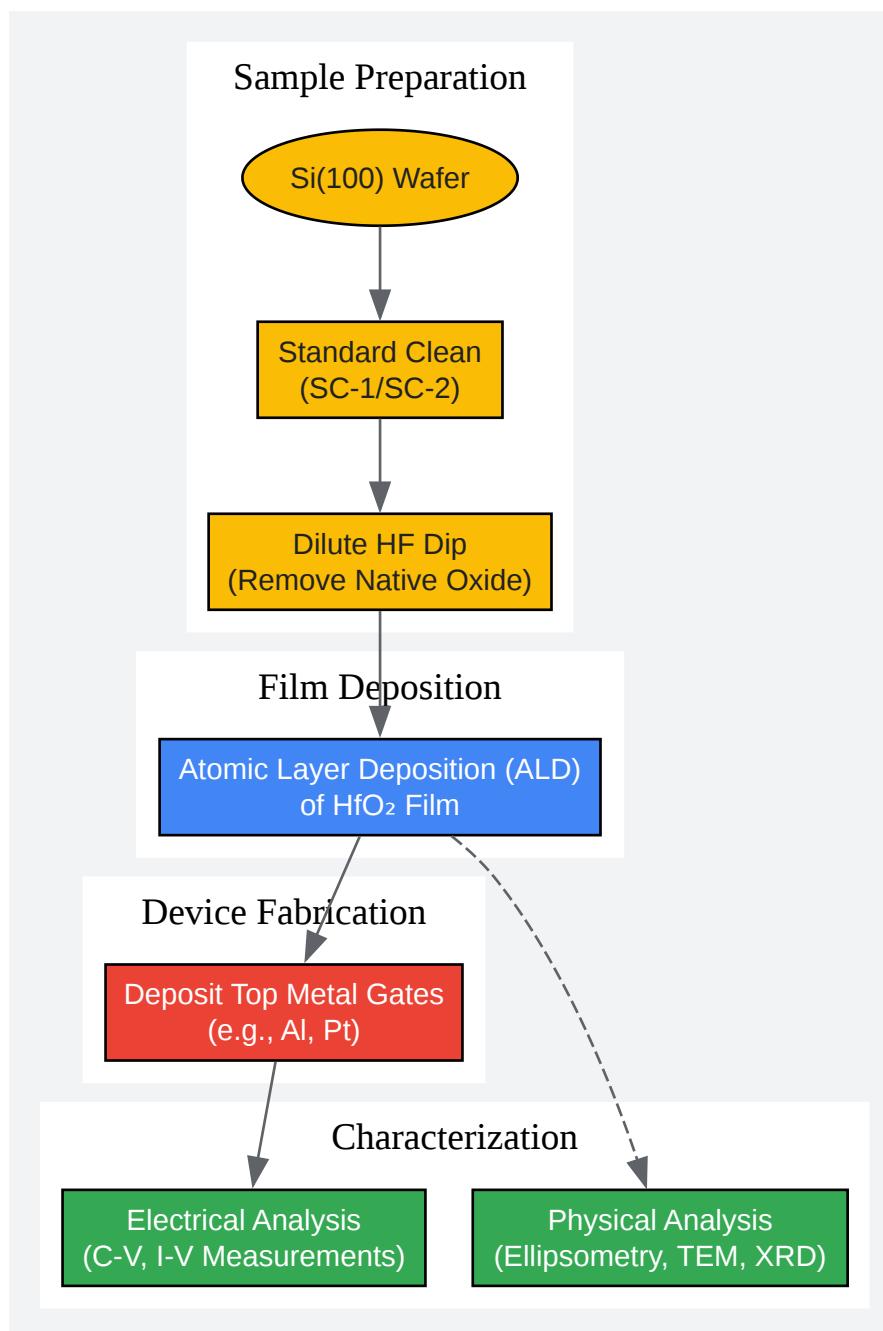

1. Substrate Preparation: a. Start with a p-type Si(100) wafer. b. Perform a standard cleaning procedure (e.g., SC-1 and SC-2 solutions) to remove organic and metallic contaminants. c. To create a hydrogen-terminated surface, dip the substrate in a dilute hydrofluoric acid (HF) solution (e.g., 1% HF) immediately before loading it into the ALD reactor.[15][17] This step removes the native silicon oxide layer.

2. ALD Process Parameters: a. Precursor: Tetrakis(ethylmethylamino)**hafnium** (TEMAH) or Tetrakis(diethylamino)**hafnium** (TDEAH).[17][18] b. Oxidant: Deionized (DI) water ( $\text{H}_2\text{O}$ ) vapor.[15][17] c. Substrate Temperature: 250 - 300 °C.[17][18] This temperature is within the "ALD window" where self-limiting surface reactions occur without precursor decomposition or condensation. d. Carrier Gas: High-purity Nitrogen ( $\text{N}_2$ ) or Argon (Ar).

3. Deposition Cycle (repeated to achieve desired thickness): a. Step 1 (Precursor Pulse): Pulse the Hf precursor (e.g., TEMAH) into the reactor chamber for 0.5 - 1.0 seconds.[18] The precursor molecules will chemisorb onto the substrate surface. b. Step 2 (Purge): Purge the chamber with the inert carrier gas for 5 - 10 seconds to remove any unreacted precursor molecules and byproducts from the gas phase.[17] c. Step 3 (Oxidant Pulse): Pulse the  $\text{H}_2\text{O}$  vapor into the chamber for 0.5 - 0.8 seconds.[15][17] The water molecules react with the precursor layer on the surface to form a monolayer of  $\text{HfO}_2$ . d. Step 4 (Purge): Purge the chamber again with the inert carrier gas for 5 - 10 seconds to remove unreacted water and reaction byproducts.

4. Film Growth: a. One complete cycle deposits a single atomic layer of  $\text{HfO}_2$ . The growth rate is typically ~1.0 - 1.6 Å per cycle.[17][18] b. Repeat the cycle until the target film thickness is achieved. For a 5 nm film, this would require approximately 30-50 cycles.

5. Post-Deposition Annealing (Optional): a. An anneal in a controlled atmosphere (e.g.,  $\text{N}_2$ ) at temperatures from 400-800 °C can be performed to densify the film, remove impurities, and control its crystalline phase.[7][12]

Protocol 2: Electrical Characterization of  $\text{HfO}_2$  using a MOS Capacitor

This protocol outlines the fabrication and measurement of a Metal-Oxide-Semiconductor (MOS) capacitor to extract key electrical properties of the deposited  $\text{HfO}_2$  film.

1. MOS Capacitor Fabrication:

- a. Deposit the  $\text{HfO}_2$  film on a silicon wafer as described in Protocol 1.

- b. Deposit top metal electrodes (gates) onto the  $\text{HfO}_2$  surface. This is typically done by sputtering or evaporation of a metal like Aluminum (Al), Platinum (Pt), or Titanium Nitride (TiN) through a shadow mask to define circular dots of a known area (e.g., 100  $\mu\text{m}$  diameter).

- c. Create a bottom contact by scratching the backside of the silicon wafer and applying a conductive material like Indium Gallium eutectic or Aluminum to ensure a good ohmic contact.

2. Capacitance-Voltage (C-V) Measurement:

- a. Objective: To determine the dielectric constant ( $k$ ), equivalent oxide thickness (EOT), and fixed charge density ( $Q_f$ ).

- b. Procedure:

- i. Place the wafer on a probe station. Contact the top electrode and the bottom contact with microprobes connected to an LCR meter.

- ii. Sweep the DC voltage applied to the gate from a negative value (e.g., -3 V) to a positive value (e.g., +3 V) and back, while superimposing a small AC signal (e.g., 100 kHz, 30 mV).

- iii. Record the capacitance at each DC voltage step.

- c. Data Analysis:

- i. From the resulting C-V plot, identify the accumulation capacitance ( $C_{\text{ox}}$ ), which is the maximum capacitance value.

- ii. Calculate the EOT using the formula:  $\text{EOT} = (k_{\text{SiO}_2} * \epsilon_0 * A) / C_{\text{ox}}$ , where  $k_{\text{SiO}_2}$  is the dielectric constant of  $\text{SiO}_2$  (3.9),  $\epsilon_0$  is the vacuum permittivity, and  $A$  is the electrode area.

- iii. Calculate the dielectric constant of the  $\text{HfO}_2$  film using:  $k_{\text{HfO}_2} = (C_{\text{ox}} * t_{\text{phys}}) / (\epsilon_0 * A)$ , where  $t_{\text{phys}}$  is the physical thickness of the  $\text{HfO}_2$  film (measured by ellipsometry or TEM).

3. Current-Voltage (I-V) Measurement:

- a. Objective: To determine the leakage current density and the dielectric breakdown field.

- b. Procedure:

- i. Using a semiconductor parameter analyzer, apply a sweeping DC voltage across the MOS capacitor (from 0 V to a higher voltage, e.g., 10 V) and measure the resulting current.

- c. Data Analysis:

- i. Plot the leakage current density ( $J = I/A$ ) versus the applied electric field ( $E = V/t_{\text{phys}}$ ).

- ii. The leakage current density at a specific field (e.g., 1 MV/cm) is a key metric for performance.

- iii. The breakdown field is the electric field at which a sudden, irreversible increase in current occurs, indicating the failure of the dielectric.

## Visualizations

[Click to download full resolution via product page](#)

Caption: Logical flow from the SiO<sub>2</sub> scaling problem to the HfO<sub>2</sub> solution.

[Click to download full resolution via product page](#)

Caption: Workflow for  $\text{HfO}_2$  film deposition and characterization.

[Click to download full resolution via product page](#)

Caption: Simplified structure of a MOSFET with a HfO<sub>2</sub> high-k gate dielectric.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Ascensus [ascensusspecialties.com]

- 2. physicstoday.aip.org [physicstoday.aip.org]

- 3. cityu.edu.hk [cityu.edu.hk]

- 4. Looking at High-K Thin Film Depositions With Multiple Surface Analysis Techniques - Advancing Materials [thermofisher.com]

- 5. GT Digital Repository [repository.gatech.edu]

- 6. Note from the Nanoworld: Hafnium Oxide Helps Keep Microelectronics on the Moore's Law Trajectory [afm.oxinst.com]

- 7. przyrbwn.icm.edu.pl [przyrbwn.icm.edu.pl]

- 8. Hafnium(IV) oxide - Wikipedia [en.wikipedia.org]

- 9. par.nsf.gov [par.nsf.gov]

- 10. pubs.aip.org [pubs.aip.org]

- 11. hofmann-group.eng.cam.ac.uk [hofmann-group.eng.cam.ac.uk]

- 12. Studies of Electrical Parameters and Thermal Stability of HiPIMS Hafnium Oxynitride (HfO<sub>x</sub>Ny) Thin Films - PMC [pmc.ncbi.nlm.nih.gov]

- 13. pubs.aip.org [pubs.aip.org]

- 14. researchgate.net [researchgate.net]

- 15. web.engr.oregonstate.edu [web.engr.oregonstate.edu]

- 16. Low-temperature fabrication of solution-processed hafnium oxide gate insulator films using a thermally purified solution process - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 17. pubs.aip.org [pubs.aip.org]

- 18. Microstructures of HfO<sub>x</sub> Films Prepared via Atomic Layer Deposition Using La(NO<sub>3</sub>)<sub>3</sub>·6H<sub>2</sub>O Oxidants - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Application Notes: Hafnium Oxide (HfO<sub>2</sub>) as a High-k Dielectric in Microelectronics]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b1195468#applications-of-hafnium-oxide-as-a-high-k-dielectric-in-microchips>]

---

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

## Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)