# troubleshooting low yield in Silicon-28 device fabrication

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: *Silicon28*

Cat. No.: *B1172460*

[Get Quote](#)

## Technical Support Center: Silicon-28 Device Fabrication

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to help researchers, scientists, and drug development professionals address common challenges that lead to low yield in Silicon-28 (Si-28) device fabrication.

## Troubleshooting Guides

This section offers detailed solutions to specific problems encountered during the fabrication process, presented in a question-and-answer format.

## Category 1: Material and Substrate Issues

Question: What are the primary material-related causes of low device yield?

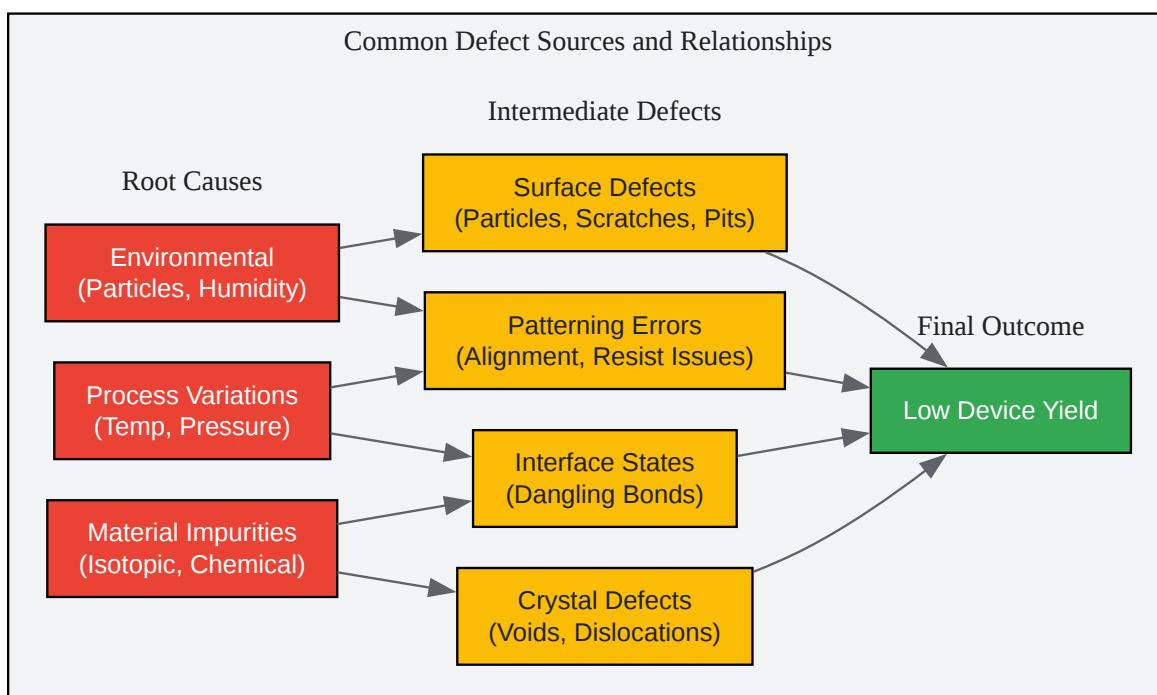

Answer: The quality of the initial Silicon-28 wafer is a critical factor influencing the final device yield.[\[1\]](#)[\[2\]](#) Even minute impurities or crystalline defects in the silicon can cause chips to fail.[\[2\]](#)

Key material-related issues include:

- Isotopic Purity: For quantum applications, high isotopic purity of Silicon-28 is essential to protect qubits from sources of decoherence.[\[3\]](#)[\[4\]](#) The presence of the Silicon-29 isotope, with its nuclear spin, can disrupt the delicate quantum properties of the device.[\[3\]](#)[\[4\]](#) While

quantum computing often requires 99.99% Si-28 purity or higher, other applications might have different specifications.[5]

- Chemical Purity: The raw polycrystalline silicon must be of extremely high purity (>99.9999%) to be considered electronic-grade silicon (EGS).[6] Contaminants such as carbon, oxygen, and various metals can introduce deep defect levels that are detrimental to device performance.[6][7]

- Crystalline Defects: Irregularities in the crystal lattice structure, such as voids, dislocations, or stacking faults, can impede carrier flow and reduce carrier mobility.[8][9] These defects can arise during the Czochralski (CZ) or float-zone (FZ) single-crystal growth process.[7][10]

Question: How can I diagnose and mitigate substrate quality problems?

Answer: Diagnosing substrate issues requires a combination of material analysis and process control.

Diagnostic Protocols:

- Secondary Ion Mass Spectrometry (SIMS): Use SIMS to verify the isotopic enrichment of your Si-28 wafer and to quantify the concentration of key impurities like oxygen and carbon.

- Defect Etching and Inspection: Carefully etch the wafer surface to reveal crystalline defects, which can then be inspected and counted using optical microscopy or scanning electron microscopy (SEM).[8]

- Photoluminescence (PL) or Carrier Lifetime Measurements: These non-destructive techniques can provide an overall assessment of material quality and the presence of recombination-active defects.

Mitigation Strategies:

- Source High-Purity Material: Procure Si-28 wafers from reputable suppliers who provide detailed certificates of analysis for isotopic and chemical purity. The conversion of enriched SiF<sub>4</sub> gas to elemental silicon must be done carefully to avoid isotopic contamination.[5]

- Optimize Crystal Growth: If growing your own crystals, carefully control parameters during the CZ or FZ process to minimize the incorporation of impurities and the formation of structural defects.[7]

- Implement Incoming Quality Control: Establish a routine inspection process for all new wafers to check for surface defects like scratches, pits, or particles before beginning fabrication.[9]

Table 1: Common Impurities in Silicon and Their Impact

| Impurity            | Typical Concentration Limit (EGS) | Primary Impact on Device Performance                                                                                              |

|---------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Oxygen              | < a few ppm                       | Can form precipitates and clusters during thermal processing, acting as unwanted shallow donors.[6] [10]                          |

| Carbon              | < a few ppm                       | Can interact with oxygen to form complexes and may lead to the formation of silicon carbide precipitates.[10]                     |

| Metals (Fe, Cu, Au) | ppb range or lower                | Introduce deep-level defects that act as recombination centers, reducing carrier lifetime and degrading electrical properties.[7] |

| Boron/Phosphorus    | ppb range or lower                | Unintentional doping affects the background carrier concentration and resistivity of the substrate.[7]                            |

## Category 2: Surface Preparation and Passivation

Question: My device suffers from high leakage currents. How can I improve surface passivation?

Answer: High leakage currents are often a symptom of poor surface passivation, which leads to a high density of electrically active defects at the semiconductor-dielectric interface.[11][12] These defects act as recombination centers for charge carriers.[12] Effective passivation is crucial for minimizing these unwanted recombination pathways.[13]

Effective passivation can be achieved through two main mechanisms:

- Chemical Passivation: This involves reducing the density of interface defect sites ( $D_{it}$ ), for example, by saturating "dangling bonds" with chemical bonds.[12]

- Field-Effect Passivation: This method uses an electric field, often induced by fixed charges ( $Q_p$ ) in a dielectric layer, to repel one type of charge carrier (electrons or holes) from the surface.[12]

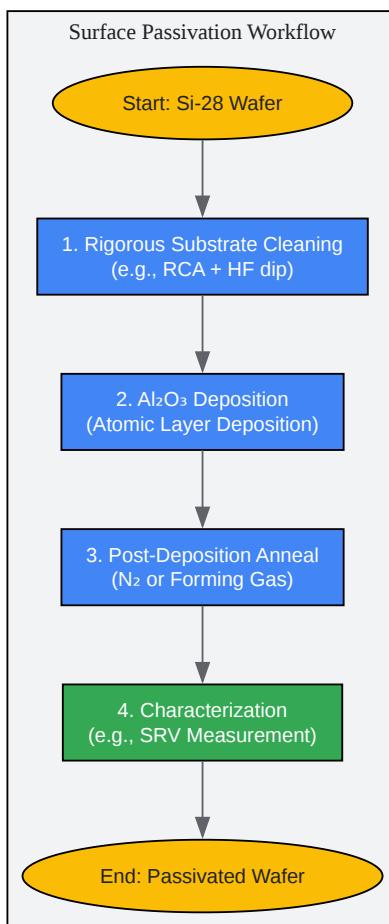

#### Experimental Protocol: $\text{Al}_2\text{O}_3$ Surface Passivation via Atomic Layer Deposition (ALD)

- Substrate Cleaning: Begin with a rigorous cleaning procedure (e.g., RCA clean) to remove organic and metallic contaminants. The final step should be a dip in dilute hydrofluoric (HF) acid to remove the native oxide layer, leaving a hydrogen-terminated surface.

- ALD Deposition: Immediately transfer the wafer to an ALD chamber. Deposit a thin film of aluminum oxide ( $\text{Al}_2\text{O}_3$ ), typically a few nanometers thick. ALD provides excellent control over film thickness and uniformity.[12]  $\text{Al}_2\text{O}_3$  is known to provide a high density of negative fixed charges, making it excellent for passivating p-type silicon surfaces.[14]

- Post-Deposition Annealing (PDA): After deposition, anneal the wafer in a nitrogen ( $\text{N}_2$ ) or forming gas ( $\text{N}_2/\text{H}_2$ ) ambient. This step is critical for activating the passivation properties of the  $\text{Al}_2\text{O}_3$  layer.

- Characterization: Measure the effective surface recombination velocity (SRV) to quantify the quality of the passivation. Outstandingly low SRVs (below 10 cm/s) are achievable with optimized processes.[15]

For enhanced thermal stability, a capping layer of silicon nitride ( $\text{SiN}_x$ ) can be deposited on top of the  $\text{Al}_2\text{O}_3$ , creating a robust passivation stack.[14][15]

[Click to download full resolution via product page](#)

Caption: A typical experimental workflow for Si-28 surface passivation.

## Category 3: Lithography and Etching

Question: I'm seeing pattern defects and inconsistencies after lithography. What are the common causes?

Answer: Lithography is a highly precise process where even small variations can introduce yield-killing defects.<sup>[16]</sup> Issues can arise from the photoresist, the mask (reticle), or the exposure tool (scanner).<sup>[16]</sup>

- Photoresist Issues: Inconsistent photoresist thickness, often caused by changes in viscosity or improper spin coating, can lead to patterning errors.<sup>[16][17]</sup> Incomplete solvent removal during the prebake step can also affect photosensitivity.<sup>[18]</sup>

- Mask/Reticle Defects: Dust particles or damage on the mask will be directly transferred to the wafer pattern.[16] A defect on a single-pattern mask can be catastrophic as it will be repeated across the entire wafer.[16]

- Alignment Errors: Each layer must be precisely aligned with the previous ones. Misalignments in the x, y, or rotational directions can cause device failure, especially with the small feature sizes in modern fabrication.[16]

- Process Variations: Fluctuations in temperature, pressure, and chemical concentrations during any step of the lithography process can impact the final result.[1]

Question: My etch process is non-uniform and is damaging the silicon. How can I optimize it?

Answer: Etching translates the lithographic pattern into the silicon substrate, and control is paramount. Both wet and dry etching present unique challenges.

- Wet Etching: While highly selective, wet etching with acids is isotropic, meaning it etches in all directions at the same rate.[19] This can lead to "undercutting" of the photoresist mask, which degrades resolution and is a significant issue for small features.[19] The effectiveness can also depend heavily on operator skill and control of the chemical bath.[19]

- Dry Etching (e.g., Reactive Ion Etching - RIE): Dry etching offers much better directional (anisotropic) control, but the plasma process can physically damage the silicon lattice.[19] It can also leave behind residual impurities on the substrate surface.[19] A post-etch cleaning step, potentially involving an oxygen or hydrogen plasma followed by a wet acid clean, is often necessary to remove this damage and residue.[19]

Table 2: Troubleshooting Common Etching Problems

| Issue                             | Potential Cause(s)                                                         | Recommended Action(s)                                                                                                                                             |

|-----------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Undercutting (Wet Etch)           | Isotropic nature of chemical etch.                                         | Switch to a dry etch process (e.g., RIE) for better anisotropic control, especially for features $< 5\mu\text{m}$ . <sup>[19]</sup>                               |

| Non-Uniform Etch Rate             | Inconsistent fresh etchant supply (wet); non-uniform plasma density (dry). | Agitate the wet etch bath; optimize gas flow, pressure, and RF power in the RIE chamber.                                                                          |

| Surface Damage/Residue (Dry Etch) | High-energy ion bombardment from plasma.                                   | Optimize RIE parameters (lower power, adjust gas chemistry). Implement a post-etch cleaning and annealing step to remove damage and contaminants. <sup>[19]</sup> |

| Resist Mask Degradation           | Etchant is too aggressive for the resist; overheating during dry etch.     | Use a hard mask (e.g., $\text{SiO}_2$ or $\text{Si}_3\text{N}_4$ ) for harsh etches. <sup>[17]</sup> Improve wafer cooling during the dry etch process.           |

## Category 4: Annealing and Thermal Processing

Question: How does the annealing process affect device performance and yield?

Answer: Annealing is a critical thermal processing step used for multiple purposes in device fabrication, including dopant activation, defect curing, and improving material interfaces. In the context of quantum devices, quantum annealing is a specialized approach that uses quantum fluctuations to find the optimal solution to a problem, which is encoded in the final state of the system.<sup>[20][21]</sup>

For conventional device fabrication, thermal annealing must be carefully controlled:

- Defect Interactions: Heat treatments can cause impurities like oxygen to cluster, forming complexes that can act as unintended donors.<sup>[10]</sup> Contamination from metals (Cu, Au, Fe)

can also occur during these high-temperature steps.[7][10]

- Process Stability: Passivation layers must be thermally stable to withstand subsequent high-temperature steps in the fabrication flow.[15] For instance, an oxide/nitride stack can offer enhanced thermal stability compared to a single nitride layer.[15]

For quantum annealing applications, the process is different:

- The system of qubits is initialized in a simple ground state and slowly evolved to a final configuration that represents the solution to a complex optimization problem.[20]

- The process is sensitive to noise and decoherence, which can lead to inaccuracies in the final result.[20]

[Click to download full resolution via product page](#)

Caption: Logical flow of how root causes lead to low device yield.

## Frequently Asked Questions (FAQs)

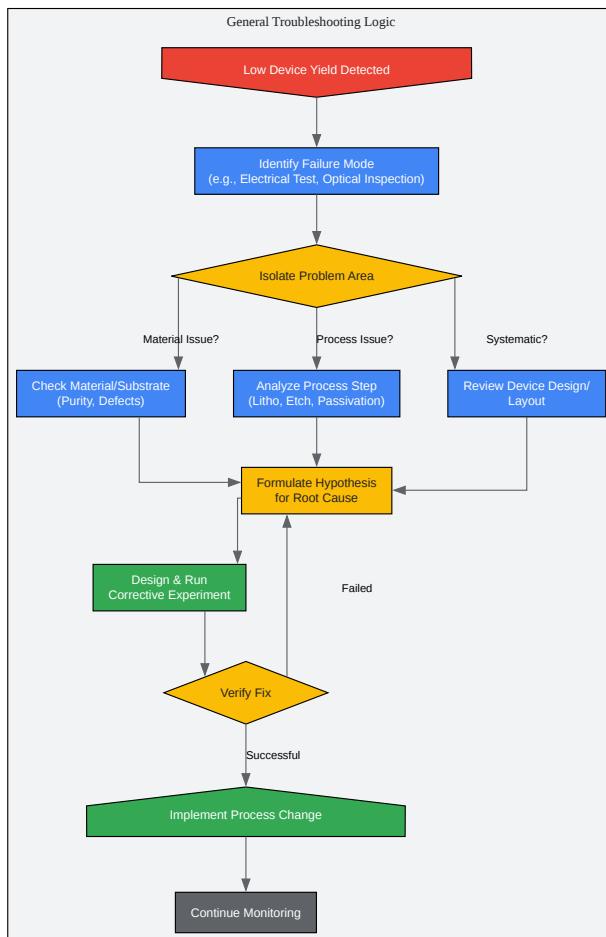

Q1: What is a typical "good" yield for a mature semiconductor fabrication process? A1: There is no single typical value, as yield is highly dependent on many variables, including the process node, die size, and product complexity.[\[22\]](#) For a very small die on a mature process, yields can be very high. However, for a large die on a new, advanced process node (like 28nm or below), initial yields might be much lower and require significant effort to ramp up.[\[22\]](#)[\[23\]](#)[\[24\]](#)

Q2: Why is Silicon-28 preferred over natural silicon for quantum computing? A2: Natural silicon contains about 92% silicon-28, but also includes roughly 5% of the silicon-29 isotope.[\[4\]](#) Silicon-29 has a nuclear spin that creates magnetic "noise," which can interfere with the fragile quantum states of a qubit, causing decoherence (loss of quantum information).[\[3\]](#)[\[4\]](#) Highly enriched, spin-free Silicon-28 provides a much quieter "spin vacuum" for qubits to operate in, leading to significantly longer coherence times.[\[5\]](#)[\[25\]](#)

Q3: Can a wafer with defects be reworked? A3: In some cases, yes. If defects are caught early in the fabrication process, it may be possible to strip the defective layer and rework that specific process step. While the yield from a reworked lot is typically lower, it can reduce overall costs by salvaging a wafer that would otherwise be a complete financial loss, especially in the later stages of production.[\[16\]](#)

Q4: How do environmental factors impact fabrication yield? A4: The fabrication environment is critically important. Cleanroom air quality must be tightly controlled to prevent airborne particles from landing on the wafer, which can cause defects during lithography or deposition.[\[2\]](#)[\[16\]](#) Additionally, factors like temperature, humidity, and even vibrations can affect the precision of manufacturing equipment and the consistency of chemical processes, ultimately impacting yield.[\[1\]](#)[\[2\]](#)

Q5: What is the difference between random and systematic defects? A5: Random defects, like those caused by a random dust particle, are unpredictable and distributed randomly across a wafer.[\[26\]](#) Systematic defects are recurring and often related to a specific aspect of the process, design, or layout.[\[24\]](#) For example, a particular layout pattern might be difficult to manufacture consistently, leading to the same defect on every chip.[\[24\]](#) At advanced nodes, systematic defects have become the dominant concern and require aggressive yield management strategies to identify and eliminate.[\[24\]](#)

[Click to download full resolution via product page](#)

Caption: A high-level workflow for troubleshooting low yield issues.

#### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. The Many Ways In Which Semiconductor Yield Can Be Impacted - #chetanpatil - Chetan Arvind Patil [chetanpatil.in]

- 2. youtube.com [youtube.com]

- 3. ASP Isotopes Inc. Commences Commercial Production of Enriched Silicon-28 at its Second Aerodynamic Separation Process (ASP) Enrichment Facility :: ASP Isotopes Inc. (ASPI) [ir.aspisotopes.com]

- 4. Spotlight: Silicon-28 in Quantum Computers | NIST [nist.gov]

- 5. briandcolwell.com [briandcolwell.com]

- 6. chem.libretexts.org [chem.libretexts.org]

- 7. researchgate.net [researchgate.net]

- 8. universitywafer.com [universitywafer.com]

- 9. waferpro.com [waferpro.com]

- 10. www2.irb.hr [www2.irb.hr]

- 11. pubs.aip.org [pubs.aip.org]

- 12. Surface passivation as a cornerstone of modern semiconductor technology – Highlighting a comprehensive review paper on surface passivation for silicon, germanium, and III–V materials – Atomic Limits [atomiclimits.com]

- 13. silicon surface passivation: Topics by Science.gov [science.gov]

- 14. repo.uni-hannover.de [repo.uni-hannover.de]

- 15. openresearch-repository.anu.edu.au [openresearch-repository.anu.edu.au]

- 16. electronics360.globalspec.com [electronics360.globalspec.com]

- 17. microchemicals.com [microchemicals.com]

- 18. loharanuradha80.medium.com [loharanuradha80.medium.com]

- 19. youtube.com [youtube.com]

- 20. medium.com [medium.com]

- 21. youtube.com [youtube.com]

- 22. quora.com [quora.com]

- 23. researchgate.net [researchgate.net]

- 24. semiengineering.com [semiengineering.com]

- 25. pubs.acs.org [pubs.acs.org]

- 26. Common Mistakes During Silicon Wafer Processing [waferworld.com]

- To cite this document: BenchChem. [troubleshooting low yield in Silicon-28 device fabrication]. BenchChem, [2025]. [Online PDF]. Available at:

[<https://www.benchchem.com/product/b1172460#troubleshooting-low-yield-in-silicon-28-device-fabrication>]

**Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

**Contact**

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)